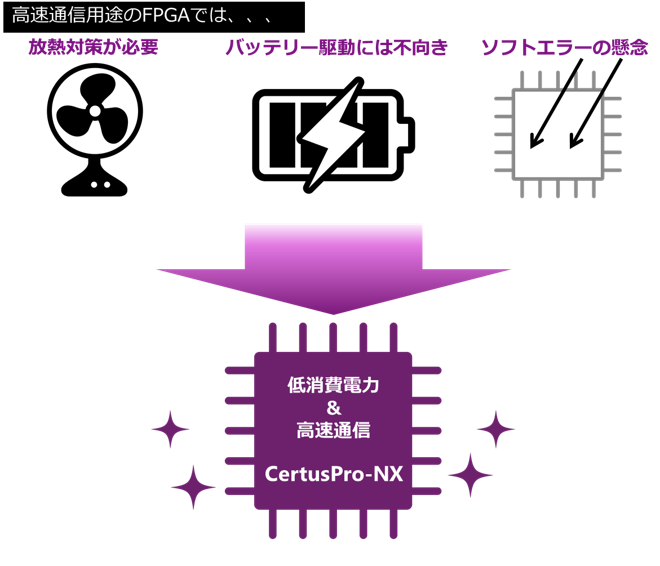

FPGAs, which allow designers to freely change logic circuits, areoften used in product development that requires high-speed communication. On the other hand, engineers commented that "it consumes a lot of power and requires measures to dissipate heat, so the housing of the product becomes large," "it is not suitable for devices that run on batteries," and "soft error countermeasures are time-consuming." is also asked.

For those who have such issues, we will introduce a small-package FPGAthat achieves both low power consumption and high-speed processing.

Flexible circuit design is possible. FPGA for high-speed communication

With the development of data communication technology and video technology,PCIe,CXPMore,SLVS-ECWith the advent of high-speed interface standards, the market is demanding products that can support high-speed communication. again,IoTAs technology spreads,AIEdge that embeds the inference engine in the terminalAIExpectations have risen for Under these circumstances, high-speed processing is possible, circuits can be designed flexibly, and functions can be differentiated.FPGAis used in a wide range of product development.

on the other hand,FPGADisadvantages include power consumption and heat generation. Therefore, medical equipment that comes into contact with the human body, industrial equipment that runs for a long time, and battery-poweredIoTIt has been considered unsuitable for gadgets and mobile devices. This time, Lattice Semiconductor has released a general-purposeFPGA"Certus Pro-NX"teeth,FD-SOIHigh-speed communication, high-speed processing, and low power consumption are achieved by the process. It can also greatly reduce heat generation. so farFPGAIt is possible to expand to products that were difficult to use.

In recent years, it has become mainstreamFinFETsThe process,3DIt consists of transistors (three-dimensional transistors) and features high-speed switching and high integration. However, there are concerns that power consumption will increase as the clock frequency increases, and heat generation per unit area will increase as the degree of integration increases.

On the other hand, FD-SOI (fully depleted silicon-on-insulator) consists of planar transistors using a "buried oxide film" and an "ultra-thin silicon film". The buried oxide film enables efficient electron flow between the source and drain, and the ultra-thin silicon film eliminates the need for transistor ON/OFF control (channel doping). As a result, leakage current can be greatly reduced.

Structure of 3D transistor (three-dimensional transistor)

Structure of a fully depleted transistor

Problems of conventional FPGA are "power consumption", "heat countermeasures" and "soft error countermeasures"

CertusPro-NXis used for the following applications.

<Usage example>

・Used in medical devices such as endoscopes that require video communication. Low power consumption generates little heat and can be safely used in products that come in contact with the human body.

A compact product size can be achieved because heat dissipation components are not required.

・ Adopted for head-mounted displays such as VRandAR, realizing products that can be worn for a long time from the viewpoint of size and heat generation.

・Develop equipment that requires high resolution and high-speed communication, such as industrial machine vision systems.

・Use it for products that do not allow malfunctions due to soft errors, such as production factories, chemical plants, in-vehicle devices, and space-related businesses, to save labor in the development process.

・Combine dedicatedICs such as ASICsfor mobile devicesandFPGAsto develop new products that support next-generation technology in a short period of time.

Conventionally, the following issues have arisen when usingFPGAsin such product development.

Issue (1) Large amount of power consumption

GeneralFPGAconsumes a lot of power, so the battery lasts a long time. In addition, since it generates a lot of heat, it was difficult to use it for products that come into contact with the human body, such as medical equipment and head-mounted displays.

Issue (2) Incorporation of heat dissipation components

Due to the large amount of heat generated by the FPGA, heat dissipation components such as heat sinks and fans are often required. The size of the product housing became large, which was also a factor in increasing the cost.

Issue (3) Measures against soft errors

A typicalFPGAhas an SRAMstructure, and neutron beams derived from cosmic rays cause bit corruption. It took time and effort to take measures against soft errors to prevent unexpected malfunctions.

FD-SOI process adopted. Small FPGA "CertusPro-NX" that can be used for medical equipment, industrial equipment, and IoT equipment

Lattice Semiconductor's advanced general-purposeFPGA"CertusPro-NX" has the following features and is attracting interest from fields where FPGAshave not been actively used until now.

Features (1) Approximately 1/4 the power consumption compared to FinFET

FD-SOIBy adopting the process, we have achieved a significant reduction in power consumption.FinFETssame scale by processFPGAcompared to about1/4Reduces power consumption to Since heat generation itself can be greatly suppressed, heat dissipation measures are not required.

Features (2) Offers up to 10.3 Gbps bandwidth, approximately double that of the competition

It uses aSERDES circuit with a maximum of 10.3 Gbps, and achieves approximately doublethe bandwidthcompared toFPGAs of the same scale. It also supports various protocols such asPCIe,CXPandSLVS-EC.

Features (3) Optimal memory configuration for AI implementation

Equipped with about65% more block memory than FPGAs of the same size, it has an optimal configuration forAI implementation. External memory such as LPDDR4can also be connected.

Features (4) Suppresses the soft error rate to about 1/100

Compared to the FinFETprocess, the soft error rate can be suppressed to about 1/100.It is also ideal for industrial robots that operate24 hours a day, as well as products used in plant businesses, in-vehicle devices, and space businesses where malfunctions affect the world.

Feature (5) Reduced package size to less than 1/6

Certus Pro-NXThe package of9mm square, area81It is as small as a square centimeter. Same size as other companiesFPGAthen529While some products are square centimeters, approximately1/6The following package sizes have been realized. camera orIoTIt is also ideal for products that require a compact housing, such as equipment.

Product Specifications

|

Features |

CPNX-50K*1 |

CPNX-100K |

|

|

Logic Cells |

53K |

96K |

|

|

EBR |

1.7Mb |

3.7Mb |

|

|

Large RAM |

2Mb |

3.6Mb |

|

|

DSP (18 × 18 Mults) |

96 |

156 |

|

|

PLLs |

3 |

4 |

|

|

Hard Blocks |

10GE PCS, PCIe Gen3, SGMII CDR, ADC |

||

|

Packing |

I/O (WR + HP + ADC) *2 |

||

|

ASG256 (0.5mm pitch) |

9x9mm |

170 (TBD) ×4 SERDES |

165 (75 + 84 + 6) ×4 SERDES |

|

CBG256 (0.8mm pitch) |

14x14mm |

170 (TBD) ×4 SERDES |

165 (75 + 84 + 6) ×4 SERDES |

|

BBG484 *3 (0.8mm pitch) |

19×19mm |

230 (TBD) ×4 SERDES |

305 (167 + 132 + 6) ×8 SERDES |

|

BFG484 *3 (1.0mm pitch) |

23x23mm |

230 (TBD) ×4 SERDES |

305 (167 + 132 + 6) ×8 SERDES |

|

LFG672 (1.0mm pitch) |

27×27mm |

305 (167 + 132 + 6) ×8 SERDES |

|

*1: CPNX-50K information is preliminary

*2: WR: Wide-Range I/O, HP: High-Performance I/O, ADC: Dedicated ADC inputs

*3: SERDES speed limited to 6.25 Gbps in BBG484 and 5.5 Gbps in BFG484