Introduction

hello! I'm Nami.

Last time Stratix ® I wrote an article about Hyper-Register to realize a new mechanism called HyperFlexTM of 10 FPGA.

This is the continuation of that.

Just in case, review Hyper-xx...

・Hyper Flex

Introduced in Stratix 10 Mechanisms to Increase FPGA Performance the whole thing

・Hyper-Retiming, Hyper-Pipelining, Hyper-Optimization, etc.

work to actually improve performance function

・Hyper-Register

Registers introduced from Stratix 10 to achieve above functionality

This time it is one of the functions Hyper-Retiming I will write about!

If you haven't read the previous article yet, by all means

[Stratix 10 New Feature ~ Mystery of Hyper-XX (What is Hyper-register?) ~]

Please read this before continuing with this article.

About conventional retiming function before talking about Hyper-Retiming.

What is Retiming?

What is retiming Improves performance by balancing delays between ALM registers and eliminating critical paths Quartus ® It's a feature of Prime.

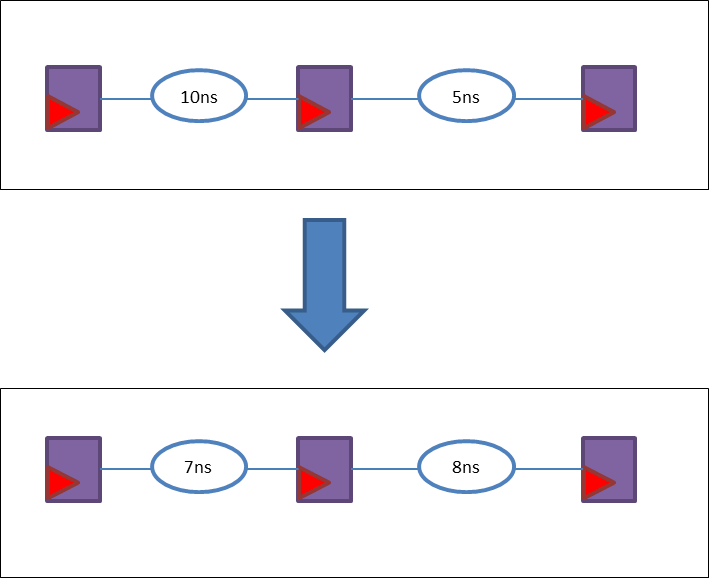

By moving the registers without changing the logic function as shown in Fig. 1, the delay of paths that do not meet the timing can be reduced.

In addition, if the wiring delay is long, it also moves registers to shorten the delay.

【example】

Let's say we want to run FPGA at 300MHz (3.3ns).

In that case, data must propagate between ALM registers within 3.3ns.

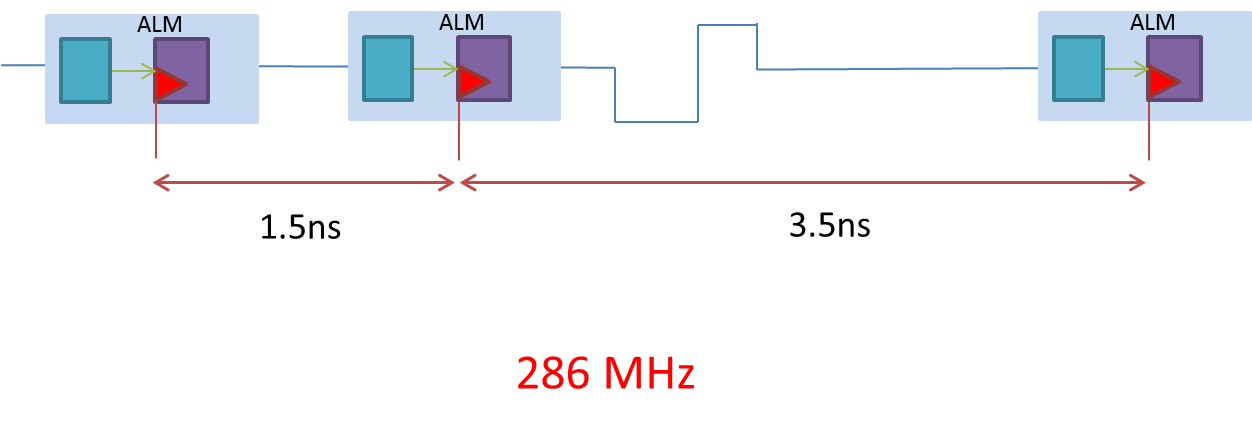

Suppose now that the ALM is connected as shown in Figure 2.

The delay between each register is 1.5ns and 3.5ns.

In this state, a delay of 3.5ns occurs and the operating frequency is 286MHz, which does not satisfy the desired operating frequency (300MHz).

Use the Retiming function at times like this!

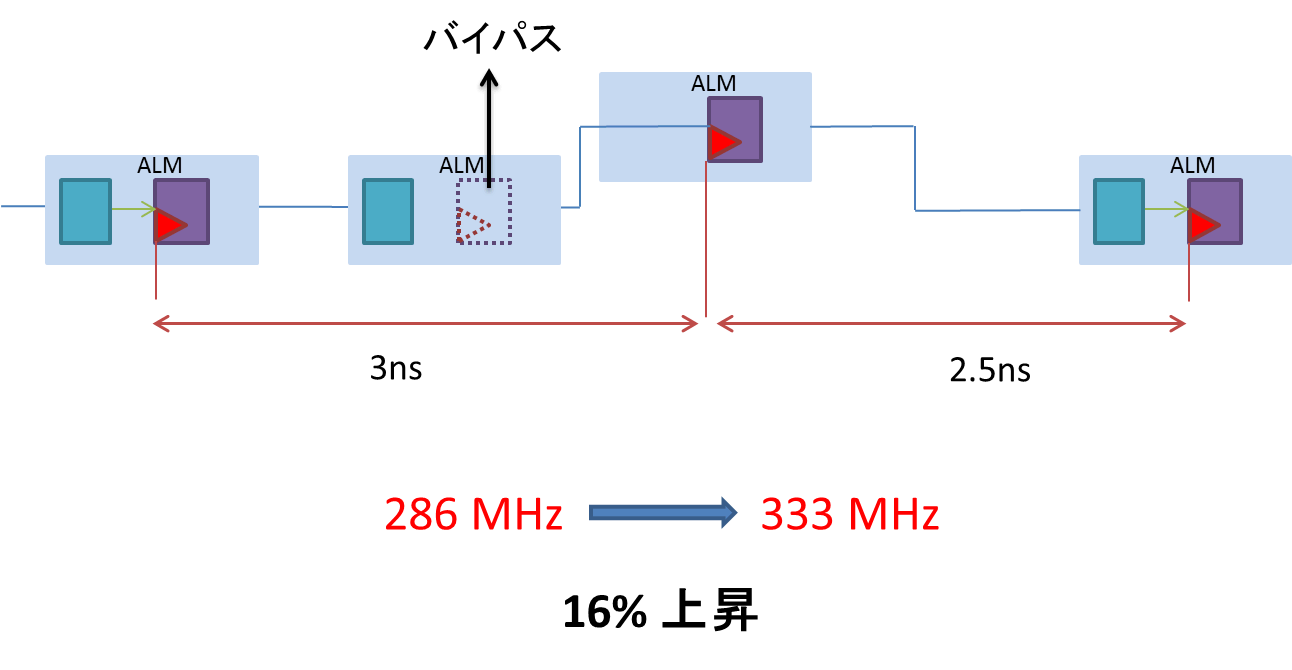

Specifically, it takes advantage of unused ALM registers in locations where critical paths can be optimized to improve timing.

In this way, it adjusts to meet the desired operating frequency (Fig. 3).

In the example above, we were able to improve the timing, but if the resource utilization is high and many ALMs are already in use, the timing may not be improved.

Also, I think there is a desire to raise the operating frequency.

That's where Hyper-Retiming using Hyper-Registers finally comes in!

What is Hyper-Retiming?

What is Hyper-Retiming?

Eliminate critical paths by balancing routing delays between registers using Hyper-Registers

Ability to improve operating frequency (performance) is.

There are two methods of Hyper-Retiming.

[1] Improve performance by changing only register placement

[2] Improve performance by changing the order of combinational circuits and registers

[1] Improve performance by changing only register placement

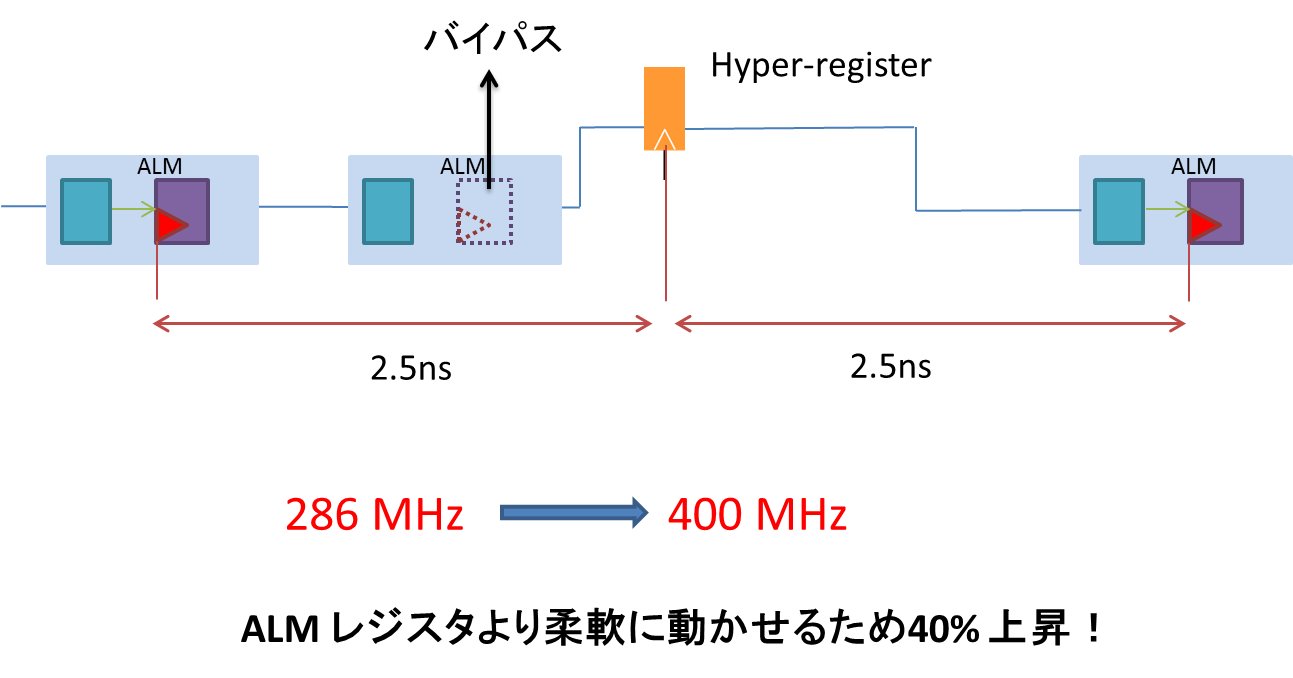

Using Hyper-Registers, it looks like Figure 4.

Unlike the previous one, we use Hyper-Registers on the wiring.

As a result, with the conventional Retiming, it was 333MHz after the improvement, but with Hyper-Retiming, it became possible to run even at 400MHz!

As I wrote in the previous article, Hyper-Registers are very abundantly arranged, so you can use Hyper-Registers in just the right positions.

That's why the timing improvement rate is higher than before!

Furthermore, Hyper-Registers are located separately from ALM registers, so retiming is possible even if all ALMs are used!

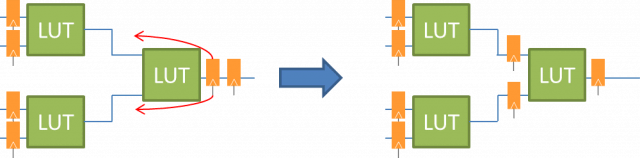

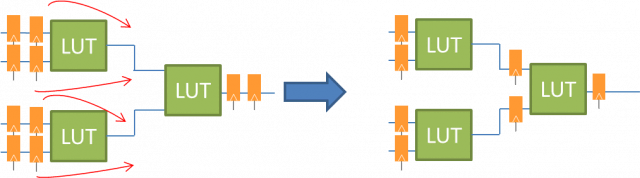

[2] Improve performance by changing the order of combinational circuits and registers

The Hyper-Retiming feature may also improve performance by reordering combinatorial circuits and registers.

For example, if the LUT two-stage part fails to meet timing, moving the registers between the two LUTs improves performance.

Backward Retiming is to move registers upstream in logic by retiming, and Forward Retiming is to move registers downstream.

The advantage of this feature is that it improves performance while maintaining functionality.

As shown in Figures 5 and 6, the delay is reduced by moving the registers before and after the combinatorial circuit.

Hyper-Register works with such flexibility!

However, there is a caveat to such a Hyper-Register.

Precautions when using Hyper-Retiming

Hyper-Retiming is convenient, but there are some things you should be aware of when using it.

For example, when using asynchronous clear, retiming may not be possible or the initial value may not be maintained.

Therefore, we have summarized the cases where Hyper-Retiming is not enabled.

Locations that cannot be retimed

・Register with asynchronous clear

・Synchronizer chain

・Boundary register with I/O (virtual pin setting is the same)

・Paths between asynchronous clock domains

- The register specified as the destination in the SDC constraint

・Registers declared with Synth hesis attribute “preserve”

・RAM/DSPs block

・Latch

For details, please refer to the "Facilitate Register Movement (Hyper-Retiming)" section of the document below.

Even if the Hyper-Register is not enabled and performance improvement is not obtained, Quartus Prime can check what is the bottleneck above, so you can take countermeasures!

Stratix 10 High-Performance Design Handbook:

Also, if you want to learn more about Hyper–xx, please see here.

Summary

Advantages of Hyper-Retiming

1. Timing improvement rate is high because placement is more flexible than ALM registers

2. Enables timing improvements independent of ALM utilization

The rest of the features I plan to write about in the article are

・Hyper-pipelining

・Hyper-Optimization

is.

next time "Hyper-Pipelining" will be introduced.

looking forward to!