hello.

My name is Hanako Altera and I provide technical support for Altera® FPGA products at Macnica.

If you are a hardware engineer or system engineer in this era, you have probably heard of a semiconductor device called FPGA (FPGA) at least once. FPGAs are familiar to us, but any product will always have a “first-timer”. People who say "I'm going to start FPGA from now on!" still need study, knowledge, and information research.

The theme is "What is an FPGA?", but I won't write the general basic knowledge of FPGA here! A web search for “what is an FPGA” now yields a wealth of information. So I'll leave the general basic knowledge to you... Here, I would like to send out a little more broken information.

(By the way, I'll just write this down.)

In a nutshell, FPGAs are "logic devices whose circuits can be rewritten later."

The word FPGA is an acronym for Field Programmable Gate Array. It means semi-custom LSI ].

by the way,

CPLD is a non-volatile IC whose etymology is Complex Programmable Logic Device.

Both are attractive because they are programmable.

How big is your device?

In short, the range is huge. With such a wide variety of devices available, developers can purchase devices of the appropriate size (capacity) and keep their budget low.

Before we give specific numbers for device scale, let's talk a bit about units of scale.

FPGAs have a unit of measurement to express the size (capacity) of the device, and users use this as a guide when selecting a device. Currently, this unit is not standardized among manufacturers. For example, Altera® FPGAs call it logic element (LE), while Xilinx calls it logic cell (LC), and lattice indicates the number of LUTs (look up tables) it has. Incidentally, an LUT is the core part of the logic circuit block of an LE or LC. (For more information, do a web search. There is a lot of information available.)

Although the basic principle of LUT is the same among FPGA manufacturers, the number of LEs and LCs is not equal because the details of the structure are slightly different. I can't strictly compare LE and LC, but roughly speaking, they are almost equal, so I think you can use it as a guideline.

Now let's get back to it.

In Altera® FPGAs, the smallest one has 40 LEs, and the largest one has 5,510K LEs (as of October 2015). When converted to ASIC gates, 1 LE is about 12 gates.

that's why

5,510 KLE x about 12 = 66,120K gate equivalent

is estimated.

But actually, this is not the logic circuit scale that FPGA can realize! FPGAs now have a variety of blocks such as DSP (multiplier) blocks, memory, PLL, transceiver, ARM, etc. in addition to LE, so it is difficult to simply convert it to gates. Well, as a minimum guideline, I think it is good to estimate by adding up the number of LEs and the maximum number of 18x18-bit multipliers.

The 5,510K LE FPGA in the previous example has 3,960 18x18-bit multipliers.

An 18x18-bit multiplier translates as about 5,000 gates,

3,960 x about 5,000 = 19,800K gate equivalent

Since LE is about 66,120K gates, the model number of this FPGA is converted in terms of ASIC gates,

66,120K + 19,800K = 85,920K gates equivalent

It can be estimated that:

It also has built-in memory, PLL, transceiver, etc. as dedicated blocks,

Equivalent to 85,920K gates + α

This means that.

Internal memory (except for MAX® II and MAX® V) ranges from a minimum of 108Kbit to a maximum of 1,677,312bit.

User I/O pins range from as few as 27 pins (36-pin VBGA package) to as many as 1,640 pins (2,912-pin FBGA package).

The lineup varies depending on the FPGA series, so please check the manufacturer's handbook, or data sheet. (This information is current as of October 2015. Product information before release may be subject to change.)

When actually designing a circuit, it is almost impossible to use 100% of the capacity (resource) of the target device. If all blocks are used to the fullest extent, the wiring that connects each block will be congested, making it impossible to achieve the desired device speed or, in the worst case, placing and routing may not be possible. Also, if there are no unused resources, it will be difficult to respond to circuit (specification) changes. For flexibility, it is recommended to select a logic circuit with a capacity that keeps the utilization rate of the device capacity (resource) to about 80% or less.

[Related Article] Product Specifications: Altera® FPGA

What is the operating speed?

The internal operating speed of an FPGA can reach about 200MHz if the resources used by the logic circuit are reduced to 80% or less and the clock control method for transferring data inside the FPGA is configured to be synchronous (flip-flops operate on the same clock). Of course, this also depends on how the user creates the circuit, so it may not even be possible to achieve 100MHz. In other words, the internal operating speed of an FPGA depends on the design and configuration of the user's logic circuit.

When you hear 200MHz, you may think that it is slow for software designers, but since FPGA is hardware, parallel processing is easy! In addition, since the hardware part can be created freely, it is possible to further increase the processing capacity (throughput) by devising a method for processing data.

The external operating speed of FPGAs is supported by many interfaces such as DDR3/DDR4 SDRAM, PCI Express (PCIe), Serial RapidIO, and Gigabit Ethernet, as they have internal transceiver blocks and support a wide variety of I/O standards. The latest FPGAs achieve data transfer speeds of up to 28Gbps. (This information is current as of October 2015. Product information prior to release may be subject to change.)

What are the development costs?

Developing an FPGA or CPLD roughly costs something like this.

| development cost | For FPGAs and CPLDs... |

| Labor costs required for design and verification | ⇒ 自社で開発すれば、人件費は抑えられます。 |

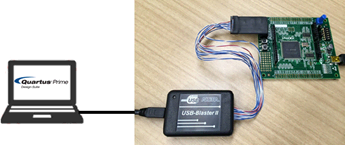

| Development environment (software) | ⇒ Use Quartus® Prime Lite Edition for 0 yen! |

| device | ⇒ Inexpensive ones can be purchased from the 100 yen range. |

| Mask and wafer manufacturing costs | ⇒ Not required. |

| Board design, device mounting | ⇒ The cost will vary depending on what kind of board specifications you use and whether you outsource or do it in-house. |

| write data | ⇒ You write the data yourself. In other words, the writing work costs 0 yen. However, if you do not have an Altera® FPGA download cable for writing, you will need to purchase one. |

| Design change of logic circuit | ⇒ (If you design it yourself) you can change it on the spot. (Because it's your own work) There is no additional cost. |

[Additional information regarding data writing]

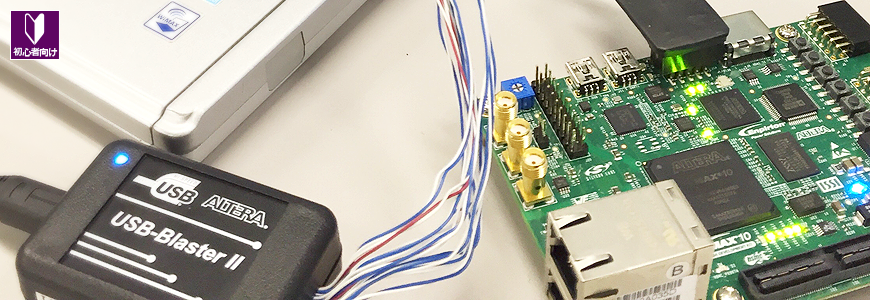

The FPGA is written while mounted on the board. The FPGA has a dedicated pin for writing, and the connector on the board is wired to the dedicated pin. A dedicated download cable called USB-Blaster™ II is used to connect the computer to the board (connector). Data is transferred from the computer to the FPGA on the board and written using the Quartus® Prime programming utility (Programmer). However, FPGA is SRAM. In order to commercialize it, it is also necessary to implement non-volatile memory (dedicated ROM or flash memory) on the board to store FPGA data.

What is the minimum purchase unit?

You can purchase from 1 piece!

Therefore, it can be used for any application that suits the user, whether it is for prototyping or for mass production.