FPGAなど多くの半導体デバイスは、複数の電源を必要とします。その際に、電源シーケンスを守ることを要求されるため、電源のオン・オフ制御ピンや出力コンデンサーのディスチャージ機能が必要となる場合があります。

今回は、LDOを使用した場合の注意点4つに絞って、説明致します。

An on/off function is essential for creating a sequence

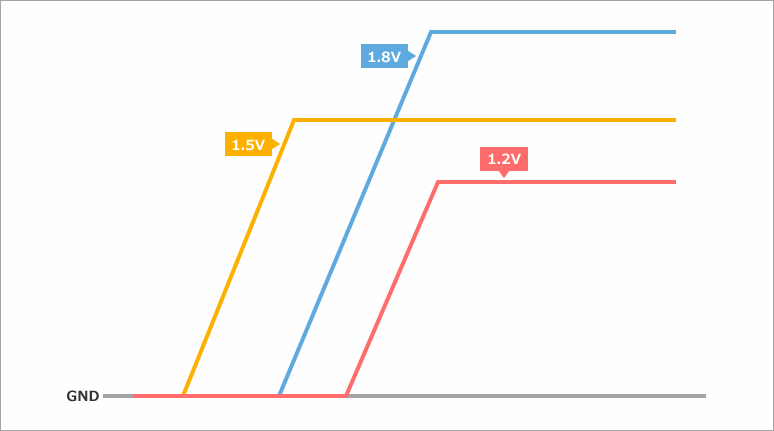

最近のFPGAやDSPは、電源のオン・オフシーケンスを要求することが一般的です。オン・オフを制御するためには、電源IC(モジュール)にオン・オフ制御用のイネーブルピンが必要になります。安価なLDOには、オン・オフ制御用のピンが無い場合があるので選定には注意が必要です。

Rise time control

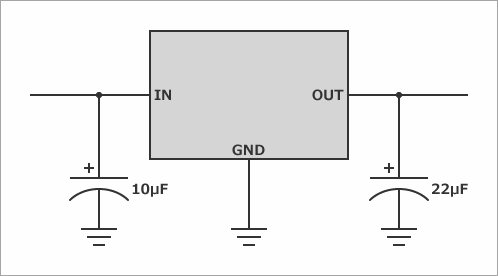

ソフトスタート機能があれば、立ち上がり時間の制御をおこなうことができます。しかし、LDOでソフトスタートの機能を持っている製品は少ないです。対策としては、出力のコンデンサーの容量で立ち上がり時間を制御する必要がでてきます。ただし、あまり大きなコンデンサーを付けてしまうと立ち下げ時に問題を引き起こしてしまいます。

Power down sequence

立ち上げシーケンスの規定は、よく知られています。しかし、立ち下げシーケンスに関してはあまり今まで注意されていませんでした。最近は、基板上に搭載される電源数も多く、立ち下り時のシーケンスも十分注意しないとラッシュカレントを流してしまうケースがあるため、立ち下げシーケンスも十分注意することが重要です。

シーケンスが必要な理由は、こちらの記事を参考にしてください。

電源シーケンスは必要ない?

立ち上がりシーケンスのため、LDOの出力コンデンサーを大きくして調整すると、立ち上げ時間を長くする観点では良いのですが、立ち下げの時間が長くなるため(コンデンサーの放電時間が長くなる)、立ち下げシーケンスに対して不利になるので注意が必要です。

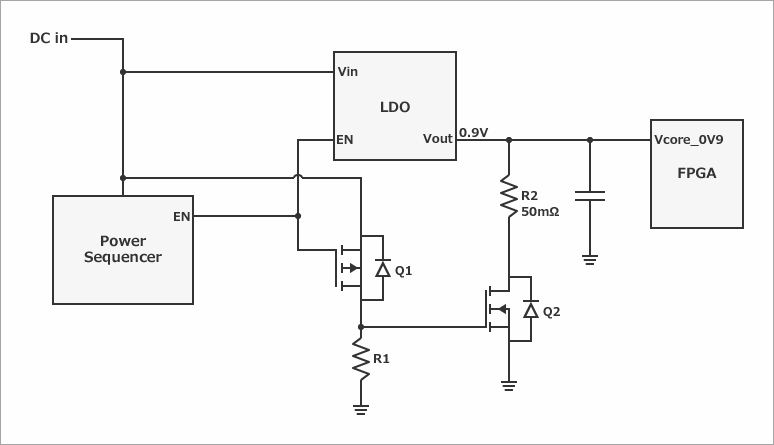

LDO fall sequence

スイッチングレギュレーターは、Low SideのFETがOff時にディスチャージしてくれる場合、出力電圧が直ぐに落ちてくれるので、オフシーケンスも簡単に組めることもあります。しかし、LDOの出力側のディスチャージ機能は無いものがほとんどです。

そのため、出力コンデンサーを大きくすることによる、立ち上げシーケンス制御はお勧めできません。仮に必須になった際は、外付けにディスチャージ用の回路を追加する必要があります。

LDO with on/off function and discharge function

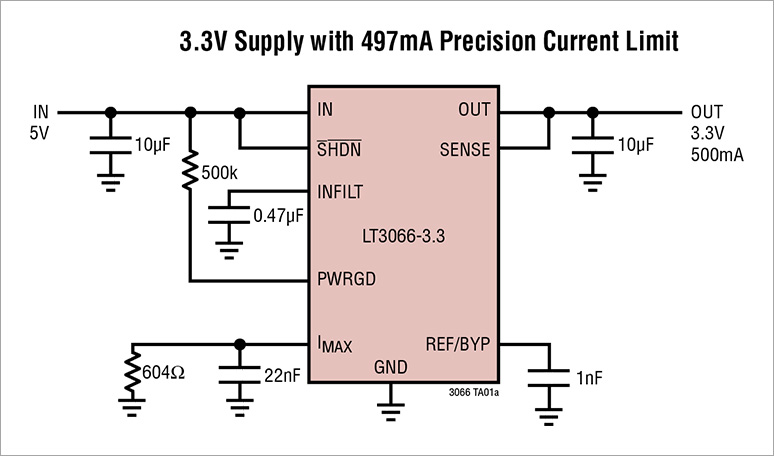

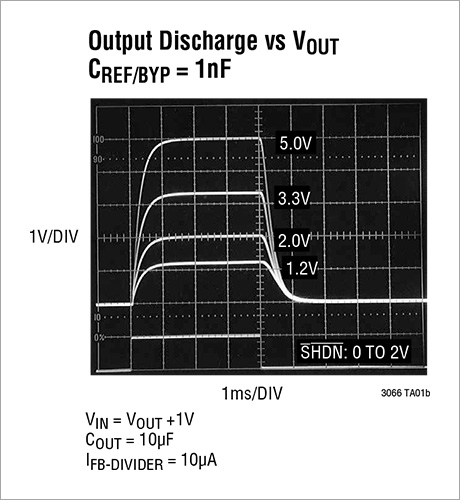

Analog Devices LDOs have an LDO like the LT3066 that has an on/off function (SHDN PIN in Figure 4) and a function to discharge the charge on the output section.

Figure 5 shows the waveform where the output voltage is quickly reduced to 0V due to the output discharge function.

This functionality allows for the FPGA to perform the required power-down sequence while simultaneously supplying clean voltage to the PLL and analog power supply via LDO products.

Click here to purchase products

Inquiry

If you have any questions regarding this article, please contact us below.

Analog Devices Manufacturer Information Top

Analog Devices Manufacturer Information If you would like to return to the top page, please click below.