Microchip FPGA: 最適化のため配置配線を複数回行うオプションはありますか? 結果はどこで見れますか?

<オプション設定の場所>

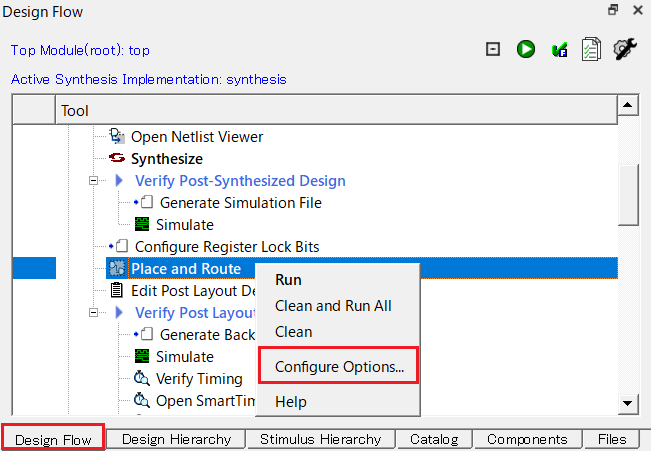

(1) "Place and Route"を右クリック、"Configure Options..."を選択

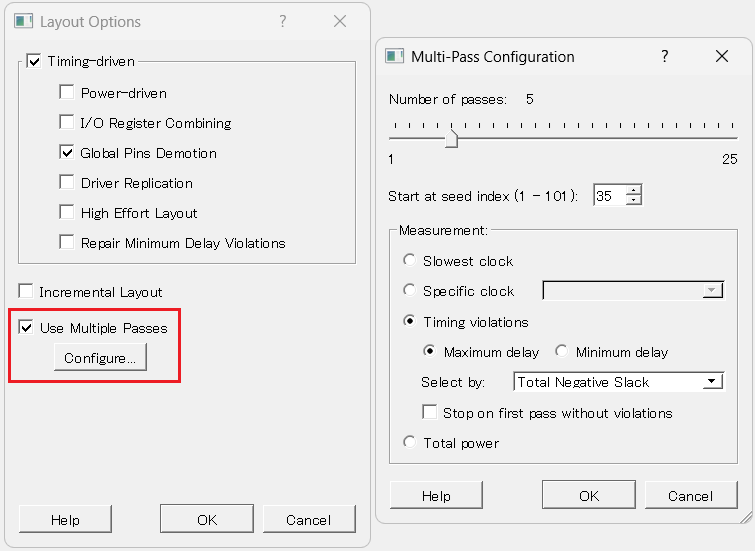

(2) "Use Multiple Passes"にチェックを入れるとオプションを有効化できます。

(3) "Configure…"ボタンを選択し、Multi-Pass Configurationウィンドウにて下記を設定可能です。

Number of passes: 1~25で設定可能、5がデフォルト

Start at seed index(1-101): 1-101で設定可能

Measurement: レイアウト結果を比較する基準を選択

<結果>

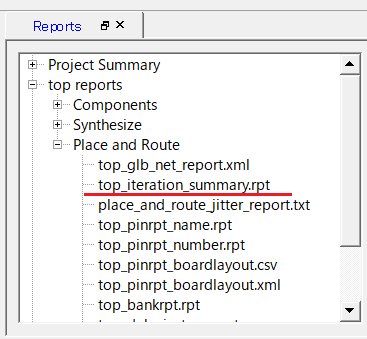

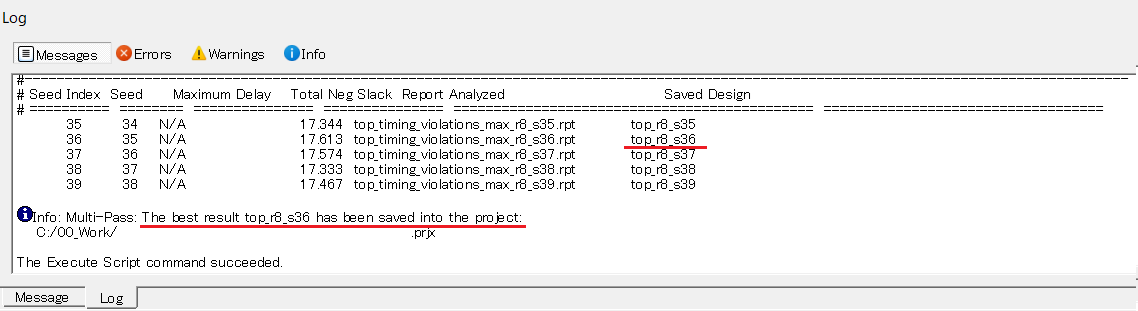

Libero SoC下部のLog、もしくはReport > Place and Route > top_iteration_summary.rptをご確認ください。

Logにてbest resultと記載された配置配線結果が保存されます。

Info: Multi-Pass: The best result xxxxx has been saved into the project:

C:/xxx/xxxx/xxxx.prjx

※ 詳細については「Libero SoC Design Flow User Guide」の「Multiple Pass Layout Configuration」の項目をご参考ください。

「Libero SoC Design Flow User Guide」は Documentation > User Guidesタブ内から参照できます。

https://www.microchip.com/en-us/products/fpgas-and-plds/fpga-and-soc-design-tools/fpga/libero-software-later-versions#Documentation

※ デザインはベストケースのみ保存されます。

引用「Note: There is no option to save the design files from all the passes. Only the (Timing or Power) result reports from all the passes are saved.」

https://onlinedocs.microchip.com/oxy/GUID-AFCB5DCC-964F-4BE7-AA46-C756FA87ED7B-en-US-16/GUID-15AAF951-BC04-4E80-9C4E-7EFD7F5F8FA6.html