Microchip FPGA: Libero SoCにてDDR3やDDR4はどのようにピンアサインしたらいいですか?

はじめに、DDR3やDDR4はピンアサインできる選択肢が決まっています。

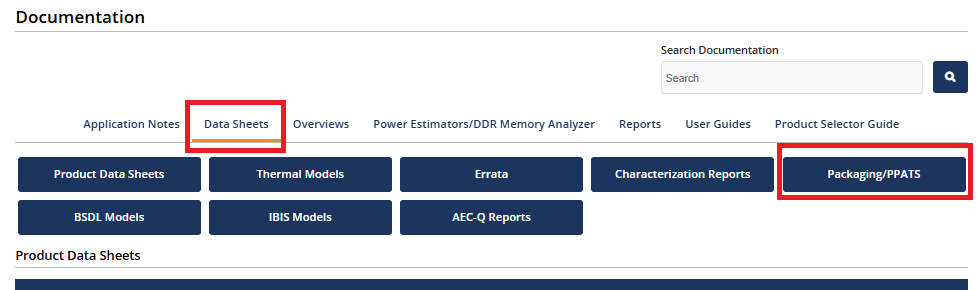

Documentation > Data Sheetタブ > Packaging/PPATS

より

使用される型番に応じた Package Pin Assignment Tableをダウンロードしてください。

https://www.microchip.com/en-us/products/fpgas-and-plds/fpgas/polarfire-fpgas/polarfire-mid-range-fpgas#Documentation

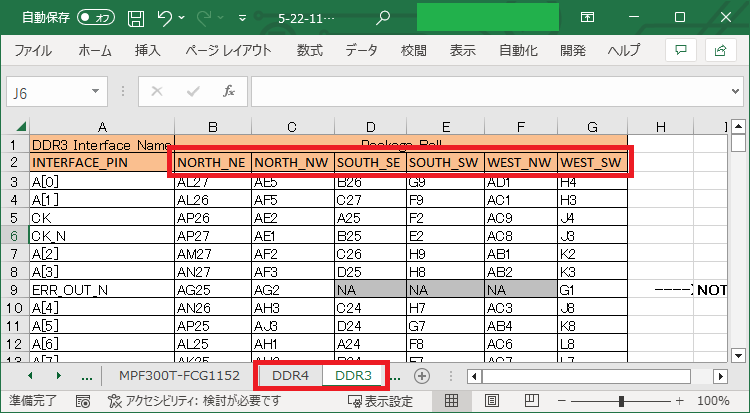

好きなピンに好きな信号をアサインできるわけではないため、

Package Pin Assignment Tableを参考にNORTH_NE、NORTH_NW 等、どこへアサインするかをご検討ください。

※ DQに関しては基板上でビットスワップ可能です。下記FAQを併せてご参照ください。

Microchip FPGA: DQビットスワッピングを際おこなう際Libero SoCでの対応は必要ですか? - 半導体事業 - マクニカ

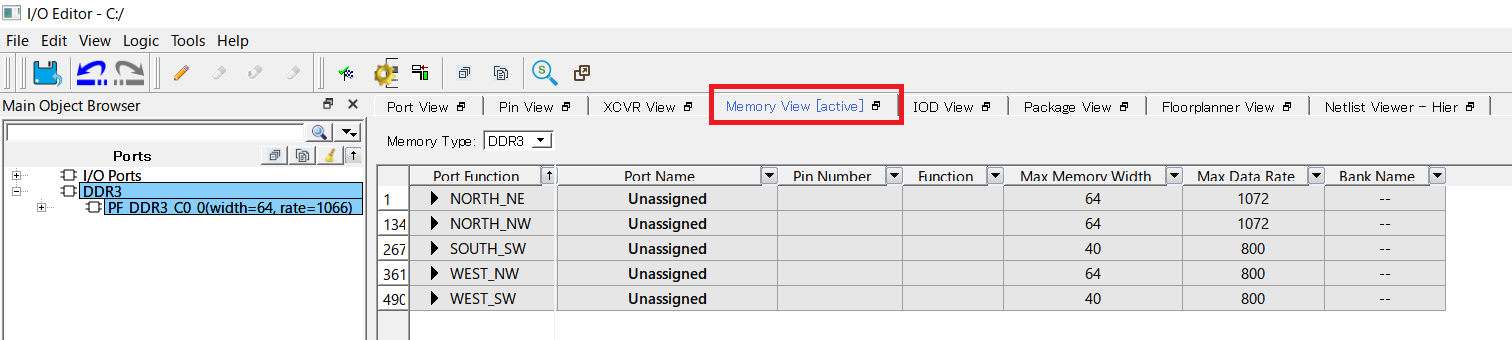

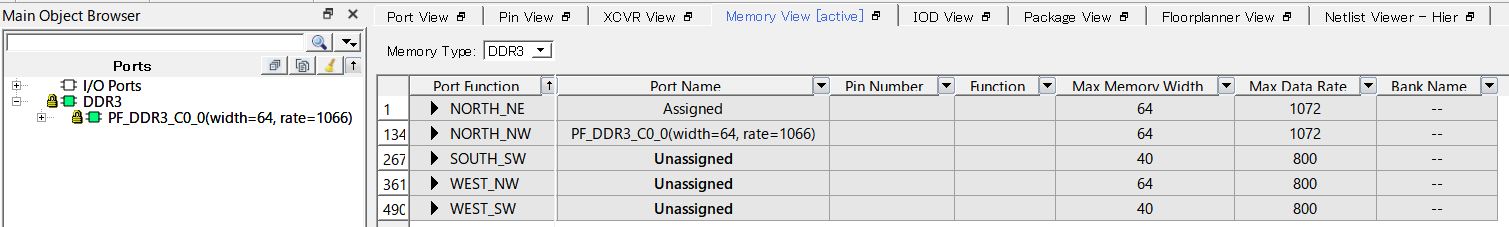

Libero SoCにてI/O Editorを開きます。

DDR3やDDR4をピンアサインする際は、Memory Viewを開きます。

Main Object BrowserにてDDRを選択し、右側の所望の場所(NORTH_NE、NORTH_NW 等)へドラッグ&ドロップすると、一括でDDRがピンアサインされます。

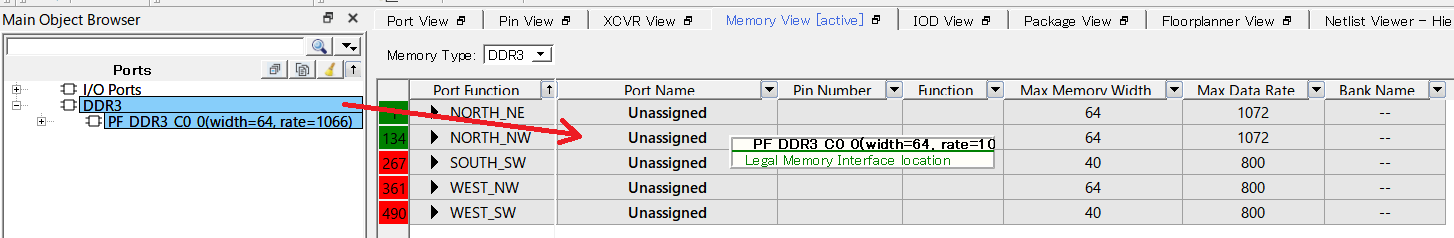

注意 : ピンアサイン可能かどうかはGUI上でドラッグ&ドロップした際に赤色、緑色によって確認できます。

そのため、お客様がpdcを書いてDDRをピンアサインされることはおすすめしません。

ピンアサイン後 :

※ 補足1

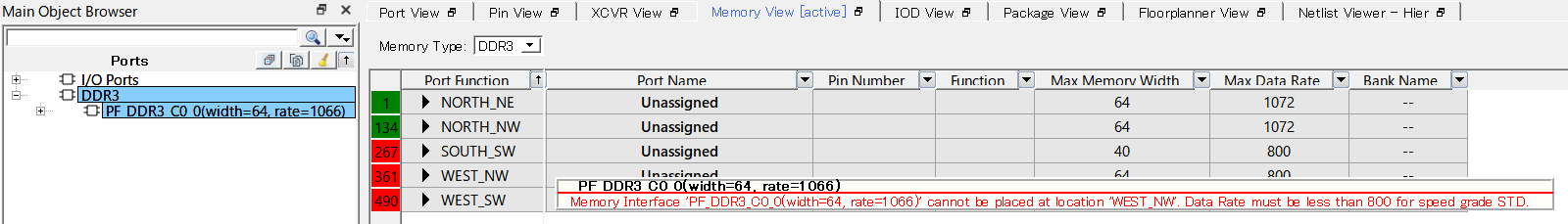

下記のようなData rateについてのメッセージが出る場合、DDRコントローラにてMemory Clock Frequency (Mhz)設定を遅くしてみて、論理合成を実施、

再度ドラッグ&ドロップを試してみてください。

メッセージの一例

「Memory Interface 'PF_DDR3_C0_0(width=64, rate=1066)' cannot be placed at location 'WEST_NW'. Data Rate must be less than 800 for speed grade STD.」

補足2

DDRは他の信号よりも先にピンアサインされることをおすすめします。

一例 :

先にREF_CLKをピンアサインした。

その後DDRを意図した場所に配置できない。(SOUTH_SWにしかアサインできない、等)

対処方法:

一度REF_CLKのピンアサインを外してからDDRのアサインを試してみてください。

その後に、REF_CLKをアサインできるピンの選択肢をIO Editorのプルダウンから探してください。

グレーアウトしていてREF_CLKをプルダウン選択できない場合は、REF_CLKをアサインできるピンのI/O standardとバンクのIO電圧が不一致の可能性があります。

I/O standardを変更してみて、グレーアウトが解除されるか試してみてください。