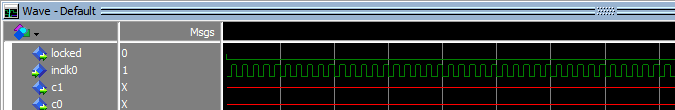

Intel:ALTPLL IP を Questa* - Intel® FPGA Edition で RTL シミュレーションすると、出力クロック (c0 など) の波形が不定になります。なぜですか?

クロック/PLL

シミュレーション

カテゴリー:シミュレーション

ツール:Questa* - Intel® FPGA Edition

デバイス:-

この事象は、ALTPLL IP を VHDL で作成し、Questa* - Intel® FPGA Edition のシミュレーションを手動 (GUI または コマンド) で実行した場合に発生します。

ALTPLL IP のシミュレーション・モデルを正常に実行するには、シミュレーション実行時に指定する分解能を ps (1ps) よりも小さい値・単位にする必要があります。(解像度が高いと計算が四捨五入され、不正確な乗算または除算がおこなわれてしまいます。)

この問題を回避するには、以下で対応してください。

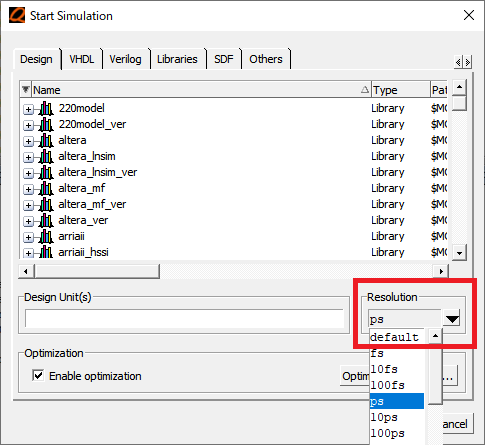

GUI 操作の場合

Start Simulation で実行する際に、

[Design] タブの右下に位置する Resolution を ps よりも小さい値・単位に変更し、シミュレーションを実行してください。

コマンド操作の場合

vsim コマンドに、分解能を指定するオプション -t を追加し、単位を指定してください。

<例: 1ps を指定する>

vsim -t 1ps -L altera_mf …(以下省略)

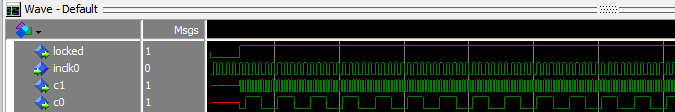

分解能を 1ps より小さい値・単位に指定することで、ALTPLL IP の出力クロック波形が生成されます。

なお、NativeLink シミュレーション で実行している場合は Resolution が 1ps に設定され実行されるため、

この事象は発生しません。