Intel:メモリーを推論させるために配列で記述した HDL コードを MAX® 10 FPGA 向けにコンパイルしたら、メモリーブロックではなくロジック・エレメントに配置されました。

カテゴリー:Tool

ツール:Quartus® Prime Standard Edition、Lite Edition

デバイス:MAX® 10

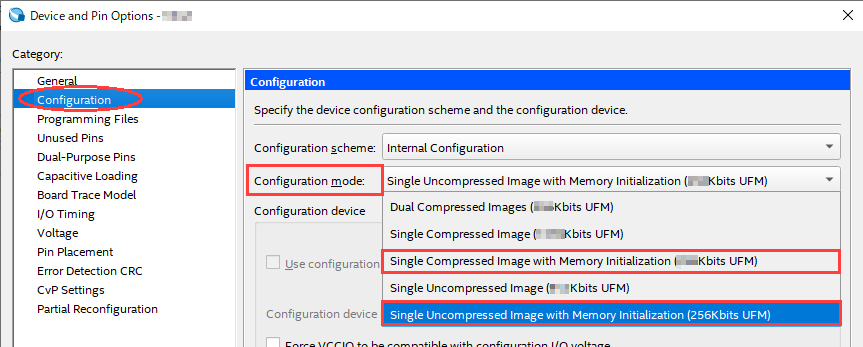

ユーザーが記述した HDL コードの "ROM" または "初期値を持つ RAM" のメモリーを MAX® 10 FPGA のメモリーブロックに配置させるには、Configuration Mode 設定 (Device and Pin Options 内)を 以下のいずれかに指定してください。

・ Single Compressed Image with Memory Initialization

・ Single Uncompressed Image with Memory Initialization

それでもメモリーブロックにアサインされない要因は、ターゲットデバイスのメモリーブロック構造に適さないなど メモリーとして認識されていない可能性があります。

FPGA 内部のメモリーブロックに配置させるには、メモリー IP を使用する方法が推奨されますが、HDL で記述したい場合には下記ドキュメントを参考にしてください。

■ Inferring Memory Functions from HDL Code (「Intel® Quartus® Prime User Guide: Design Recommendations」より)

<Pro Edition>

https://www.intel.com/content/www/us/en/docs/programmable/683082/22-2/inferring-memory-functions-from-hdl-code.html

<Standard Edition>

https://www.intel.com/content/www/us/en/docs/programmable/683323/18-1/inferring-memory-functions-from-hdl-code.html

なお MAX® 10 FPGA のデバイス機能オプションが Compact だった場合は、メモリーブロックに初期値を設定することができません。ご注意ください。

[関連 FAQ]

HDL で作成したデザインが、FPGA のメモリー・ブロックにアサインされません。指定する方法はありますか?

MAX 10 デバイスの Compact は、M9K メモリーに初期値を設定できますか?