はじめに

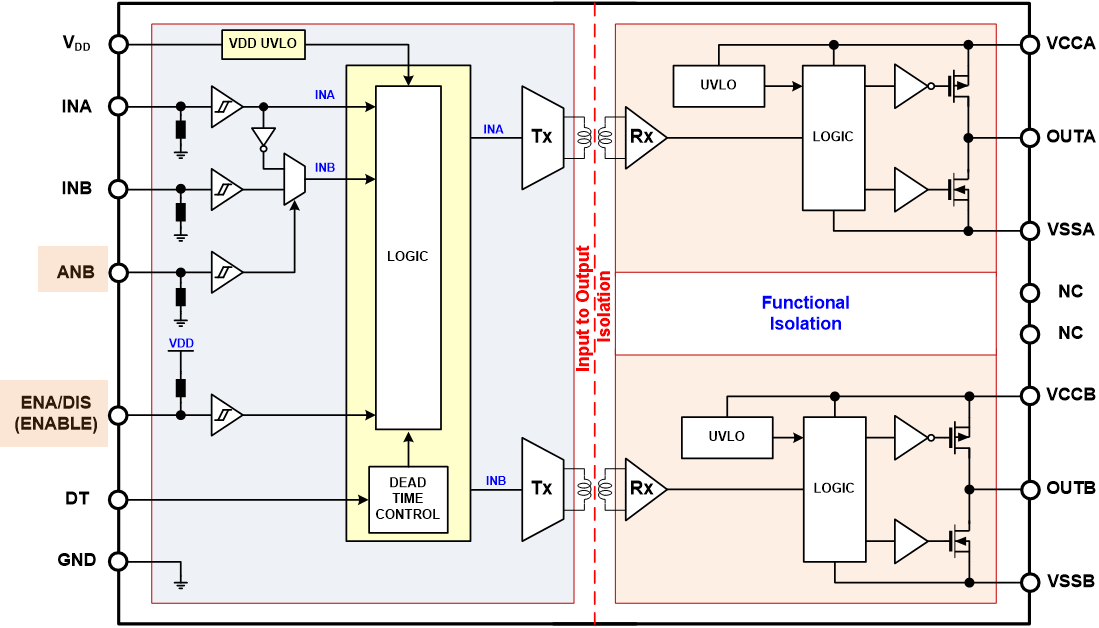

NCP[NCV]51561 は、ソースとシンクのピーク電流がそれぞれ 4.5A/9A の絶縁型デュアルチャンネルのゲートドライバーです。これらは、シリコンMOSFET および SiC MOSFET パワースイッチを駆動するための高速スイッチング用に設計されています。

機能・特長

・4.5A (ソース)/ 9A (シンク)電流

・デュアル ローサイド、デュアル ハイサイド、またはハーフブリッジ ゲートドライバーの制御モードに対応

・各出力ドライバーに独立したUVLO保護

・CMTI(コモンモード過渡耐性)>200V/ns

・伝播遅延 標準 36 ns

- チャネルあたり最大 5 ns の遅延マッチング

- 5 ns の最大パルス幅歪み

・プログラム可能な入力ロジック

- ANB によるシングルまたはデュアル入力モード

- ENABLE または DISABLE モード

・プログラム可能なデッドタイム

・絶縁と安全規格

- 5 kVRMS 絶縁 (UL1577) および出力チャンネル間の1500 Vピーク差動電圧

- 8000 VPK 強化絶縁電圧 (VDE0884-11)

- GB4943.1-2011 による CQC 認証

- IEC 62386-1 に基づく SGS FIMO 認証

・NCV51561は、車載アプリケーション向けAEC-Q100対応

主な特長について

UVLO(低電圧誤作動防止機能)

本製品は、一次側のVDDに対してと、二次側のVCCAとVCCBへの両ゲートドライバー出力に対して、UVLO保護機能を提供します。

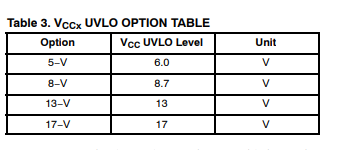

一次側供給電圧3~5Vに対して、UVLOは2.8Vtypです。二次側のVCCAとVCCBのゲートドライバー出力側に対する供給電圧のUVLOついては、下図のTable3に示すとおり、各電圧をオプションで選択可能です。

シリコンMOSFETを駆動する場合と、SiC MOSFETを駆動する場合では、最適なゲート駆動電圧値が異なるため、ゲートドライバーにて駆動する各パワーデバイスの仕様に合わせて、NCP[NCV]51561のUVLOの値を選択できます。

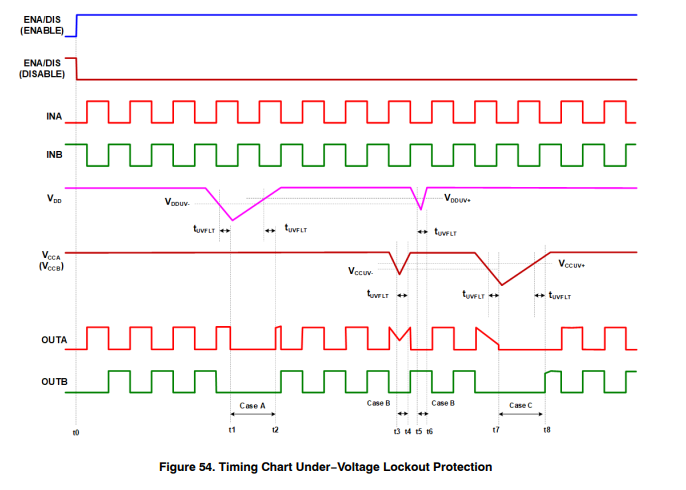

下図Fig.54はUVLO保護時のタイミングチャートを示しています。

ENABLE または DISABLE モード

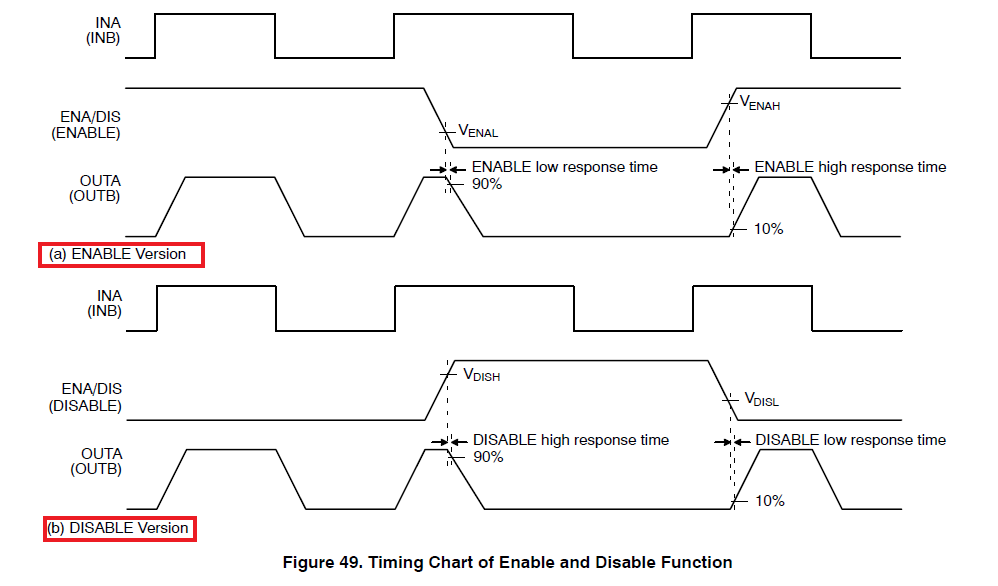

Fig. 49 は、ENABLE または DISABLE 動作モードに応じた応答時間を示しています。

Fig. 49(a)のENABLEバージョンで示すように、ENA/DIS(ENABLE)ピン電圧が LOW 状態になると、両方の出力(OUTA&OUTB)が同時にシャットダウンされ、ENA/DIS(ENABLE)ピンが HIGH (またはオープンのまま) になると、ENABLE モードで正常に動作します。

逆に、Fig. 49(b)のDISABLEバージョンで示すように、ENA/DIS(DISABLE)ピン電圧が HIGH 状態になると、両方の出力(OUTA&OUTB)が同時にシャットダウンされ、ENA/DIS(DISABLE)ピンが LOW (またはオープンのまま) になると、DISABLE モードで正常に動作します。

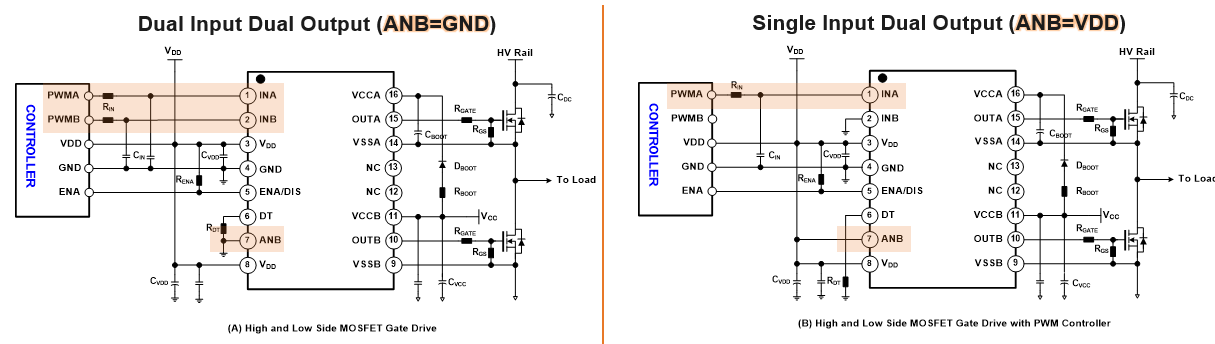

デュアル入力とシングル入力

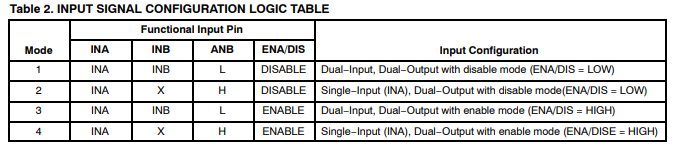

本製品はANB端子により、入力信号構成を設定できます。

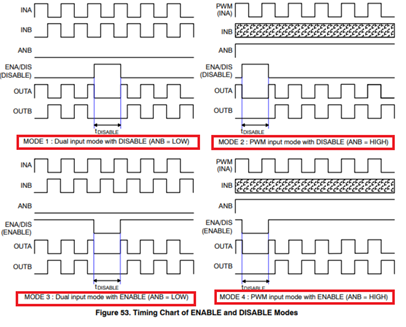

以下の表(Table.2)に示すように、入力チャネルから出力チャネルへの構成(例:シングル入力―デュアル出力、またはデュアル入力―デュアル出力)とシャットダウン機能(例:ENABLE またはDISABLE)の選択で、4つの動作モードがあります。

下図にANB端子の接続例と、Fig.53にANB端子とENA/DIS端子による入出力とシャットダウン機能のタイミングチャートを示します。

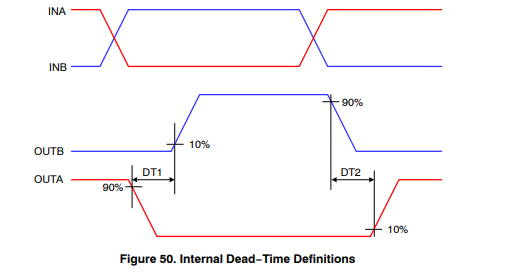

プログラム可能なデッドタイム

外部 2つの入力信号 (INA 信号と INB 信号の間) のデッドタイムが、内部設定のデッドタイム (DT1 と DT2) よりも短い場合、自動的にデッドタイムが挿入されます。それ以外の場合、外部入力信号のデッドタイムが内部デッドタイムよりも大きい場合、Fig.50 に示すように、デッドタイムはゲートドライバーおよび内部デッドタイムの定義によって変更されません。

デッドタイムは入力タイミングを監視し、出力のクロスコンダクション(ハーフブリッジ構成で、両方の出力が同時にオンになるなどの問題)を防止します。

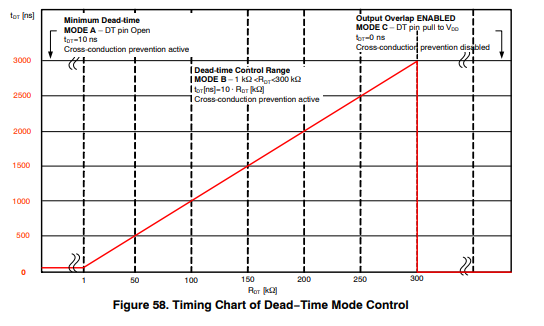

デッドタイム制御において、3つのモードがあります。

・モードA: ピン6 (DT) フローティング。

20ns以下[最小デッドタイムtDTMIN(typ)=10ns]のデッドタイムが働くため、両方のチャネル出力のクロスコンダクションは抑止されます。

・モードB: ピン6 (DT)を外部抵抗 (1kΩ~300kΩ) に接続してデッドタイムを調整

tDT (in ns) = 10 x RDT (in kΩ)

・モードC: ピン6 (DT)をVDD に接続

両方のチャネル出力のクロスコンダクション防止は無効となります。 (非ハーフブリッジアプリケーション)。

下図Fig.58にデッドタイム制御モードのタイミングチャートを示します。

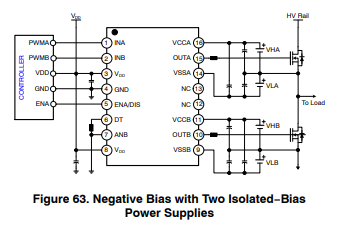

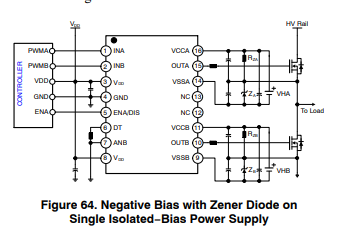

ネガティブバイアス

SiC MOSFET駆動時、SiCの動作特性を十分に活用するために、慎重に検討する必要があります。ゲートドライバーは、+20 V および -2V~-5 Vの負バイアスを供給できる必要があります。理想的でない PCBレイアウトや長いパッケージリードによって寄生インダクタンスがある場合、高いdi/dtやdv/dtのスイッチングの間に、パワートランジスタのゲートソースドライブ電圧にリンギングが発生する可能性があります。

リンギングがしきい値電圧を超えると、意図しないターンオンやシュートスルーのリスクさえあります。ゲート駆動に負のバイアスを適用することは、このようなリンギングをしきい値未満に保つ一般的な方法です。負電圧は、SiC MOSFET のノイズ耐性を向上させ、意図しないターンを抑制することができます。Fig.63やFig.64に負のゲート駆動バイアスを実装する例を示します。

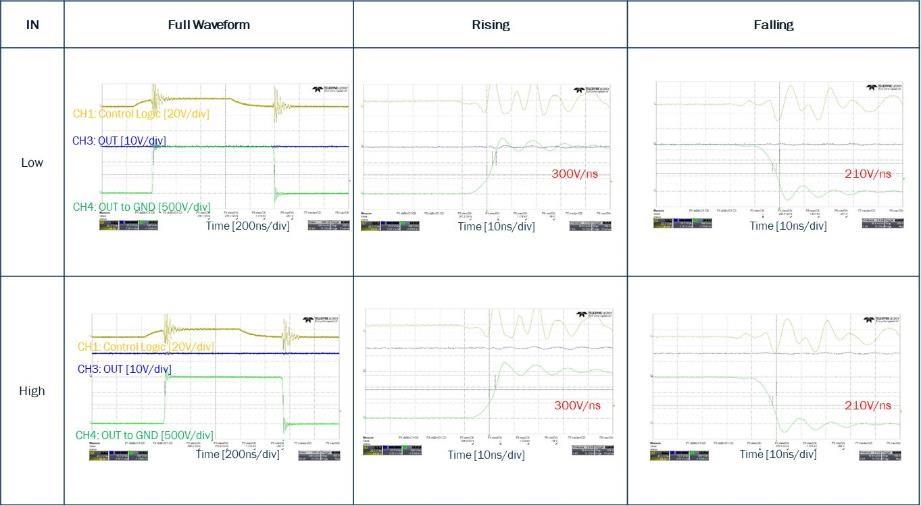

CMTI(コモンモード過渡耐性)

下図にCMTIの特性を示します。

ブロック図

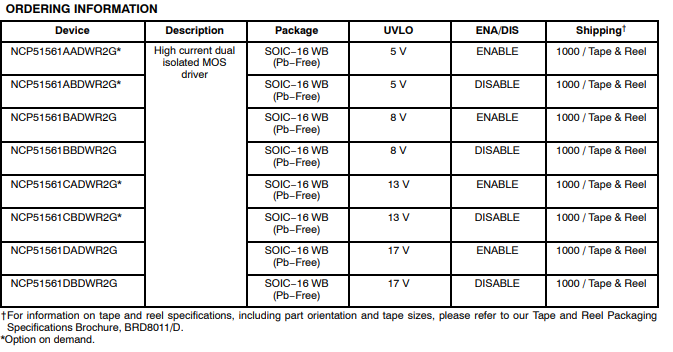

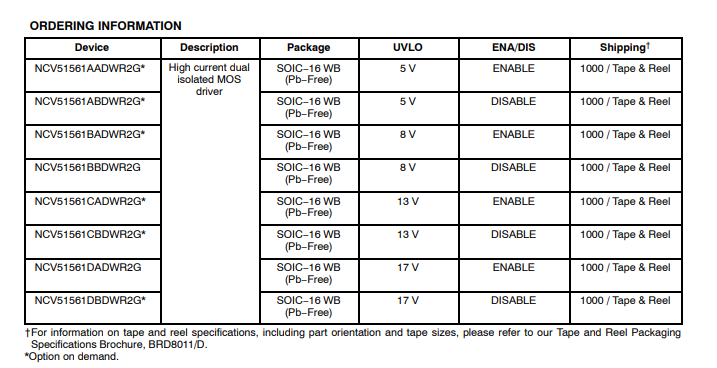

オプション選択箇所の型番表記について

NCP[NCV]51561xy

・UVLO値のオプション (x):A: 5-V, B: 8-V, C: 13-V, D: 17-V

・ENABLE/DISABLEのオプション (y):A: ENABLE, B: DISABLE

- ENABLE バージョン: ロジック入力 High は、両方の出力チャネルを有効(ENABLE)にします 。[内部抵抗プルアップ]

- DISABLE バージョン: ロジック入力 High は、両方の出力チャネルを無効(DISABLE)にします 。[内部抵抗プルダウン]

下記に各型番情報を示します。

評価ボード

評価ボードについては、駆動されるパワーデバイスのパッケージ違いでいくつか用意していますので、詳細については、問い合わせボタンまたは下記オンセミ社のwebページにて確認ください。

https://www.onsemi.com/products/power-management/gate-drivers/ncp51561

さいごに

本製品について詳細を知りたい方は、ぜひ下記オンセミ社のWebのデータシートを確認ください。

お問い合わせ / お見積もり

本製品に関してご質問、お見積もりなどのご希望がありましたら以下よりお問い合わせください。

オンセミ メーカー情報Topへ

オンセミ メーカー情報Topに戻りたい方は以下をクリックしてください。