製品概要

Certus-NXは、次世代ラティスFPGAのプラットフォームである、28 nm FD-SOIプロセスで構成された、動作周波数当たりの消費電力が従来のFPGAに比べて圧倒的に低い超低消費電力の汎用FPGAです。

製品の搭載しているハードウエアと特徴

FD-SOI

FD-SOIの特徴

・28nmプロセス

・動作周波数当たり圧倒的低消費電力(同規模帯・動作周波数のデバイスにくらべ最大1/4の消費電力)

・従来品と比べ100倍以上のSoft-Error(ソフトエラー)耐性

PCI-Express

Certus-NXには、PCI-Express(Gen1, Ge2)のハードブロックを内蔵しており、これまで以上に幅広い分野でのインターフェースをサポートすることが可能です。

MIPI I/F対応

Programable I/Oとロジックによる MIPII/Fを実現

・1laneあたり1.5Gbpsのデータレートをサポート

・CLK 1lane、Data4laneで構成した場合、一つのSoft MIPI D-PHYブロックで、6.0Gbpsまでのデータレートをサポート

・MIPI CSI-2、MIPI-DSIともに対応

カメラインターフェース側、ディスプレイインターフェース側での幅広いI/Fブリッジを可能にします。

LRAM

Certus-NXには、EBRとは別にLRAMと呼ばれる大容量メモリーブロックが内蔵されています。容量は最大2560kbitとなり、外付けメモリーを使用することなくラインバッファーを構成するなど、ある程度のメモリー容量が必要なケースにも対応可能です。

ADC

1 MSPS, 12-bit SARのADCを2ch内蔵しています。これにより、センサーからのアナログ信号処理や、供給電圧の監視などをおこなうことが可能です。

その他のコンポーネント

Programmable I/O

・MIPI、LVDS(Rx,Tx)、Sub-LVDS(Rx)、HiSPI(Rx)、SLVS200(Rx, Tx)、LVCMOSなど様々なI/Fに対応することが可能

・差動I/Fを使用した場合、Max 1.5Gbps/laneまでのデータレートをサポート

I2C、SPIハードブロック

・I2C、SPIハードブロックを内蔵。I2C、SPI経由でコンフィグレーションを実施することが可能

・ホストとなるCPU、SoCから、これらのハードブロックを使用してFLASHを外付けすることなくコンフィグレーション可能(Quad SPIにより数十ms)

・Quad SPIにも対応しており、数十msオーダーでのコンフィグレーションが可能

DSPブロック

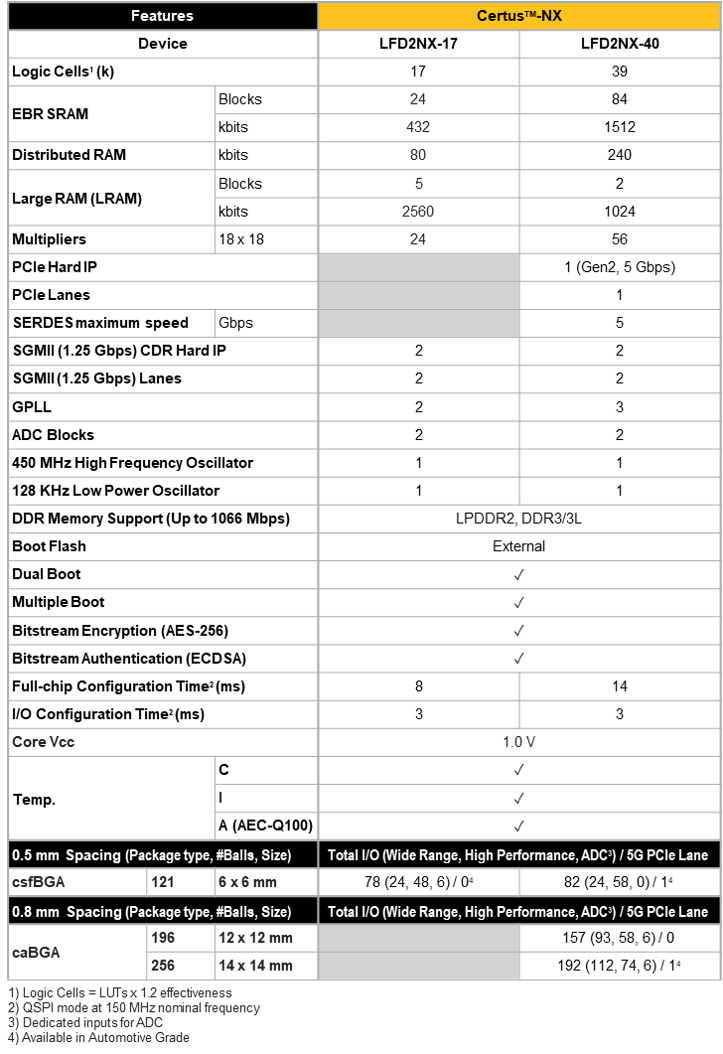

・18 X 18 Multipliersが最大56個内蔵

DRAM I/F

・DRAM I/F(DDR3、DDR3L、LPDDR2、LPDDR3をサポートし、最大1066 Mbps)に対応

製品使用例

下図はあくまでも一例のため、実現可否については、本ページ下のお問い合わせボタンからお気軽にご連絡ください。

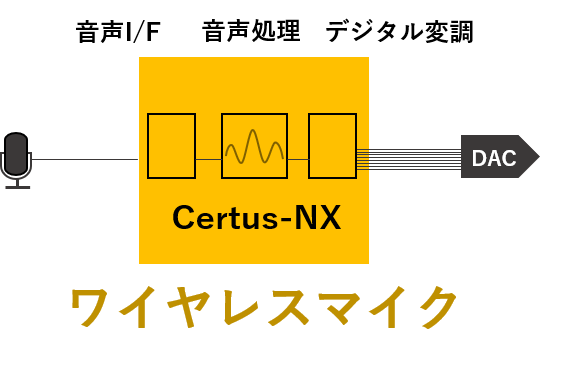

使用例1

バッテリー駆動のワイヤレスマイクでの使用例

・音声 I/F

・音声処理(フィルターなど)

・デジタル変調処理

・DAC I/F

・超低消費電力

パッケージラインナップ

お問い合わせ / お見積もり

本製品に関してご質問、見積もりなどの希望がありましたら以下より問い合わせください。

設計ツール情報

Certus-NXの設計ツールは、"Radiant"となります。