製品概要

CrossLink-NXは、次世代ラティスFPGAのプラットフォームである、28 nm FD-SOIテクノロジーで構成されたデバイスです。 FD-SOIの採用によって、これまで以上に信頼性向上と低消費電力化を実現することが可能です。CrossLink-NXでは、2つのMIPI D-PHYをハードブロックで内蔵しており、1laneあたり2.5Gbpsまでのデータレートをサポートする事が可能です。

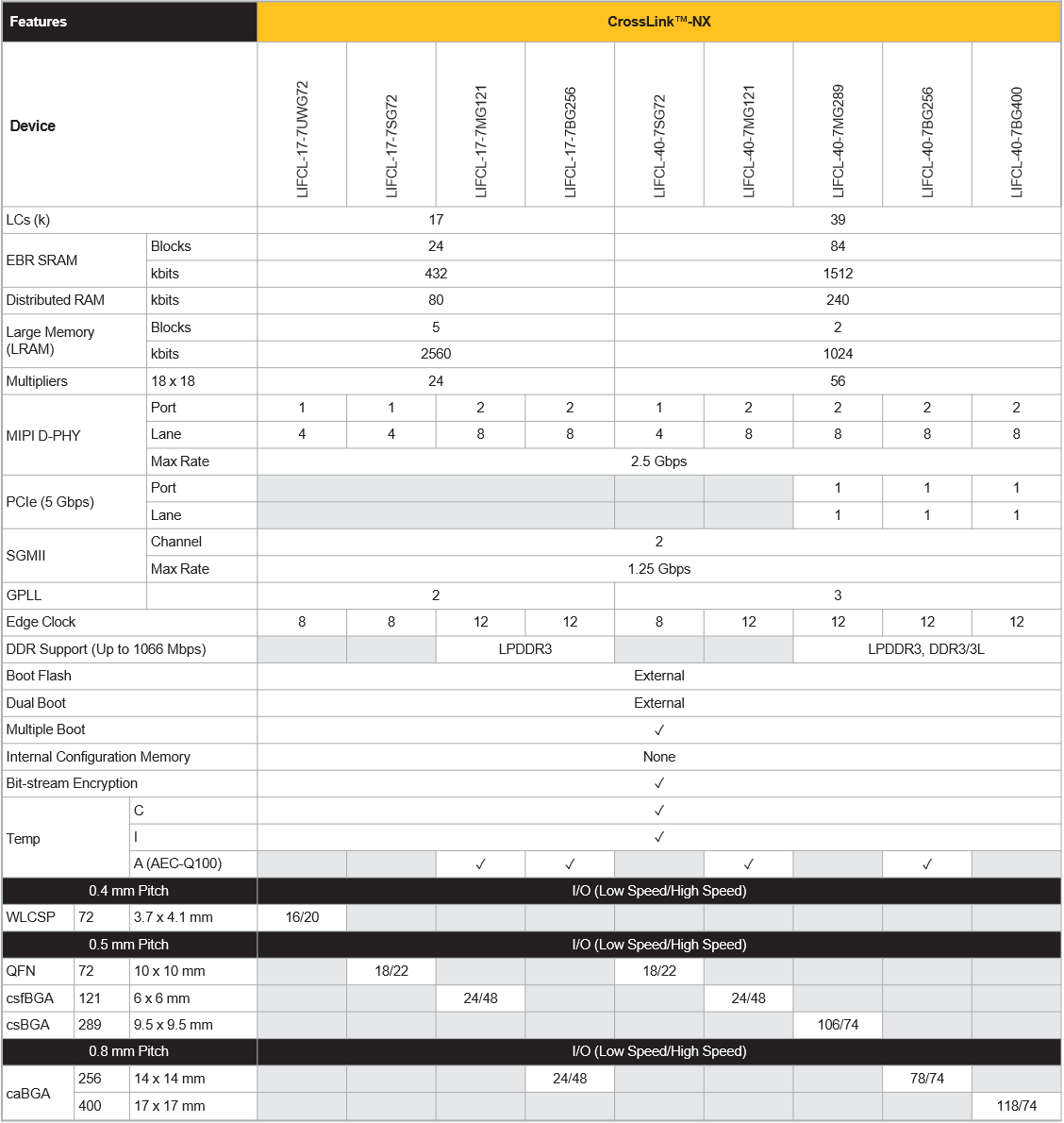

MIPI I/F以外のLVDS、SLVS、subLVDS等の差動I/Fでは、1laneあたり1.5Gbpsまで対応しており、PCI Express(Gen1, Gen2)対応のハードブロックも内蔵していることから、初代CrossLink™ よりも様々な分野でのインターフェースに対応することが可能です。ロジック容量も最大39Kロジックセル、56個の18x18乗算器、2.9 Mbの組み込みメモリー(EBRおよびLRAMブロックで構成)、12bit ADC、DRAMインターフェース(DDR3、DDR3L、LPDDR2、LPDDR3をサポートし、最大1066 Mbps)など、初代CrossLink™ と比べ、飛躍的に機能アップを図った製品です。

また、CrossLink-NX向けに多数のIP(Intellectual Property)モジュールを提供しており、お客様の仕様に合わせてGUI上でIPを構成することが可能です。これらIPを使用することにより、言語による設計が不要となり設計工数を大幅に削減することが可能です。

製品の搭載しているハードウエアと機能

FD-SOI

CrossLink-NXは、次世代アーキテクチャーである28nmプロセスのFD-SOIを採用しています。FD-SOIを採用することで、ソフトエラーの体制が従来品と比べ約100倍向上、低消費電力化(同規模帯の他社製品と比べ、最大75%程度の低消費電力化)を実現できます。また、デバイス内部のバイアスをプログラマブルに変更することが可能で、同一のデバイスにて、低消費電力版、ハイパフォーマンス版を切り替えることが可能です。

MIPI D-PHY

CrossLink-NXには、2つのMIPI D-PHYをハードブロックとして内蔵しており、1laneあたり2.5Gbpsのデータレートをサポートしています。

1つのMIPI D-PHYブロックでCLK 1lane、Data4laneまでサポートしているため、一つのMIPI D-PHYブロックで、10.0Gbpsまでのデータレートをサポートすることが可能です。また、MIPI CSI-2、MIPI-DSIともに対応しているため、カメラインタフェース側、ディスプレイインターフェース側での幅広いI/Fブリッジを可能にします。

Programmable I/O

CrossLink-NXには、MIPI I/F以外の様々なI/Fに対応できるように、プログラマブルに設定変更可能なI/Oが用意しています。具体的には、LVDS(Rx,Tx)、Sub-LVDS(Rx)、HiSPI(Rx)、SLVS200(Rx, Tx)、LVCMOSなど様々なI/Fに対応することが可能です。これらI/Oは、差動I/Fを使用した場合、Max 1.5Gbps/laneまでのデータレートをサポートしています。

EBR(Embedded Block RAM)

CrossLink-NXには、EBRと呼ばれるハードブロックで構成されたメモリーが内蔵しています。容量は最大1512kbitとなり、ユーザーロジック領域を使用することなく、簡単なデータバッファーなどの機能を構成することが可能です。

LRAM

CrossLink-NXには、EBRとは別にLRAMと呼ばれる大容量メモリブロックが内蔵されております。容量は最大2560kbitとなり、外付けメモリを使用することなくラインバッファを構成するなど、ある程度のメモリ容量が必要なケースにも対応可能です。

I2C, SPIハードブロック

CrossLink-NXには、I2C、SPIハードブロックを内蔵しており、I2C、SPI経由でコンフィグレーションを実施することが可能です。ホストとなるCPU、SoCが基板上に実装されているケースであれば、これらのハードブロックを使用してFLASHを外付けすることなく、I2C、SPI経由でコンフィグレーションさせることが可能です。また、Quad SPIにも対応しており、数十msオーダーでのコンフィグレーションが可能となっております。

PCI-Expressブロック

CrossLink-NXには、PCI-Express(Gen1, Ge2)のハードブロックを内蔵しており、これまで以上に幅広い分野でのインターフェースをサポートすることが可能です。

DSPブロック

CrossLink-NXでは、演算処理用のDSPが内蔵されております。18 X 18 Multipliersが最大56個内蔵されている為、映像信号のブリッジだけではなく画像処理を実施させる等、必要な演算処理をユーザーロジック領域を消費しないで実現することが可能です。

ADC

1 MSPS, 12-bit SARのADCを2ch内蔵しています。これにより、センサーからのアナログ信号処理や、供給電圧の監視などを行うことが可能です。

DRAM I/F

CrossLink-NXでは、DRAM I/F(DDR3、DDR3L、LPDDR2、LPDDR3をサポートし、最大1066 Mbps)に対応しています。これにより、画像処理等に必要となる、フレームバッファーを構成する事が可能となります。

製品使用例

下図はあくまでも一例の為、実現可否については、本ページ下のお問い合わせボタンからお気軽にご連絡ください。

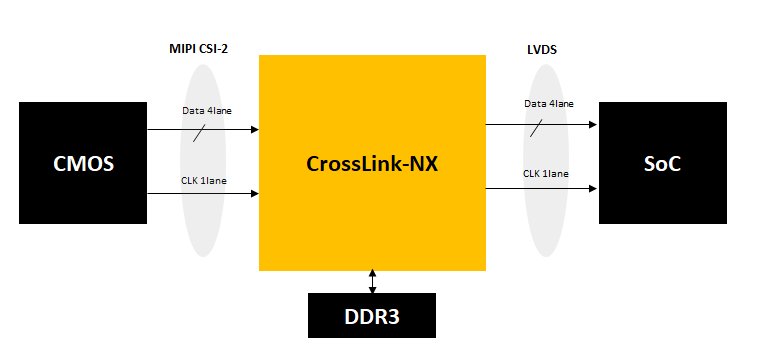

使用例1

・CMOSセンサーから出力されるMIPI I/Fを後段のSoCに直接接続できないケースでの使用例です。

・DDR3メモリーにより、フレームバッファをー構築、内部DSPにより画像処理を行うことを想定しています。

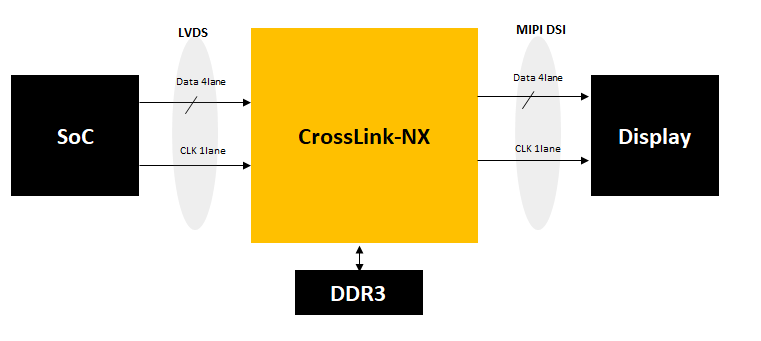

使用例2

・SoCとDisplayを直接接続できない場合の使用例です。。

・DDR3メモリーにより、フレームバッファーを構築、内部DSPにより画像処理を行うことを想定しています。

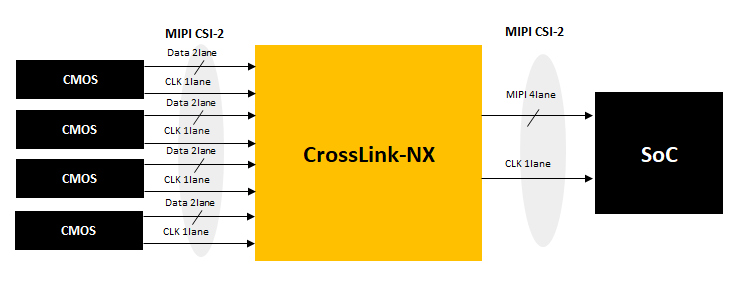

使用例3

後段SoCのMIPIポートが1chのみのため、CMOSセンサーから入力される複数chの MIPI信号を接続できないケースでの使用例です。

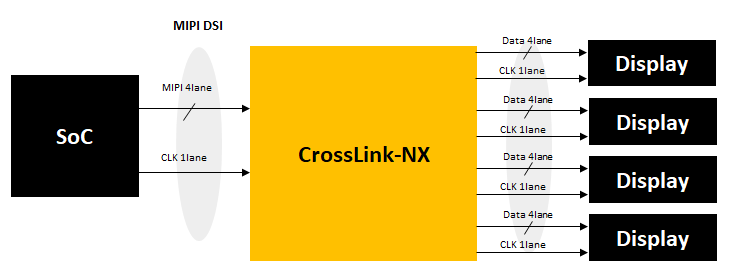

使用例4

前段SoCのMIPIポートが1chのみのため、後段の複数DisplayにMIPI信号を接続できないケースでの使用例です。

パッケージラインナップ

お問い合わせ / お見積もり

本製品に関してご質問、見積もりなどの希望がありましたら以下より問い合わせください。

設計ツール情報

CrossLink NXの設計ツールは、"Radiant"となります。