製品概要

ECP5は最大85Kのロジック容量と3.7MbitのEBRメモリー、演算処理用のDSPブロック、800 MbpsのDDR3を含む高速メモリーインターフェースを内蔵しています。さらに、ECP5は、MAX5.0Gbps低消費電力SERDESコアにより、PCIExpress Gen2、イーサーネット、V-by-One等の高速I/Fに対応可能です。

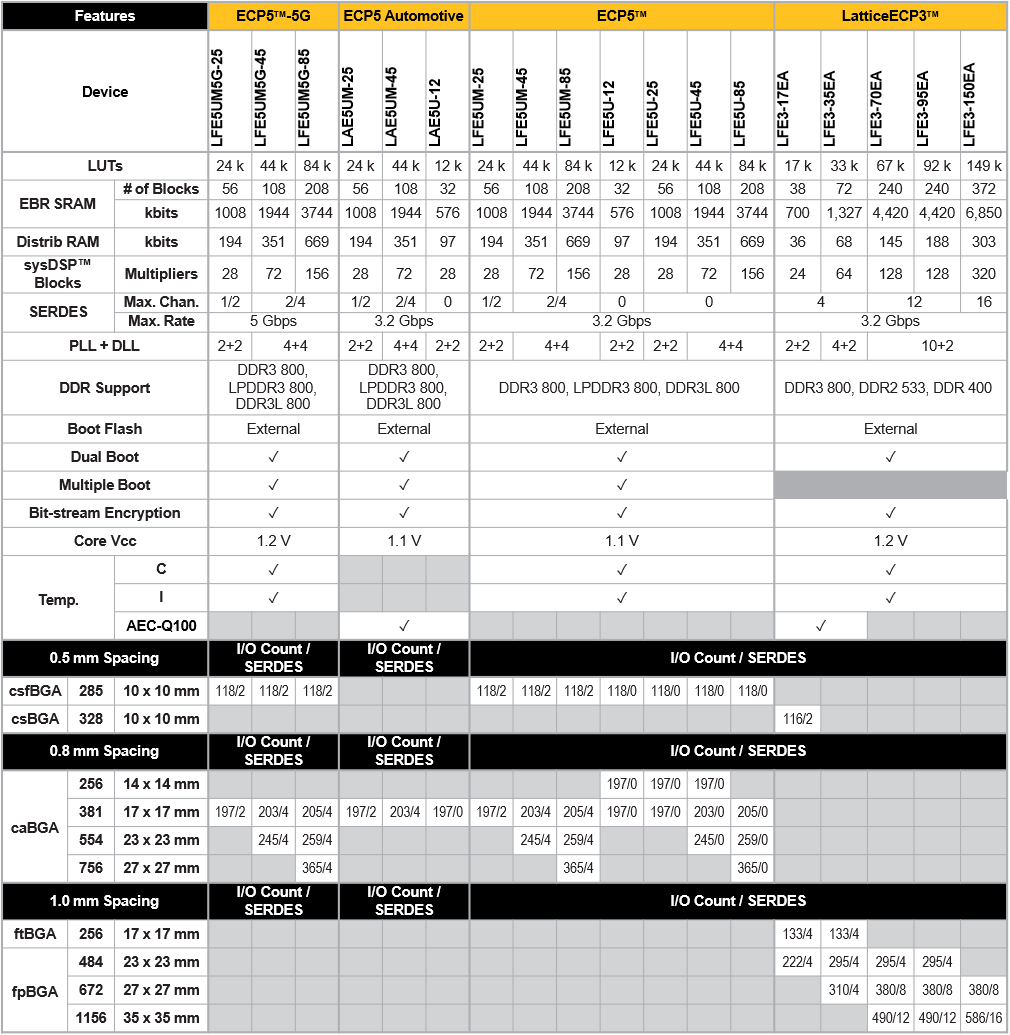

ECP5は、285 csfBGA(10 x 10mm)のタイプから、756 caBGAの多ピンタイプ、AEC-Q100対応の車載対応品もリリースされているため、幅広い分野、用途でご使用いただく事が可能です。他社製品の同等規模のFPGAと比較すると、低消費電力化に優れており、放熱機構の削減や、ダウンサイズ化など、幅広い分野、製品にてメリットを提供可能です。

また、DSPと最大3.7Mbitのメモリーを低消費電力、小パッケージFPGAに内蔵しているECP5の特徴を生かし、ラティス エッジAIソリューション用のデバイスとして、ラティス社から様々なAIソリューションを提供しています。ラティスエッジAIソリューションについての詳細は、お気軽に弊社へお問い合わせください。

搭載しているハードウエアと機能の特徴

SERDESブロック

ECP5には、Max 5.0Gpsまでのデータレートをサポート可能なSERDESブロックを内蔵しています。これにより、PCIExpress Gen2、Ethenet、V-by-One等の高速シリアルインターフェースに対応することが可能です。

DSPブロック

ECP5では、演算処理用のDSPが内蔵しています。18 X 18 Multipliersが最大156個内蔵されているため、映像信号のブリッジだけではなく画像処理を実施させるなど、必要な演算処理をユーザーロジック領域を消費しないで実現することが可能です。

DRAM I/F

ECP5では、DRAM I/F(DDR2/DDR3 and LPDDR2/LPDDR3、最大800 Mbps)に対応しています。これにより、画像処理等に必要となる、フレームバッファーを構成することが可能です。

EBR(Embedded Block RAM)

ECP5には、EBRと呼ばれるハードブロックで構成されたメモリーが内蔵されております。容量は3.7Mbitとなり、ユーザーロジック領域を使用することなく、簡単なデータバッファーなどの機能を構成することが可能です。

Programmable I/O

ECP5では、LVCMOS、LVDS、Sub-LVDS(Rx)、MIPI(Rx,Tx)、といったクロック並走型の高速差動I/F、シングルエンドのI/Fをサポートしています。

ECPシリーズ パッケージラインナップ

お問い合わせ / お見積もり

本製品に関して御質問、見積もりなどの希望がありましたら以下より問い合わせください。