次世代CMOSイメージセンサーのインターフェースである「SLVS-EC v3.0/3.1」をFPGAで実現

概要

SLVS-EC v3.0/3.1 Rx IPは、Altera®製FPGAで動作するインターフェースIPコアです。このIPを利用することで、最新のSLVS-EC規格v3.0/3.1に対応した製品をスピーディかつ容易に実現することができます。また早期導入のための「評価キット」も提供されます。

- Altera®社製 FPGAでSLVS-ECインターフェースからの受信機能を実現

- 最新のSLVS-EC Specification Version 3.1に対応

- 強力なDe-Skew機能をサポート。レーン間で発生するSkewを意識することなく基板設計が可能

- スピーディな実機評価のための「評価キット」を用意

本IPを使用したシステム構成例

SLVS-EC 規格概要

- SLVS-EC(Scalable Low Voltage Signaling with Embedded Clock)は、ソニーセミコンダクタソリューションズ株式会社により開発された高解像度&高速イメージセンサー向けのインターフェース規格です。

- SLVS-EC規格は、日本インダストリアルイメージング協会(JIIA)にて標準化がおこなわれています。

SensorとのSLVS-ECインターフェース接続

特長

- SLVS-EC Specification Version 1.2/2.0/3.0ならびに最新の3.1に対応

- SLVS-EC Link層で定義される各種機能を実現

・ 出力インターフェースとして32または64ピクセルを選択可能

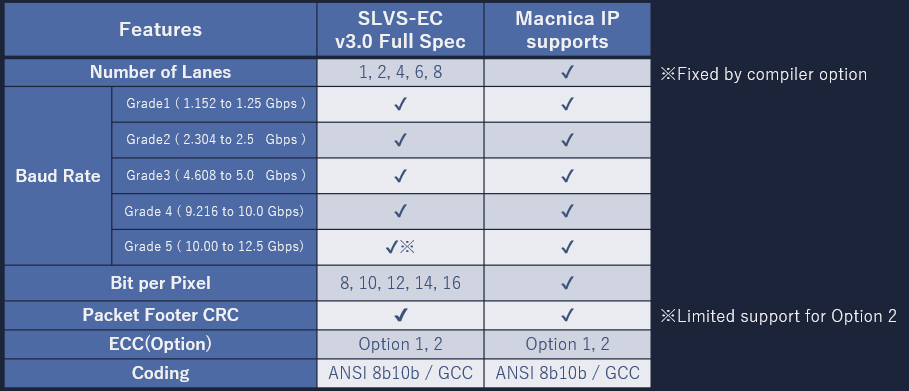

・ 8, 10, 12, 14, 16 bit/ピクセルをサポート - 最新のSLVS-EC Version 3.0/3.1で追加されたGCC (Gigabit Channel Coding) の特徴を活かし、従来のANSI 8b10bと比較して少ないオーバーヘッドでの転送を実現

- ECC(Error Correction Code)よるエラー訂正機能をサポート

- 1, 2, 4, 6, 8の各レーン構成におけるByte to Pixel変換をサポート

- ヘッダー解析とペイロードエラー検出機能を搭載

- コンパイルオプションにて不必要な機能の削除が可能

仕様諸元

対応デバイス

Altera® 社製

- Arria® 10 FPGA

- Agilex™ 7 FPGA

- Agilex™ 5E(GroupB) FPGA

評価キット: Luminous IMX537 SLVS-EC Sensor EVM

評価キットについてはこちらをご参照ください。

評価キット利用イメージ

接続の様子

外観

弊社関連ソリューション

CoaXPress® Device IP Package for Altera® FPGA - 半導体事業 - マクニカ (macnica.co.jp)

CoaXPress® Device IP Package for Microchip FPGA - 半導体事業 - マクニカ (macnica.co.jp)