![[オンラインセミナー] 改版ゼロを目指す、FPGA 基板設計手法 <無料>](/assets/images/default/event_cover.png)

本イベントの開催は終了いたしました。

イベントの特徴

基板改版ゼロを目指して!

FPGA を使った基板設計のガイドラインと最近の不具合事例から、改版ゼロで基板設計するための基板設計ノウハウを解説します。

本セミナーは、2部構成になっています。

<第1部>

FPGA を使った基板設計で最低限知っておいて欲しい基板の設計ガイドラインと弊社の技術サポート経験から見えた新たな検証ポイントを、実際の不具合例を用いて解説

<第2部>

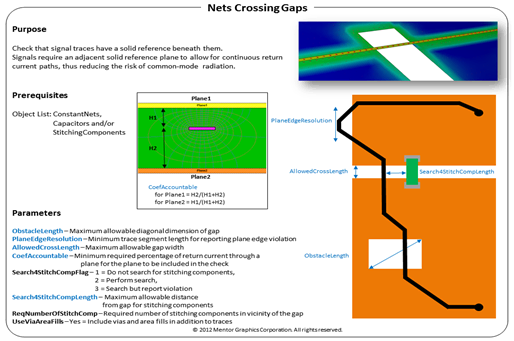

第1部のチェックポイントを PCB データから自動で検図できるツール HyperLynx DRC をご紹介

▶ HyperLynx DRC の概要

こちらは、オンラインセミナーですので、ご自宅やお客様のオフィスから受講することが可能です。

こんな人にオススメです!

■ 過去に、基板改版で苦労された方

■ デザインルールチェックを自動化して、効率化したい方

※ 競合メーカー(ベンダー)やその販社の方、競合商社の方の受講は、お断り申し上げます。

※ 個人およびフリー・メールアドレスによる参加申込み、また過去に受講されたことのある方のご参加は、お断りしています。

日程・お申し込み

| 日程 | 時間 | 会場 | 定員 | お申し込み |

|---|---|---|---|---|

| 2024/11/14 (木) |

|

ご自分のデスク |

|

受付終了

|

アジェンダ

| 時間 | 内容 |

|---|---|

| 13:30-15:00 |

第1部:FPGA を使った基板検証のポイントを実際の不具合事例を用いて解説(インテル FPGA & Analog Devices) |

※ 時間は目安ですので、前後する可能性があります。

※ 当日のアジェンダは変更される可能性がありますので、予めご了承ください。

注意事項

以下の内容を必ずご確認ください。

・ 本セミナーはオンラインセミナーとなります。視聴方法はお申込み後にご連絡いたします。

・ 開催当日は弊社オフィスにご入場いただけません。ご自身の PC からご受講ください。

・ 申し込み多数の場合には抽選となることがございます。ご了承ください。