パフォーマンスは主観的な用語です。パフォーマンスは、好きなだけ測定できます。しかし、電力変換の世界では、効率とコストという、相互に依存する2つの主要な値に帰着します。半導体スイッチの材料であるシリコンは、導通損失とスイッチング損失の両方で限界に達していることは周知の事実であり、性能向上のためにシリコンカーバイドやGaNのワイドバンドギャップ技術が検討されることが多くなっています。

これらの材料の優れた絶縁破壊特性により、より薄く、より高ドープのブロック層で低オン抵抗を実現することができ、また、ダイサイズを小さくすることでデバイスのキャパシタンスを減らし、スイッチング損失を低減することができます。SiC MOSFETやGaNのHEMTトランジスターは、最適な性能を得るためにゲート駆動条件を厳密に制御する必要がありますが、シリコンに比べて損失は少ないものの、実際にはワイドバンドギャップデバイスとしては不利な面もあります。

また、SiC MOSFETのゲートしきい値のばらつきやヒステリシス、GaNのアバランシェ定格の欠如など、シリコンスイッチとのさまざまな違いが難点となっています。

理想のスイッチに近づいたSiC FET

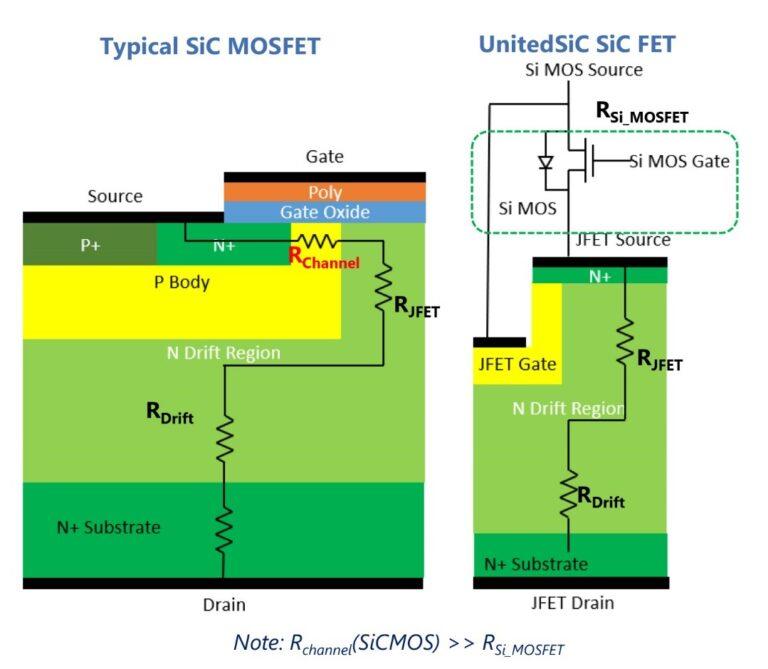

理想的で実用的なスイッチに近づくことは、必ずしも大きな飛躍ではありません。シンプルな縦型トレンチのSiC JFETとシリコンMOSFETを組み合わせれば、規格化された全体の損失がさらに低くなり、ゲート駆動が容易でクリティカルではなく、アバランシェや短絡の定格が高い堅牢な部品が得られます。このデバイスは、SiC FETカスコードであり、図1(右)に示すように、左のSiC MOSFETと比較している。SiC FETでは、SiC MOSFETのチャネル抵抗Rchannelが低電圧のSi MOSFETの抵抗で置き換えられており、反転層の電子移動度が格段に向上し、結果として低損失となっている。

また、SiC FETは、特にSi MOSFETを上にスタックしたパッケージを採用しているため、比較ダイエリアが小さくなります。

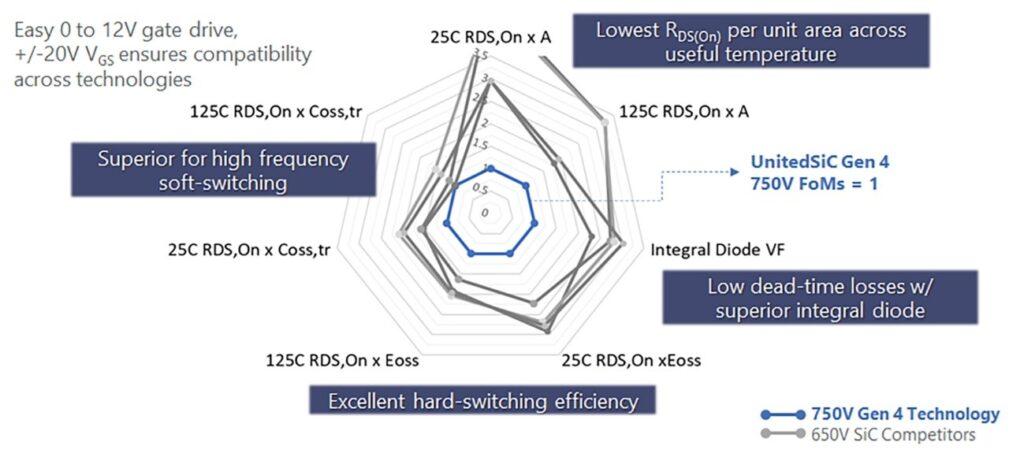

実際の性能を比較するには、「Figure of Merit (FoM)」を用いるのが最適です。このFoMは、一定のダイサイズにおけるさまざまなアプリケーションの導通損失とスイッチング損失の寄与を組み合わせたもので、これはウェハーあたりの歩留まり、ひいてはコストに重要な意味を持ちます。図2は、入手可能な650VのSiC MOSFETと、Qorvoの750V、第4世代のSiC FETを比較したものです。RDS(ON)xA (単位面積当たりのオン抵抗)は、重要なFoMであり、この値が小さいほど、所定の損失性能に対してダイ面積が小さくなり、ウェハー当たりの歩留まりが向上します。

もう一つのFoMであるRDS(ON)xEOSS (オン抵抗と出力スイッチングエネルギーの積)は、導通損失とスイッチング損失のトレードオフを特徴づけるもので、ハードスイッチングのアプリケーションでは重要です。FoM RDS(ON)xCOSS (tr)は、オン抵抗と時間依存の出力容量の関係から、高周波のソフトスイッチ回路における相対的な効率性能を示します。また、重要な比較対象として、内蔵ダイオードの順方向電圧降下があります。

SiC FETでは、VFはSi MOSFETのボディーダイオードのドロップと第3象限のJFETの抵抗ドロップの合計であり、その合計は1〜1.5V程度です。SiC MOSFETの場合、この数値が4V以上になることもあり、内蔵ダイオードで電流を整流するアプリケーションでは、スイッチングのデッドタイムで大きな導通損失が発生します。図中のオン抵抗関連のFoMは、25℃と125℃で示されており、実使用環境でのSiC FETの優れた性能を示しています。

3.6kWのSiC FETトーテムポールPFCステージ実証機、効率99.3%のピークを達成

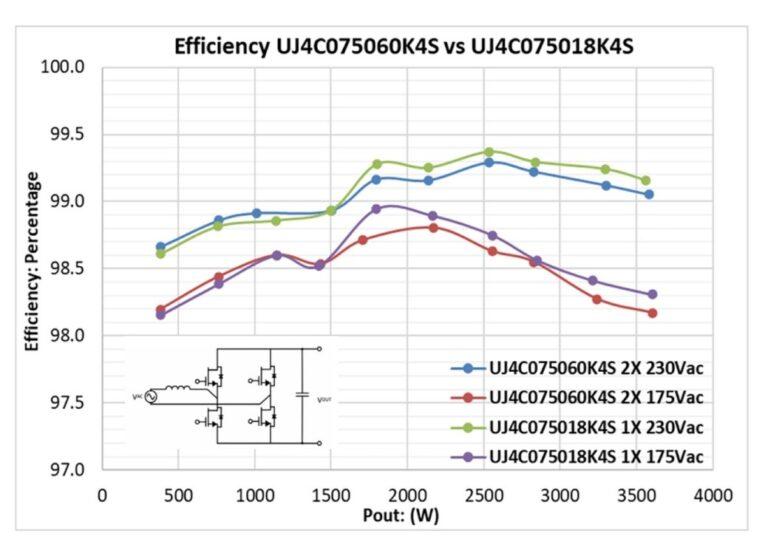

SiC FETの性能を最もよく示すのは、典型的なアプリケーションであるトーテムポールPFCステージでしょう。この回路は、ACラインの整流と力率補正を組み合わせた高効率のソリューションになり得るものとして古くから知られていましたが、高出力時にはハードスイッチングが発生し、シリコンMOSFET技術では許容できないスイッチング損失損失が発生します。

この問題を解決するのがSiC FETであり、Qorvoによる3.6kWのデモ機では、AC230Vで99.3%のピーク効率を示しており、80+Titaniumシステムの効率評価をより簡単に達成するのに役立っています(図3)。この回路の「高速」レグにある2つの18ミリオームのSiC FETでは、それぞれわずか8Wが消費されるだけで、「低速」レグには同期ACライン整流器としてシリコンMOSFETが使用されています。これらをシリコンダイオードに置き換えることで、99%以上の効率を達成しつつ、より低コストのソリューションを実現できます。図3には、60ミリオームのSiC FETを並列に配置した場合と、18ミリオームのSiC FETを「高速」レグのスイッチに1個ずつ配置した場合の結果も示しています。

シミュレーションツールでSiC FETの選択が容易に

Qorvoの「FET-Jet」計算機」を使用すれば、最適な性能を発揮するための最適なSiC FET部品の選択が容易になります。これは無料で使用できるウェブベースのツールで、ユーザーは求められる設計を整流器、インバーター、または絶縁および非絶縁のDC/DCトポロジーの範囲から選択することができます。 その後、動作仕様を入力し、QorvoのSiC FETおよびダイオードの選択肢からデバイスを選択します。このツールは、効率、コンポーネントの損失(導通およびスイッチングの寄与の割合)、ジャンクション温度の上昇などを即座に計算します。デバイスの並列化の効果はサポートされており、実用的なヒートシンク性能も指定できます。

シミュレーションと実例の結果から、SiC FETは電力変換器の性能を大幅に向上させることができることがわかりました。システム効果を考慮すると、SiC FETはこの点でも優れています。効率の向上とスイッチングの高速化により、ヒートシンクや磁気部品のサイズとコストが削減され、システム全体のバランスと所有コストの削減につながります。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

オンセミメーカー情報Topページへ

オンセミメーカー情報Topページへ戻りたい方は、以下をクリックください。