もっといいオシロスコープがないと・・・

最新のSiCスイッチは、単に「速い」のではなく、同程度のヘッドライン定格の部品であれば、シリコンよりも桁違いに優れています。これは、SiC半導体のダイサイズがはるかに小さいことに起因しており、デバイスの容量が小さくなる一方で、熱伝導率が3倍優れているため、放熱能力が維持されています。650V/1200Vのシリコンデバイスと比較してSiC縦型デバイスのチップサイズが小さいのは、ブレークダウン時の臨界電界値が10倍大きいことに起因します。オンセミのSiCカスコード JFETでは、入手可能な最高のSiC MOSFETよりもさらに半分の大きさのSiC JFETを使用しています。立ち上がり時間と立ち下がり時間がナノ秒単位で測定されるテスト回路では、実際のエッジレートを見るためにも、オシロスコープの帯域幅について真剣に考えなければなりません。

これは、スイッチモードの電力変換の効率化には良いニュースです。電圧と電流が高レベルと低レベルの間を遷移する間、過渡的な電力損失が発生します。この電力損失はピークでkWに達することもありますが、スイッチング周波数に反比例して平均化されます。しかし、最近のコンバーターは1MHz以上でスイッチングできるようになってきているので、高速スイッチングでは、この過渡損失をできるだけ低く抑える必要があります。

高速スイッチングが現実的に始まる

現在、SiC FET などのワイドバンドギャップ(WBG)デバイスのエッジレートが、100kV/µs や 3000A/µs 以上と測定されているのをよく目にしますが、これは実際に使用可能でしょうか。 TO247ベースのハーフブリッジの直列浮遊インダクタンスは、簡単に50nHになります。V = -Ldi/dtとなるので、50nHは3000A/µsで150Vを落とし、ドレイン電圧のオーバーシュートとして現れます。

同様に、ドレインの浮遊容量がわずか10pFであれば、100kV/µsの1A電流パルスが発生し、ヒートシンクの熱損失の問題が発生します。FETのソースインダクタンスも、ゲートドライブに対抗する過渡的な電圧を発生させ、スプリアスターンオンの危険性があります。さらに厄介なのはFET内部の問題で、高速遷移によりパラメトリック発振やカオス的な動作が発生します。これらの理由から、SiC FETではエッジを遅くするために内部にゲート抵抗を意図的に追加していることが多く、オン/オフを遅くするためにさらに外部抵抗を追加することが推奨されています。

SiC FETのカスコードの問題点に対処する

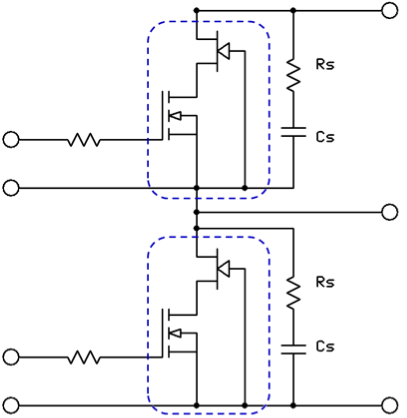

図1に示すように、低電圧MOSFETとSiC JFETを同梱したSiCカスコードを使用することで、ゲート・ドレイン間容量CGDが実質的にゼロの高速常温OFFデバイスを実現し、問題の一部を軽減することができます。

外部ゲート抵抗R(ON)とR(OFF)により、エッジレートを制御してdV/dtとdi/dtを低減することができます。 これは非常に実用的なソリューションであり、標準的なSi MOSFETやIGBTを使用している既存のシステムを、既存のゲート駆動回路を維持したまま、より効率的にアップグレードするために使用できます。外付けのゲート抵抗を使ってエッジレートを遅くすると、制御ICの出力とスイッチゲートの間に遅延が生じ、最小オン時間が制限されるため、制御範囲や動作周波数が制限されるという問題があります。また、故障時のシャットダウンコマンドへの応答時間も遅くなります。これは、WBGのメリットを最大限に生かすために高周波数での動作が必要な新規設計にとっては、深刻な問題です。

高速カスコードを実現

最近の研究によると、より高速のJFETと低値の外部ゲート抵抗を用いたSiC JFETカソードの「ブレーキを外す」ことで、単純なRCスナバを使用し、電圧オーバーシュートを適切に制限しながら、スイッチング速度と効率を向上させることが示されています。損失を単純にFETからスナバに移すだけと思われるかもしれませんが、スナバをかなり小さくしても電圧制限効果が得られることがテストで示されています。JFETの改良により、逆回復電荷量(Qrr)が50%減少し、UJ3C汎用デバイスに比べてターンオン時の損失が減少しています。

オンセミのこの「FAST」デバイスは、UF3Cシリーズの一部を構成しており、通常5~10Ωのスナバ抵抗と47pF以下のコンデンサーで使用することができます。実際に推奨される値は、デバイスのタイプや最終的なアプリケーションによって異なり、ハードスイッチされたアクティブな整流器やトーテムポールPFCなどの回路が最も効果的です。経験則では、コンデンサーはデバイスのCOSSの約3倍に設定します。既存の設計をアップグレードする場合、スナバの位置はすでに存在することが多く、UF3Cの部品を使用した値は、通常、物理的にはるかに小さく、もちろん低コストです。

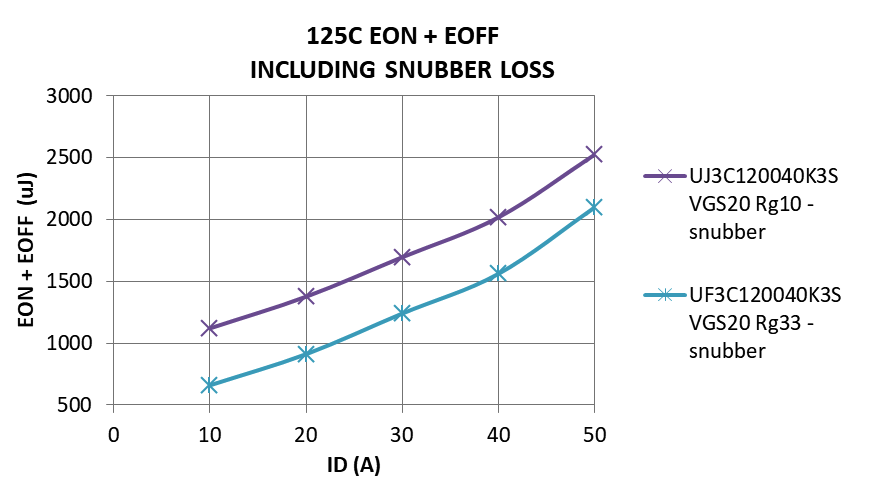

図2は、TO-247パッケージの1200V/35mΩクラスの各種デバイスの全スイッチング損失の比較を示しています。ゲート抵抗を33Ω、スナバを330pF、5ΩとしたUF3C120040K3Sは、全負荷範囲で優れた結果を示しており、Rgを1つにしてドライバーを簡素化することも可能です。

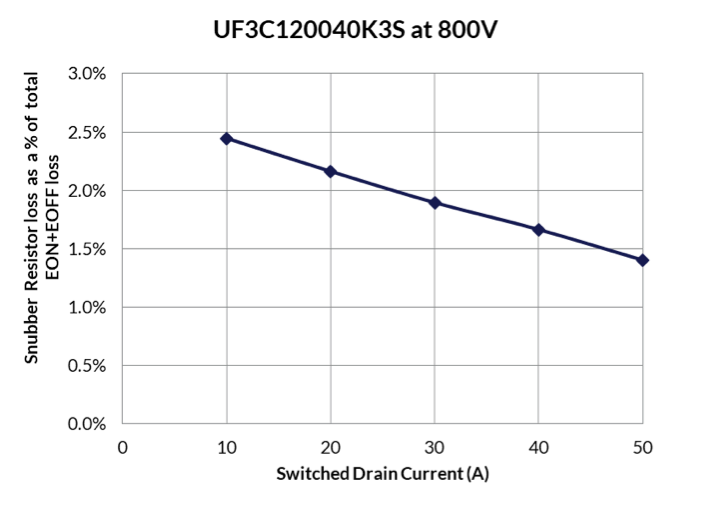

図3にUF3C120040K3S のスナバ抵抗の損失測定値を示します。必要とされる容量が非常に小さいため、この損失は全スイッチング損失のごく一部に過ぎません。

SiCカスコードの新しいUF3Cシリーズを使用すれば、小型スナバでオーバーシュートによる電圧ストレスのリスクを負うことなく、高速スイッチングが提供する効率的なメリットを得ることができます。このデバイスは、幅広いSiおよびSiCゲートドライブ電圧に対応しており、アバランシェ定格も保証されているという事実は、ボーナスです。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

オンセミメーカー情報Topページへ

オンセミメーカー情報Topページへ戻りたい方は、以下をクリックください。