概要

炭化ケイ素(SiC)などの広帯域ギャップを示す材料で構築されたデバイスは、低い導通損失とスイッチング損失、高い動作接合部温度、および高速スイッチング速度の組み合わせにより、高い電力密度を維持できるトランジスターを設計者に提供します。これらの高い電力密度は、より小さな電力制御および変換回路を可能にするのに魅力的ですが、半導体材料を選択するだけでは達成できません。このようなデバイスは、TO-247などの熱抵抗の低いパッケージで提供する必要があります。これにより、デバイスが放散する熱を簡単に逃がすことができます。残念ながら、TO-247パッケージは接続はしばしば高いインダクタンスを持ち、スイッチング速度を制限する可能性があります。

この記事では、ケルビン接続と呼ばれる技術を使用してインダクタンス問題の解決策を提供します。

ケルビン接続とは

スコットランド/アイルランドの実験家であるケルビン卿は、電流などの物理現象を測定できる精度に関心を持っていました。彼は、オームの法則を使用して低抵抗を測定するには、定義された電流を印加した場合に発生する電圧降下をチェックすることにより、電流を流す系とは別の系で正確に電圧測定を行う必要があることを理解しました。この方法は、ケルビン接続として知られるようになりました。

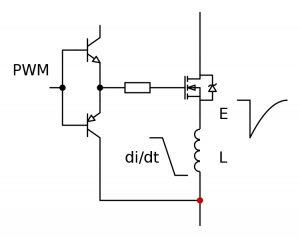

ケルビン接続は元々、回路の適切なポイントで静電圧を測定することを目的としていましたが、適切なポイントで電圧を注入するためにも使用できます。たとえば、MOSFETスイッチングのゲートを高周波で駆動する場合、デバイスのソース端子は、ゲート駆動電圧とドレイン-ソース電流の共通の接続点です。ソース接続のインダクタンスLがある場合(図1)、電流の変化はインダクタンスLと電流の変化率に比例してでゲート電圧に影響を与えます。ゲートがドライブオフされると、インダクタンスLの両端に発生する電圧がゲートをより長く保持するように作用し、電流の低下を遅くします。逆に、ターンオン中、インダクタLの両端の電圧は、電流の上昇速度を遅くするように作用します。

リードインダクタンスの影響の管理

インダクタンス L は MOSFET の内部ボンドワイヤーに起因しており、通常は 1mm あたり約 1nH です。TO-247パッケージのようにデバイスにリード線がある場合、これらの外部接続もLを増加させます。

スイッチング時間をマイクロ秒単位で測定した場合、スイッチング電流のアンペアはミリボルトの過渡電流を発生させるだけで、ゲートドライブ電圧はほとんど変化しませんでした。しかし、ワイドバンドギャップ(WBG)デバイスでは、数ナノ秒で数十アンペアのスイッチングが可能で、接続インダクタンスのnHあたり約2~5Vの過渡現象が発生します。この過渡現象がゲート駆動に加わると、MOSFETのスイッチオフが停止し、リンギングやデバイスの故障の危険性さえある。

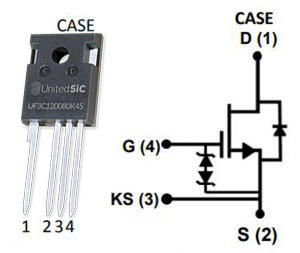

Si MOSFETでは、オフ時にゲートを負の電圧(おそらく最大-10V)まで駆動することで、電圧スパイクによるバイアスの低下を防ぐことができます。これにより、ゲートドライブの電力損失が大きくなり、これもまた、ゲートドライブの電圧振幅の合計に比例して大きくなります。この問題は、約-3Vの負のドライブ電圧しかサポートできないSiCや窒化ガリウムを使用したWBGデバイスの方が深刻です。解決策は、MOSFETダイのソース接続にゲートドライブリターンができるだけ近くなるようにケルビン接続を行うことです。これはチップスケールのパッケージでは簡単ですが、優れた放熱特性を持つTO-247パッケージを使用したい場合は、ケルビン接続を行うために4本目のリード線を追加する必要があります(図2)。

より高速なスイッチングにより、効率が向上

ケルビン接続を使用してリードインダクタンスとゲートバイアスへの潜在的な影響を制御することは、負のゲート電圧を印加することなく、ワイドバンドギャップデバイスを本来のスイッチング速度で動作させることを意味します。これにより、駆動回路が簡素化されます。この効果は劇的です。オンセミのSiC JFETカスコードを3端子パッケージに入れた場合、信頼性を維持するためにデバイスを減速させなければなりません。ケルビン接続の4端子パッケージに実装すると、電流スルーレートは5000A/µsを超えることができ、ゲートドライブ信号に影響を与えることなく、より高い効率を可能にします。

物理学的には、TO-247パッケージでも、デバイスのリードインダクタンスを考慮する必要がありますが、通常は電源経路の電圧オーバーシュートを止めるために、ドレイン・ソース間に小さなスナバを配置します。ゲートドライブループもまた、インダクタンスを最小化し、メイン整流ループによる外部磁場からのピックアップを防ぐために慎重にレイアウトする必要があります。

*オンセミのSiC JFETカスコードについては以下のURLをご参照ください。

ケルビン接続とは?

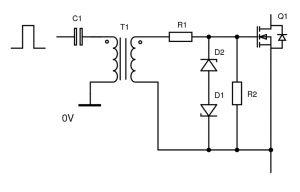

ケルビン接続を実装することには、他にも実用的な問題があります。ゲートドライブのリターンがメインのシステムの0Vで、電源グランドに接続されている場合、この共通接続点をスイッチへのケルビン接続にするのはおそらく不便でしょう。電源回路がフルブリッジの場合、少なくとも2つのローサイドデバイスがあり、それぞれがケルビン接続されているので、どちらがシステム0 Vに接続されるべきでしょうか?ケルビン接続がシステムの0Vの場合、抵抗器で発生する電圧は負になります。

これを解決する1つの方法は、ゲートドライブをオプトカプラーまたはトランスを介して絶縁することです。このような絶縁をローサイドに使用すると、ケルビン接続が浮いてシステム0Vから絶縁されます(図3)。トランスを使用することで、設計者は必要に応じて負のオフステートゲートドライブを生成し、ターン比を調整することで正のドライブを最適な値にスケーリングすることができます。

まとめ

有線のワイドバンドギャップデバイスにケルビン接続を行うことで、高電力損失をサポートするTO-247パッケージでの納入が可能となります。これにより、電気的に理想的でありながら、高電力レベルで実用的に使用できるスイッチに近づきます。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

オンセミ メーカー情報Topページへ

オンセミ メーカー情報Topページへ戻りたい方は、以下をクリックください。