SiCデバイスを使うことの難しさ

高効率、高電力密度、およびシステムのシンプルさに対する需要の高まりにより、炭化ケイ素(SiC) FETは、高速スイッチング速度、低RDS(on)、および高電圧定格により、電力エンジニアにとって魅力的な選択肢となっています。

ただし、SiCデバイスのスイッチング速度が速いと、リンギング時間が長くなり、VDSスパイクが大きくなり、高電流レベルでより多くのEMIが発生します。EVや再生可能エネルギーなどの高出力アプリケーションで作業するエンジニアにとって、これは、設計を不必要に複雑にすることなく、効率を改善し、この高度なテクノロジーの可能性を最大限に引き出すことを試みるときに懸念事項になります。

VDSスパイクとリンギングとは?

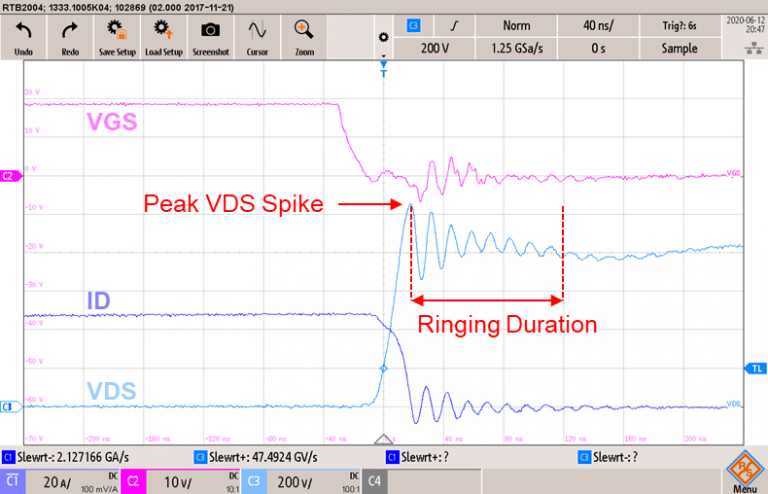

VDSのスパイクとリンギングの根本的な原因は、寄生インダクタンスです。 SiC MOSFETの典型的なターンオフ波形(図1)を見ると、ゲート-ソース間電圧(VGS)は18Vから0Vで、ドレイン電流(ID)は50Aでオフになり、バスは 電圧(VDS)は800Vです。 SiC MOSFETのスイッチング速度が速いため、VDSスパイクが高くなり、リンギング時間が長くなります。VDSスパイクが高いと、デバイスのマージンが減少し、雷や突然の負荷変動などの条件による電圧の低下に対処できます。呼び出し時間が長いと、EMIが増加します。 この現象は、高電流レベルでより顕著になります。

従来の方法

EMIを抑制するための標準的な解決策は、高いゲート抵抗(RG)を使用して、di/dtを下げることです。 ただし、この方法では、効率とEMIの間のトレードオフが発生します。 実際、高いRGを使用すると、スイッチング損失が劇的に増加します。

別の解決策は、パワーループの浮遊インダクタンスを減らすことです。 ただし、PCBレイアウトの再設計と、誘導性の低い小さなパッケージの使用が必要です。さらに、PCBの電源ループ領域を最小化できる量には制限があり、最小間隔とクリアランス距離を設定する安全規制があります。また、より小さなパッケージを使用することで、熱性能を犠牲にします。

また、EMI要件を満たし、システムのトレードオフを緩和するのに役立つフィルター設計もあります。さらに、制御方法を使用してEMIを削減できます。たとえば、周波数ディザリング技術は、電源のノイズスペクトルを拡散することによってEMIを低減します。

新しい方法

より効果的かつ効率的なアプローチは、シンプルなRCスナバを採用することです。これにより、設計上の課題が軽減され、SiCデバイスの能力が最大限に発揮されます。この単純なソリューションは、VDSのスパイクとリンギングの持続時間を効果的に制御し、広い負荷範囲で効率を高め、ターンオフ遅延を無視できることを示しています。より高速なdv/dtと追加のCのおかげで、スナバの変位電流も大きくなります。つまり、ターンオフ遷移時のIDとVDSのオーバーラップが少なくなります。

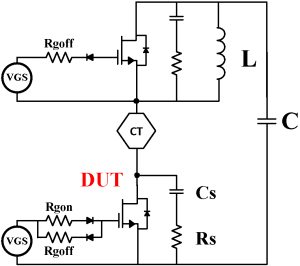

スナバの効果を研究するためにダブルパルステスト(DPT)を使用して、これの証拠を見ることができます。誘導性負荷のあるハーフブリッジ構成です。ハイサイドとローサイドの両方が同じデバイスを使用します。VGS、VDS、およびIDは、ローサイドデバイスから測定されます(図2)。変流器(CT)は、デバイス電流とスナバ電流の両方を測定します。したがって、測定されたスイッチング損失には、デバイスのスイッチング損失とスナバ損失の両方が含まれます。

スナバを使用する場合、それはSiCMOSFETのドレインとソースの両端に10Ωの抵抗と直列に接続された200pFのコンデンサーです。

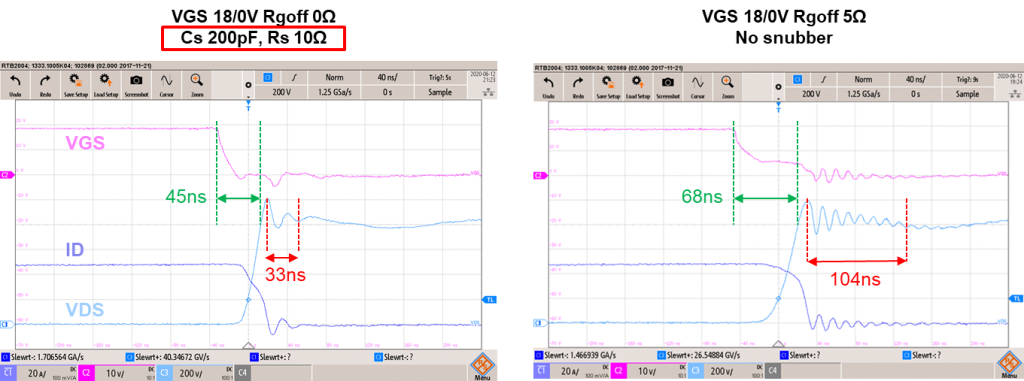

まず、ターンオフを比較してみましょう(図3)。 図1の同じデバイスの場合、左側の波形はRCスナバと低RG(off)を使用しており、右側の波形は高RG(off)を使用していますが、スナバは使用していません。どちらの方法でも、ターンオフVDSのピークスパイク電圧が制限されます。ただし、スナバは33nsを使用してリンギングを減衰させますが、高RG(off)のリンギング持続時間は100nsを超えます。また、スナバは高いRG(off)を使用するよりも遅延時間が短くなります。したがって、スナバは、VDSターンオフスパイクとターンオフ時の呼び出し時間の両方を制御するのにより効果的です。

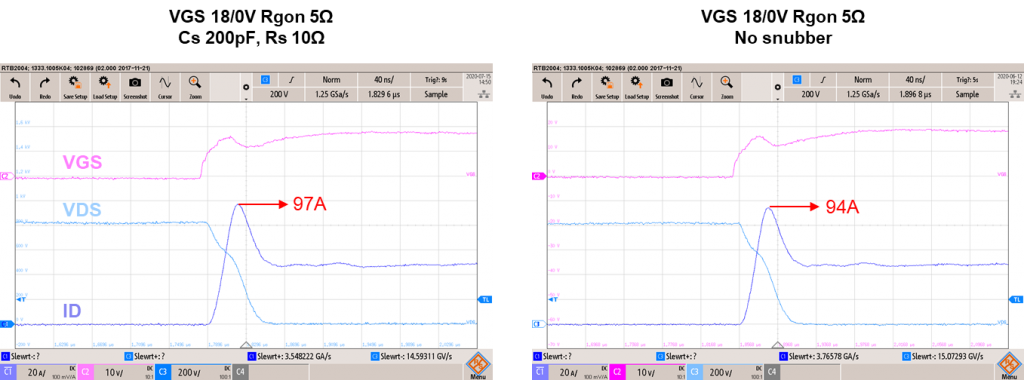

ターンオン側(図4)で、RCスナバとRG(on)が5Ωの波形とスナバのない波形を比較すると、小さいスナバを使用すると、ピーク逆回復電流(Irr)が94Aから97Aまで増加することがわかります。それ以外は、ターンオン波形への影響はごくわずかです。

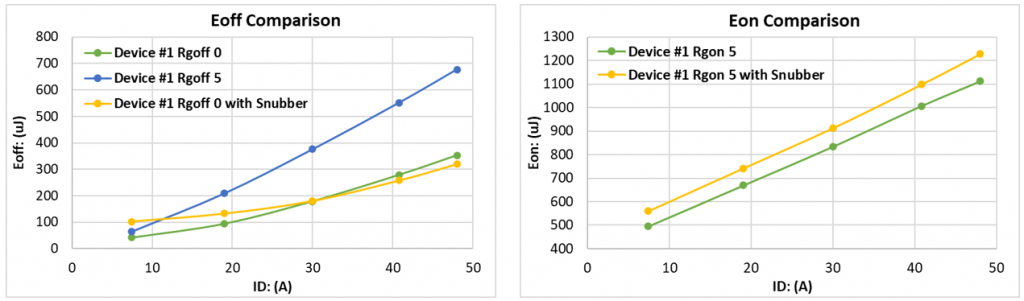

これは、VDSスパイクとリンギング持続時間の制御において、スナバが高RG(off)よりも効果的であることを示唆しています。 しかし、スナバはより効率的でしょうか?(図5)

48Aでは、高いRG(off)は、低いRG(off)のスナバを使用する場合の2倍以上のターンオフスイッチング損失があることがわかります。したがって、スナバは、VDSスパイクとリンギングのより良い制御を提供しながら、より高速なスイッチングを可能にするため、ターンオフにおいてより効率的です。

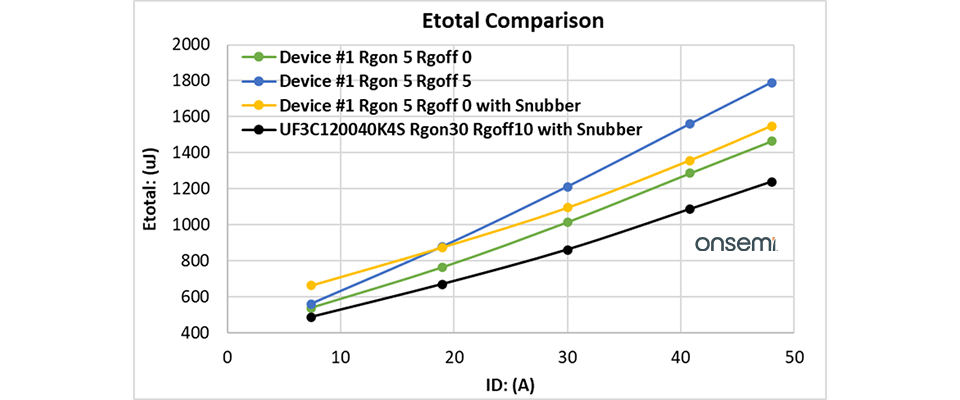

ターンオンスイッチング損失を見ると、スナバはEonを平均70µJだけわずかに増加させます。したがって、全体的な効率を完全に見積もるには、EoffとEonを合計して、Etotalを比較する必要があります(図6)。デバイスがフルスピードで切り替わるとき、18Aを超えるとスナバがより効率的になることは明らかです。40A/40kHzでスイッチングする40mΩデバイスの場合、スナバを使用して高RG(off)と低RG(off)を使用した場合のスイッチング損失の差は、デバイスあたり11Wです。

したがって、スナバは高RG(off)を使用するよりも効果的で効率的であると結論付けることができます。第4世代のSiCカスコード JFETデバイスに入ると、このシンプルな設計ソリューションは、システムの電力効率を最適化しながら、さらに低い総スイッチング損失を提供し続けます。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

オンセミ メーカー情報Topページへ

オンセミ メーカー情報Topへ戻りたい方は以下をクリックしてください。