ワイドバンドギャップのデバイス - これらのデバイスが約束すること

炭化ケイ素(SiC)や窒化ガリウム(GaN)などのワイドバンドギャップ(WBG)半導体技術は、現在のホットなトピックであり、ユニバーサルワイヤレス充電から電力変換器まで、ほとんどのアプリケーションにおいてサイズが縮小されることを約束できるデバイスです。 ただし、利用可能なテクノロジーとデバイスの選択は必ずしも簡単ではなく、それらが浸透できる市場は皆様が思っているよりも広いでしょう。

一歩下がって、WBGデバイスとは何かを概説しましょう。 半導体には、原子核の周りの異なるエネルギー準位(価電子帯と伝導帯)を占める結合電子があります。 電子は伝導帯まで移動して電流を流すことができますが、そのためにはエネルギーが必要です。 WBGデバイスでは、このエネルギー要件はシリコン(Si)よりもはるかに大きくなります。 たとえば、SiCは1.1eVのSiと比較して3.2電子ボルト(eV)を必要とします。 WBGデバイス内の電子を伝導帯に移動するために必要なエネルギーの増加は、同じスケールのSiと比較してより高い電界破壊性能に変換されます。 同じ理由で、SiCは故障する前に高温(熱エネルギー)に耐えることができ、また材料として、Siの約3.5倍の熱伝導率を持っています。 実際には、これらの属性は、高電圧および高電力レベルでの高周波、高温動作を約束します。

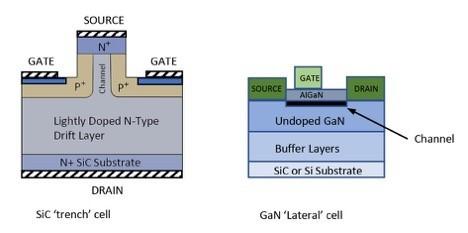

SiCで最初に利用可能だったデバイスは単純なダイオードでしたが、材料技術はJFETとMOSFETの製造を可能にするために進歩しました。 図1は、横方向構造のGaN高電子移動度トランジスター(HEMT)セルと比較して、非常に低いオン抵抗を与える垂直トレンチ構造のSiCJFETのセルを示しています。

アプリケーションに最適なソリューションを見つける

エンハンスメントモード、ノーマリーオフ、Si-および現在のSiC-MOSFETは、低電力および中電力のスイッチングアプリケーションに最適なコンポーネントですが、いくつかの欠点があります。

• MOSFETには、高い順方向電圧降下と比較的高い回復電荷(Qrr)を持つ一体型ボディーダイオードがあります。これは通常、3倍の過熱によって変化します。高いQrrと高い順方向電圧降下は、チョッパー、誘導性負荷のあるハードスイッチブリッジ、PFCステージ用のブリッジレストーテムポール回路など、ボディーダイオードを強制または導通させる回路に高い損失を発生させます。ボディーダイオードをバイパスするために、追加の並列SiCショットキーダイオードを追加できますが、かなりのコストがかかり、メリットは限られています。

• MOSFETの場合、ゲートターンオンしきい値は低く、例えばSiCデバイスでは約2.2Vになりますが、最適で安全なパフォーマンスを得るためにゲート-ソース間電圧を非常に厳しい制限内に維持する必要があります。

• 短絡飽和電流はゲート-ソース間電圧によって変化し、制御が不十分であるため、システムの信頼性が大きく懸念されます。

• MOSFET周辺の入力、出力、およびミラー容量は比較的高いです。これは、重大なゲート駆動電力要件、静電容量が充電および放電されるときの損失、およびミラー静電容量を介してゲートに注入された電流からのスプリアスデバイスのターンオンの危険性につながります。

JFETは、ボディーダイオードなしで検討できますが、通常、ゲート電圧がゼロの場合はオンになり、約-7Vが印加されるとオフになります。ノーマリーオンデバイスはサーキットブレーカなどの一部のアプリケーションで役立ちますが、スイッチアプリケーションではノーマリーオフタイプが非常に好まれます。

スイッチのカスコード接続

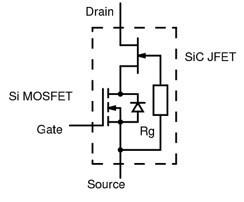

WBGテクノロジーを使用しながらMOSFETの問題を回避するために、メーカーは1930年代の真空管テクノロジーに戻し、図2に示すカスコード接続を再検討しました。

ここで、低電圧Si-MOSFETはそのドレインでSiCトレンチJFETのソースに接続され、JFETゲートはMOSFETソースへの接続されています。 Si-MOSFETゲートに正の電圧を印加するとONし、JFETのゲートとソースを効果的に短絡してONします。 Si-MOSFETゲートがゼロボルトのときはオフになり、ドレインの電圧が上昇します。

ただし、これが約+ 6Vに達すると、JFETゲートはソースよりも6V負になり、オフになります。 MOSFETのドレイン電圧は、JFETを完全にピンチオフするために必要な電圧に基づいて15〜20Vに増加します。他のカスコード実装とは異なり、ピンチオフ後のJFETのCDSがほぼゼロであるということは、Si-MOSFETを備えた容量性分圧器がHVJFETの両端に発生するすべての電圧を優先することを意味します。

したがって、SiMOSFETは、数ミリオームの非常に低いオン抵抗RDS(on)を伴う低電圧タイプにすることができます。その場合、全体的なオン抵抗はJFETチャネルによって支配されます。これで、MOSFETのような通常はオフのデバイスができましたが、ボーナスとして他のMOSFETの制限も解決しました。

• 低電圧Si-MOSFETの一部としてボディーダイオードが導入されていますが、高電圧SiCMOSFETよりも2倍以上小さく、標準的なファストリカバリーダイオードの20倍程度の非常に低いQrrの数値を持つものです。ボディーダイオードが導通する実用的な回路では、余分な並列ダイオードは必要ありません。

• Si-MOSFETゲートドライブはSiC-MOSFETと比較して重要ではなく、最大+/- 25Vに耐えることができます。

• カスコードのSi-MOSFETのゲート・ソース電圧は、約+8Vでフルエンハンス後の短絡飽和電流に影響を与えません。電流は現在、JFETの垂直トレンチ内の「ピンチオフ」効果によって制御されており、これによって電流は飽和レベルに効果的に制限されています。さらに、電流によって生じる加熱効果がJFETチャネルの導電率を低下させ、自己制限特性を与えます。ジャンクション温度の許容値が高いことも、この点で役立ちます。

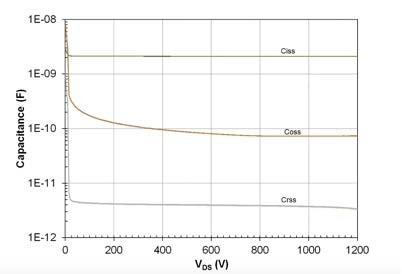

• カスコード内のSi-MOSFETは低電圧であり、アプリケーション用に最適化されているため、その入力容量Cissは低く、カスコードドレインゲートです。ミラー容量Crssは実質的にゼロです。 1200V 60mΩデバイスについては、図3を参照してください。これにより、ゲート駆動電力が減少し、ドレインの正方向のdV/dtがミラー容量を介して電流のスパイクをゲート駆動回路に押し込むことによるスプリアスターンオンの危険性が排除されます。

• Cossに関連するスイッチング、Eossで失われるエネルギーがあります。 650Vクラスのデバイスでは、約6.5µJのSiCカスコードは、同等のSi-またはSiC-MOSFETの半分以上の値を持っています。

カスコードに注意点があるとすれば、その速度を抑える必要があります。 実用的な設計では、dV/dtとdi/dtを管理可能な値に制限して、EMC規格に適合させ、関連する回路の誘導電流スパイクと接続のインダクタンス全体の電圧スパイクを制限します。 注意深く構成すると、カスコード構成により、外部ゲート抵抗を使用してdV/dtおよびdi/dtを効果的に制御できます。

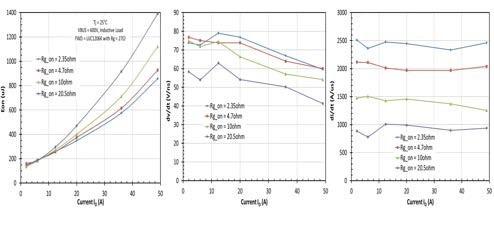

図4は、600Vの誘導負荷を備えたUJC1206Kカスコードデバイスの2.35〜20.5オームのゲート抵抗R(on)で確認された値を示しています。 1nHのインダクタンスごとに、1000A/μ秒のdi/dtで1Vのトランジェントが発生することに注意してください。 このトランジェントがゲート回路ループに現れると、ターンオンまたはターンオフマージンが減少します。同様に、簡単に達成できる50V/ns dV/dtは、わずか20pFの浮遊容量に1Aの電流スパイクを生成します。

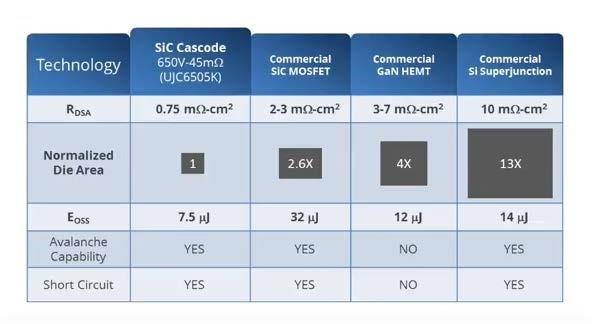

図5は、WBGテクノロジーの相互特性と従来のSiスーパージャンクションMOSFETの相対的な特性をまとめたものです。

カスコードは既存のアプリケーションに「ドロップイン」します

WBGデバイスの主な利点は、数MHzおよび200°Cを超える接合部温度での速度と高温動作として見られることが多く、効率の向上とともにサイズとコストの劇的な削減を約束します。これは、新しいマグネティックス、共振トポロジー、RFスタイルのレイアウトを使用したゼロからの再設計で確実に可能になります。おそらく最良の例は、GoogleとIEEEの「リトルボックスチャレンジ」で、当時の最先端バージョンの10分の1の50W/立方インチの電力密度で95%の効率のコンバーターを設計することです。勝者は、WBGテクノロジーを使用して145W/cu-inよりも優れた性能を達成しました。

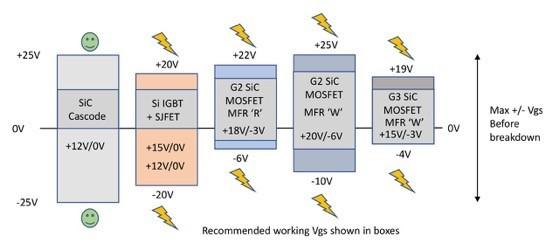

ただし、既存の機器をアップグレードするための広大な市場があり、完全な再設計は実現可能でも経済的でもありません。 ほとんどのWBGスイッチソリューションは、IGBTやSi-MOSFETなどの設計されたコンポーネントには適していません。 これらのコンポーネントのゲートドライブシステムは、SiC-MOSFETやGaNHEMTデバイスなどに必要な正確なゲートドライブ電圧と互換性がありません。 ただし、カスコードSiCJFETはすぐにドロップインできます。従来のTO-247およびTO-で使用できます。

220のケーススタイルで、他のすべてのデバイス標準を含む幅広いゲート駆動電圧を受け入れることができます(図6)。一部のカスコードには、過電圧とESDから保護するためのゲートクランプダイオードも含まれています。 既存のシステムのIGBTおよびSi-MOSFETのゲートは、多くの場合、デューティーサイクルによって変化する不正確な電圧のトランスを介して直接駆動されます。この場合も、SiCカスコードに対するゲート電圧ドライブの許容範囲が広いため、置換が容易になります。

カスコードは、既存の設計に一致するゲート抵抗を選択することで速度を落とすことができ、外部高速回復ダイオードを備えたSi-MOSFETやIGBTと比較して、ボディーダイオードのエネルギー損失を劇的に削減します。

システムの安定性と潜在的な速度が向上し、ミラー効果が実質的になくなり、ゲート駆動電力が大幅に低下します。例として、UJC1210K 800V/20AのSiCカスコードをIGBTタイプIRG7PH35UD600V/25Aと比較すると、カスコードの総ゲート電荷QG(合計)は47.5nC、IGBT85nCです。これは大きな違いではないように思われるかもしれませんが、IGBTが9V/+ 15Vを必要とする場合でも、カスコードはゲートで0V/12Vに切り替えることができます。ゲート駆動電力要件PGは次の式で与えられます。

PG = QG(total)× F × VSW

ここで、Fは動作周波数、VSWは合計ゲート電圧振幅であり、IGBTの場合はカスコード値の2倍です。したがって、必要な総電力は、カスコード接続で約4分の1です。ゲートが各スイッチング周期で完全に充電および放電される限り、電力はどのデューティーサイクルでも一定であることに注意してください。

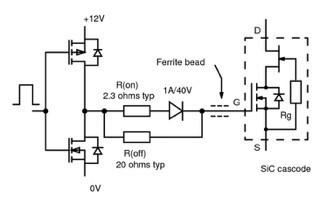

したがって、SiCカスコードは、IGBT、SiMOSFET、またはSiC-MOSFETを使用する多くのアプリケーションにドロップでき、スイッチング速度を最適化するために直列ゲート抵抗値を変更するだけです。 SiCカスコードの典型的なゲート駆動回路を図7に示します。R(on)は通常R(off)よりも低く、カスコードの内部発振を避けるために最小値は約10オームである必要があります。シリーズフェライトビーズは、ダンピング用のオプションです。

SiC vs GaN

SiCよりも遅れて登場したGaNは、コスト、歩留まり、信頼性の問題から採用が遅れています。理論的には、SiCやSiよりも高いスイッチング速度が可能で、電子移動度がはるかに高くなりますが、熱伝導率がSiCより3分の1低いため、電力密度の可能性が制限されます。現在、SiCデバイスは約650V〜1.2kV定格以上で一般的ですが、GaNは約650Vに制限されており、同じ電圧でより成熟したSiC製品の現在の低コストおよび実証済みの堅牢性と競合するのに苦労しています。

GaNサプライヤーは、データセンター、EV/HEV、太陽光発電などの低電圧/電力市場が、期待されるコスト削減の実現に伴って開かれることを望んでいます。ただし、SiCカスコードは、特に双方向DC-DCコンバーターおよびトーテムポールPFCのアプリケーションにおいて、これらの市場領域にも対応しています(以下を参照)。IHSのデータは、2020年代半ばまで使用量の相対的な分割が同じままであり、WBG市場の合計が35億ドルに達し、そのうちGaNがまだ約5億ドルであることを示しています。

SiCは現在、サプライチェーンで十分に確立されており、部品はハイサービスディストリビューターのカタログで入手できます。SiCトレンチカスコードは、性能指数RDSAがはるかに優れているという点で、GaN、実際にはSi-MOSFETおよびSiC-MOSFETよりも利点があります(図8)。RDSAは、特定のダイ領域で達成されるON抵抗の組み合わせの尺度であり、デバイス間で同じ電力レベルを比較すると、たとえばSiCカスコードはGaNよりも5〜10倍優れています。言い換えると、ダイのサイズを5〜10倍小さくすることができるため、静電容量が小さくなり、ウェハーあたりのダイが多くなり、関連するコストが削減されます。熱伝達の領域は少ないですが、SiCはGaNの3倍の熱伝導率を持ち、とにかく特性の変化がほとんどなく、250°Cまでの接合部温度に耐えます。

おそらく、GaN電圧定格が競合するように改善されたとしても、産業用システムでSiCに優位性を与える要因は、誘導性負荷で発生する可能性がある電圧アバランシェ条件に耐えるSiCの能力です。メーカーは、SiCの信頼性過電圧過大応力を示す広範なデータを持っていますが、GaNは、最大電圧を超えてはならないということを除いて主張していません。

デバイス間のより具体的な違いは、利用可能なパッケージです。 SiC部品は一般的にTO-247およびT0-220スタイルで入手可能であり、既存の設計のMOSFETおよびIGBTの代替品としてドロップインできるため、すぐに利点が得られます。さまざまな標準の表面実装オプションが開発中です。ただし、GaNデバイスの製造元は、固有の速度制限接続インダクタンスを備えたリード付きパッケージが、部品から最高の潜在的性能を得る上での障壁になることを認識しています。

したがって、彼らは主に表面実装、単一ソース、チップスケールのパッケージングを選択しており、新しい設計への採用を制限しています。ここで、システム設計をGaNデバイスの特性に適合させて、より小さな受動部品、特に磁気およびコンデンサーを与えることができます。

現在のWBGデバイスのポジション

SiCカスコードは、最大約85Aの電流で定格650Vおよび1200V、オン抵抗が約30mΩで一般的に入手可能です。 過去の記事で紹介いたしました、「スーパーカスコード」も利用可能です(定格3.5kVを超える直列接続されたJFET)。約70Aおよび45mΩで最大1700VのSiCMOSFETが利用可能ですが、それらの内部ボディーダイオードは、カスコードとは異なり、比較的低速であり、アプリケーションで必要な場合、たとえば高価で高速なSiC外部ダイオードでバイパスする必要があります。

GaNデバイスは650V定格で約60Aおよび25mΩで、多くのSiC部品と同等ですが、理論的にはより高速なスイッチングが可能です。興味深いことに、100V定格で入手可能なGaNデバイスは、オン抵抗に関して従来のSi-MOSFETよりも優れているわけではないため、このレベルでコモディティーMOSFETに比べて大幅なコストがかかることに対抗するために速度の利点に依存しています。

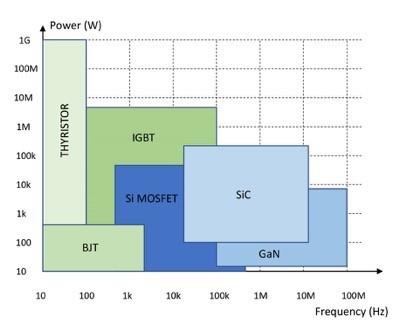

将来的には、IHSデータはWBGデバイスのデザインインの大幅な増加を明確に示していますが、IGBTおよび従来のMOSFETの売上も成長市場で増加します。問題は、さまざまなWBGデバイスが特定の市場セグメントをどのように支配するかということです。図9は、パワーデバイスの電力と動作周波数の将来の分割の可能性を示す1つのビューですが、GaNの存在は、予想されるコスト削減に依存します。

アプリケーション

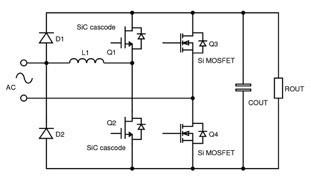

潜在的に高速スイッチングと低損失を備えたWBGデバイスの高温機能により、パフォーマンスが重要となる軍事および産業用アプリケーションに最適です。ブリッジ回路は、インバーター、溶接、クラスDオーディオアンプ、モータードライブなどの高出力で使用される明らかな候補です。主な利点が見られる特定のアプリケーションは、ブリッジレストーテムポールPFC回路です(図10)。

ここで、Si技術を使用する以前の回路は、通常使用されるMOSFETのボディーダイオードの性能が遅いために制限されていました。並列のSiCダイオードは役立ちますが、コンポーネント数を減らすという目的を達成できなくなります。これにより、「臨界伝導」モードが強制的に使用され、各伝導期間の終わりにスイッチング電流がゼロに設定されます。ただし、この可変周波数モードでは、高いピーク電流と高いEMIが発生します。カスコードSiCJFETを使用すると、「連続導通」モードを使用して、効率を高め、インダクターサイズを縮小し、固定動作周波数でのフィルタリングとEMIの問題を緩和できます。1.5kWおよび230VACラインでQorvo UJC06505Kデバイスを使用した回路例は、99.4%という驚異的な効率を示しました。

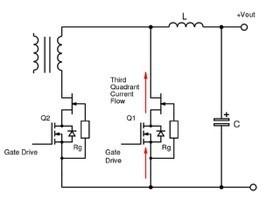

コンバーターのプライマリースイッチで高効率を達成するには、DC出力の整流における同様の改善と一致させる必要があります。 ここでも、SiCカスコードは「同期整流」用に構成できるため、ここに適合します(図11)。 いわゆる第3象限動作では、順方向または降圧型コンバーターの「順方向」および「フライホイール」期間中に、出力インダクターを介していずれかのカスコードのソースからドレインに電流が流れて負荷がかかります。

ボディーダイオードを流れる電流により、JFETのゲート-ソース間電圧が約+ 0.7Vに設定され、自然にハードオンになります。カスコードゲートが高く設定されている場合、内部Si-MOSFETチャネルが導通し、合計ON抵抗がカスコードのRDS(on)になり、導通損失が低くなります。 Q1はフライホイール整流器を形成し、Q2は前方整流器を形成します。

堅牢性の懸念

高電力アプリケーションでは、過渡的な短絡や過電圧による堅牢性が大きな懸念事項です。典型的なカスコードSiCJFETは、この点で優れた特性を備えています。ピンチオフ効果についてはすでに説明しましたが、飽和電流は負の温度係数で制限されます。

過電圧の場合、SiC JFETゲート-ドレインダイオードが導通し、内蔵ゲート抵抗に電流が流れ、JFETチャネルがオンになって過電圧がクランプされます。この場合も、SiCダイの固有の高温定格により、ダイのサイズが比較的小さい場合でも、かなりのアバランシェエネルギーレベルに対して十分な安全マージンが得られます。追加の信頼性の尺度として、すべての部品は最終テストで100%アバランチェ領域にさらされます。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

オンセミ メーカー情報Topページへ

オンセミ メーカー情報Topページへ戻りたい方は、以下をクリックください。