データセンターの電源およびテレコム整流器でのシリコンカーバイド(SiC) FETの使用

5Gネットワークの導入により、世界中で大規模な増築が予想され、必要な電力を供給するために多くの高品質の電気通信整流器が必要になります。効率の向上、運用コストの削減、BOMコストの削減等のニーズを応えるために、WBG(ワイドバンドギャップ)ソリューションへの関心が新たに高まっています。これは熱損失を最小限に抑えつつ、サーバー電源の効率をこれまで以上に高めようとする取り組みにも共通しています。デジタル経済、ビッグデータ、IoT、人工知能に電力を供給するハイパースケールデータセンターは、現在30KWを超えるサーバーラックと高度に洗練された冷却管理システムで動作しています。

より大きなアンテナアレイ(最大64送信/64受信)を備えた5Gネットワークは、100〜1000倍のデータレートを実現し、IoTを形成する何兆ものデバイスに対応するために、さらに多くの電力を必要とします。各基地局に必要な電力を削減するために多くの技術改良がおこなわれましたが、それ以上の数の基地局が必要になる可能性があります。これらの基地局の電源は、高度な電力管理方法に対応するために、待機状態から全負荷状態まで、これまで以上に厳しい効率要件を満たす必要があります。

SiC FETの新製品により、これまで達成できなかった効率目標を達成することが可能になっているので、この記事では主なトポロジーとデバイスの能力を検証します。ここでは、Siスーパージャンクション、SiC FET、およびGaN FETのすべてが競合するこの分野において、どのようなことが見られるかについて説明します。

基本的な事項

これらのすべての電源装置に共通するのは、力率補正PFCセクションで、出力電圧400Vでほぼ単一の力率でACからDCに整流し、その後にこの400Vをシステム内で使用するための48Vまたは12Vに変換するDCDCコンバーターを備えています。さらに、ポイント・オブ・ロード・コンバーターを使用して、CPUとメモリーバンクに電力を供給します。

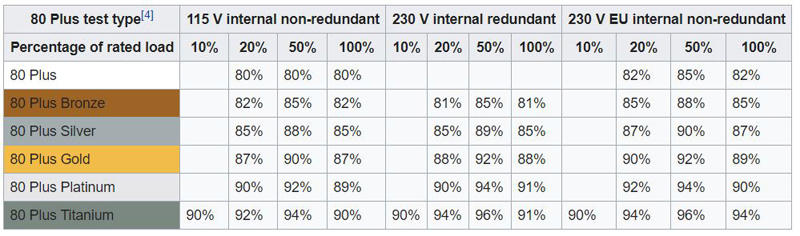

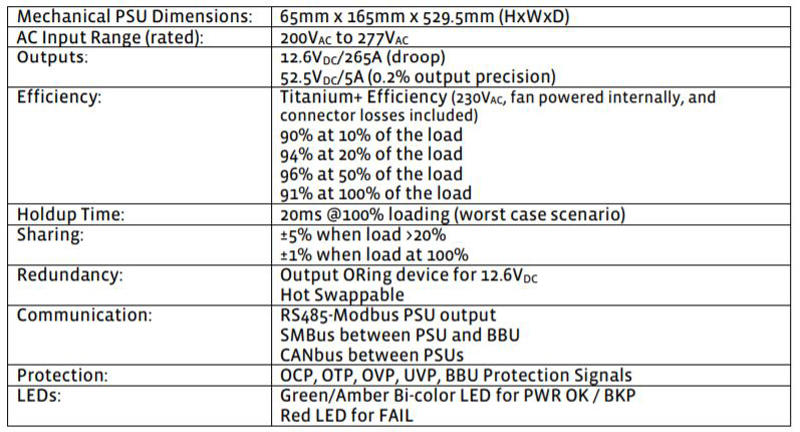

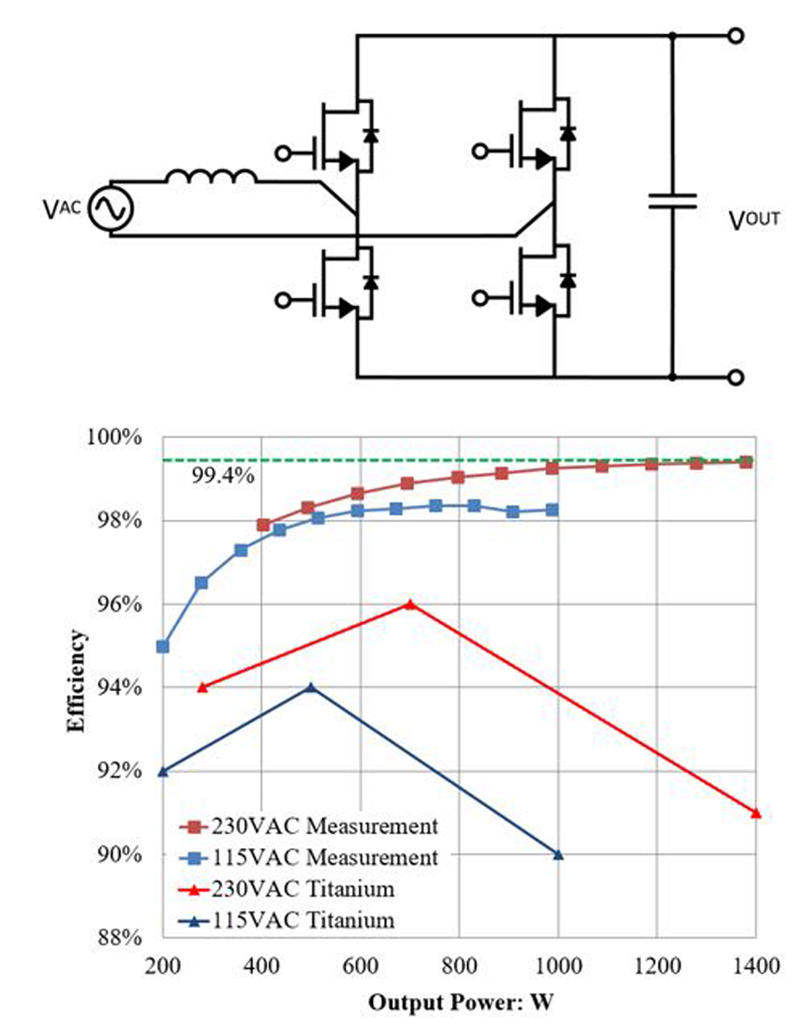

データセンターのサーバー電源の使用プロファイルを調べると、動作寿命の大部分が軽負荷から中負荷であることが明らかになります。したがって、PFCおよびDC-DCセクションは、ピーク負荷動作の熱的制約を満たしつつ、すべての負荷条件で高効率で動作しなければなりません。これは、図1に示すように、コンピューター電源に使用される、よく知られている80Plus規格によって捉えることができます。サーバーは、10%の負荷でも高効率を維持するTitaniumの要件を満たす必要があります。図2は、Open Compute Projectから引用した典型的な仕様を示しており、3.3KWクラスの電源に対するTitanium+要件を特長としています。

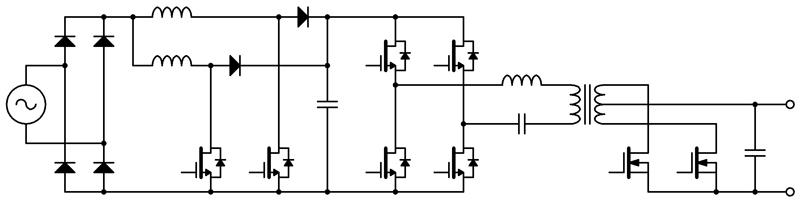

図3は、入力ブリッジ整流器、650V FETとSiC JBS(ジャンクション・バリア・ショットキー) ダイオードを備えたシンプルなデュアル・インターリーブ・ブーストコンバーター(PFC)、およびDC-DCコンバーター用のフルブリッジLLCステージを備えた典型的な電源アーキテクチャーを示しています。入力EMIフィルターは図示しておりません。 PFCステージには、65〜150kHzの一般的なスイッチング周波数が使用されています。ここではインダクターを30kHzではなく、ピーク電流にすることができるため、電力密度の必要性は低い周波数での高効率とトレードオフされています。このため、65kHz~150kHzで高速スイッチングをおこないながら、高効率を維持するために、SiC JBSダイオードを用いたSi スーパージャンクションMOSFETを使用しています。高度に進歩したスーパージャンクションMOSFETは高速にスイッチングでき、SiCショットキーダイオードはMOSFETのターンオン損失を最小限に抑えることができます。

入力ブリッジ整流器の後には、インターリーブPFCステージとフルブリッジLLCステージがあります。

回路のLLC部には、650V MOSFETも一般的に使用されます。この回路はZVS(ゼロ電圧スイッチ)動作を維持し、ターンオフ電流を低減しているため、損失が大幅に小さく、100〜500kHzでの高周波数での動作が可能にとり、トランスを小型化にすることができます。二次側では、高周波の二次交流電圧を整流してDC電圧出力を供給する為に、とても低いオン抵抗の80-150VシリコンMOSFETを使用しています。使用されている650V FETは、いくつかの動作条件でZVSがなくなった場合でも、ボディーダイオードのリカバリーが破壊的でないように選択されています。

半導体デバイス

トランジスターを中心に、PFCやDC-DCユニットの高電圧側では、650Vクラスのデバイスが一般的に使用されます。表1に、シリコン、GaN、およびSiCデバイスの現在とそれらの関連する特性の概要を示します。チップサイズに換算されるRdsAの観点からは、SiC FET(SiC JFET RdsA)が最も優れた選択肢です。すべてのワイドバンドギャップデバイスは、シリコンスーパージャンクションに比べて、ボディーダイオードのリカバリー特性が優れています。ただし、アバランシェエネルギーを処理できるのは、SiCおよびシリコンデバイスのみです。エンハンスメントモードGaNデバイスは、Vthが低く、速度と狭いゲート電圧範囲と相まって、駆動が困難です。

|

Spec |

SIC Cascode UJCO6SOSK |

SiC MOSFET |

E-mode GaN |

Si Superjunction |

|

Rpm mohm-cm2 |

0.75 |

3.5 |

6.6 |

10" |

|

Rds*Eoss mohm-uJ |

255 |

600 |

350 |

462 |

|

Vth (V) |

5 |

4.5 |

1.3 |

3.5 |

|

Avalanche |

Yes |

Yes |

No |

Yes |

|

Gate voltage rating(V) |

±25 |

±22/-4 |

+/-10 |

+/-20 |

|

Diode behavior |

Excellent |

Excellent |

Excellent |

Poor |

表1:650Vトランジスターオプションの基本技術比較

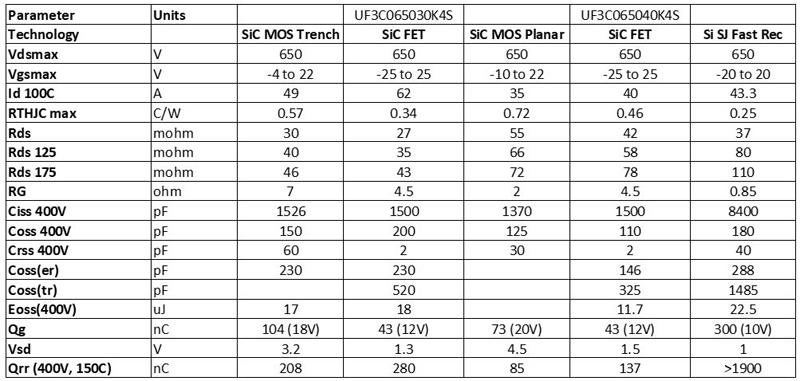

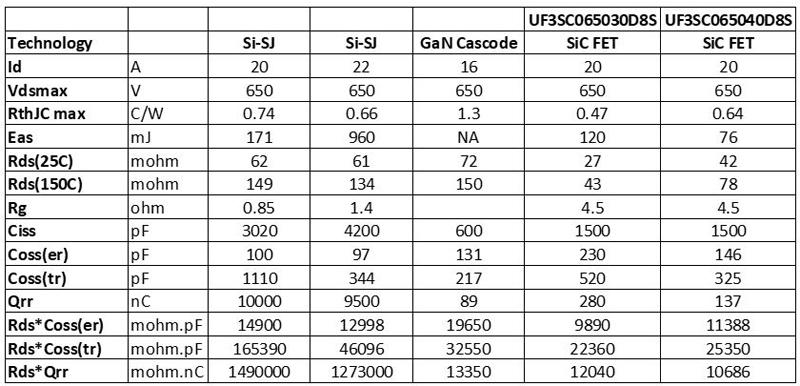

表2は、一般的に使用されているTO-247パッケージのいくつかの業界同等製品の比較を示しています。シリコンスーパージャンクション(Si SJ)デバイスとUnitedSiC は、0〜10Vドライブで駆動できます。 SiC MOSオプションは、異なる電圧が必要です(例:-4Vから18V)。 SiCデバイスはすべて、より低い入力容量(ゲート電荷)、大幅に低減されたダイオードのリカバリー電荷Qrrを提供します。 SiliconスーパージャンクションとSiC FETのボディーダイオード導通損失は、SiC MOSFETよりも低くなっています。

表3に、DFN8x8フットプリントの類似デバイスの比較を示します。シリコンSJ、SiC FET、およびGaNデバイスは、すべて標準のシリコンゲートドライブで駆動できます。 UnitedSiC FETは非常に低いオン抵抗を提供します。各デバイスの150℃のRDS(ON)の比較をするには、下3行の性能指数を使用して行うのが最適です。 WBGソリューションは、特にRds * Coss(tr)およびRds * Qrrに対して、より優れた性能指数を提供しています。

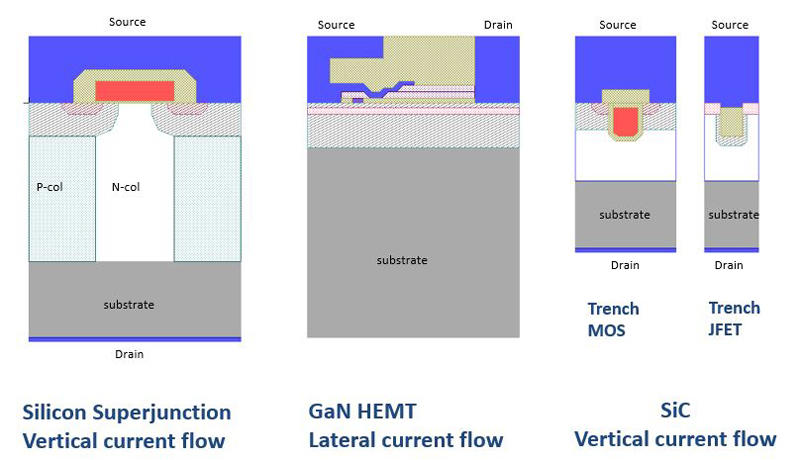

図4は、SiC、GaN、シリコンスーパージャンクションFETの一般的に使用される構成の断面アーキテクチャーを示しています。 GaN のHEMTは水平方向デバイスですが、他のデバイスは垂直方向の電流デバイスです。垂直方向に電流を流すことで、ソース端子とドレイン端子がウェハ上面ではなく、ウェハーの対抗面にあるため、高電圧デバイスをよりコンパクトに実装できます。 GaN のHEMTでは、導通は2DEGチャネルに限られますが、SiCデバイスは短い表面チャネルを使用していますが、ほとんどは電流を運ぶためのバルクとして使用しています。 SiC JFETにはバルクチャネルがあり、その垂直と共に、単位面積あたりの抵抗値(RdsA)が最も低くなり、チップサイズを小さくすることができます。その後に低電圧Si MOSFET(抵抗値を10%を増加させる)でカスコードされて、SiC FETが形成されます。

デバイスが向上すると、デバイスの出力容量Cossを充電する負荷電流によって、最終的にスイッチ速度の限界が設定されます。所定のオン抵抗のCoss(tr)の値が低くすると、最速のスルーレートがと400Vに達するまでの最短の遅延時間が得られます。表3から明らかなように、SiC FETはこの点で優れており、高周波電力変換に適しています。

Qrrに関して、WBGオプションのすべては、シリコンスーパージャンクションデバイスに比べてはるかに優れたパフォーマンスを提供します。したがって、CCM(連続電流モード)トーテムポールPFCのように、回路がハードスイッチターンオンを使用する場合は常にこれらのデバイスが選択されます。これらの回路がフリーホイーリング状態でボディダイオードの導通を使用する場合、オン状態による電圧低下が導通損失につながります。したがって、これらの損失を減らすためにFETチャネルをオンにして、同期導通が一般的に使用されます。通常、電流の反転を検出してからFETチャネルをオンにするまでには遅延があり、この時間が高周波ではスイッチング周期のかなりの割合になります。例えば、スイッチング周波数が100kHz(10us周期)の場合、ダイオードが導通する100nsのデッドタイムはほとんど問題になりません。ただし、1MHz(1000ns周期)のスイッチングサイクルでは10%になります。したがって、低Qrrと低ボディーダイオードの導通損失VSDは有用な特性であり、QorvoのSiC FETは両方を提供します。

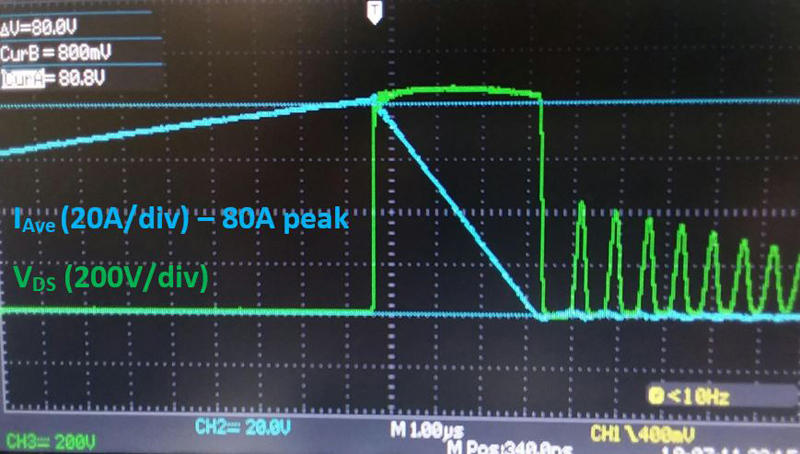

デバイスの堅牢性に関して、すべてのSiCデバイスは優れたアバランシェ機能を備えており、コンバーターのシステム信頼性を高めます。チップサイズが小さいにもかかわらず、特に大電流レベルでは、スーパージャンクションFETの能力を超えることがよくあります。 GaNデバイスはアバランシェを処理できないため、この動作領域を回避するために高耐圧で設計されています。図5は、実用的な必要性をはるかに超える80Aのピークアバランシェ電流(青)を処理するUnitedSiC製の40mΩ、650VのSiC FETのスコープキャプチャーを示しています。ブレークダウン電圧は800V(緑)を超えているのがわかります。

SiC JFETのサイズが小さいにもかかわらず、デバイスは80A以上のアバランシェ電流にも故障なく処理しています。

ゲートドライブの考慮事項

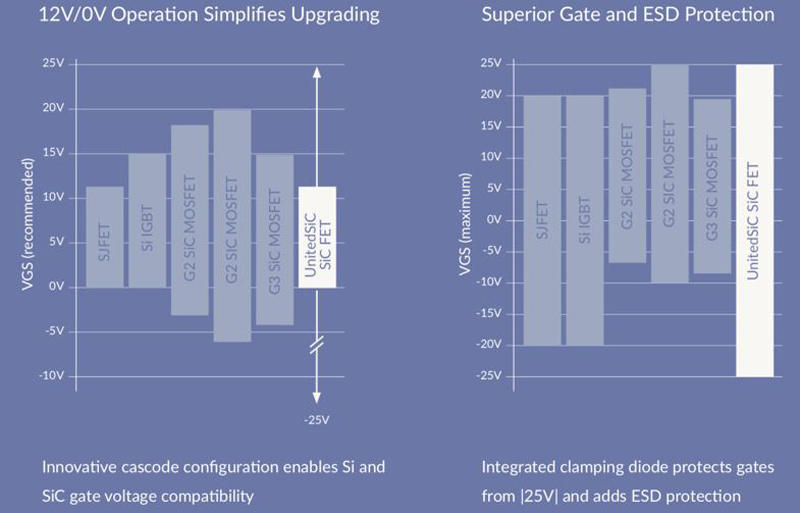

SiC FETを使用すれば、ゲートドライブを簡素化でき、これは低電圧MOSFETのVTHしきい値が5V、VGS(MAX)定格が+/- 25Vであるからです。 0〜10V(または12V)のシリコンスーパージャンクションMOSFETのように駆動することができます。図6は、さまざまな技術の推奨ゲート駆動電圧と対応するゲート絶対最大定格の比較したものです。 SiC MOSFETは、通常、負および正のゲートドライブを必要としており、ゲート電圧に20〜25Vの合計スイングが必要です。多くの場合、ゲート電圧は絶対最大定格に非常に近いため、ゲートスパイクに注意する必要があります。ゲート電圧のスイングが大きいと、高い周波数でかなりのゲート電荷損失が生じる可能性があります。さらに、VTHヒステリシスの問題を管理するために、ゲート駆動電圧レベルについて、メーカーの推奨事項に注意深く従う必要があります。 SiC FETはこの点で柔軟性があり、ゲート電圧レベルのそのような注意深い制御を必要としませんが、SiC MOSFETと互換性のあるゲート電圧で駆動することもできます。

SiC FETは他に類を見ないほど汎用性を持っています。

GaNエンハンスメントモードデバイスは、一般にVthが低く、ゲート電圧範囲が狭いため、絶対最大VGS制限に非常に近いことがよくあります。これには、スイッチへの損傷を避けるために、特殊なドライバーと注意深いレイアウトが必要です。 カスコードオプションは、これらの問題のいくつかを回避できます。エンハンスメントモードデバイスのゲート電圧スイングが小さいほど、高周波でのゲート損失を低減するのに役立ちます。

すべての場合において、デバイスはより高速で使用されるため、デバイスを高いdV/dtで維持することはますます困難になります。電力ループとゲート駆動ループのインダクタンスからのゲート電圧スパイクの管理も同様です。ソースケルビンpinを使用したパッケージの導入は役立ちましたが、この記事の後半で他のオプションについて説明します。

回路トポロジ– PFCステージ

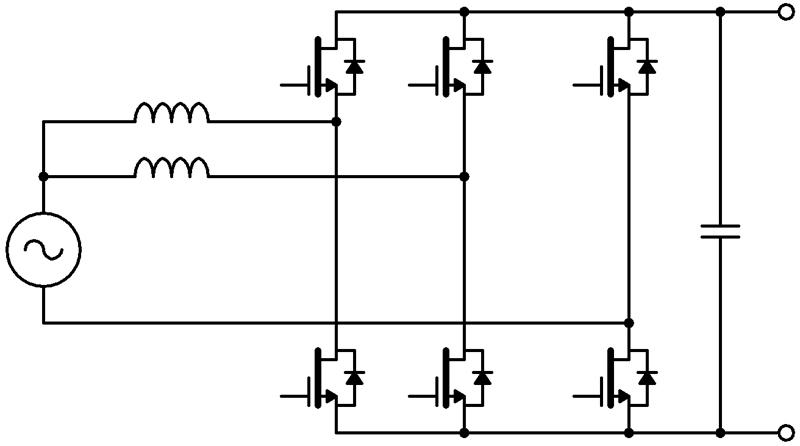

図7は、トーテムポールPFC(TPPFC)回路、およびUJC06505K SiC FETを使用した1.5KWのQorvoデモボードにおいて100kHzで測定された効率を示しています。この回路は、入力ダイオードブリッジとSiCで構成されるPFCの導通損失を無くします。この場合、コンバーターはCCMモードで動作し、デバイスはハードスイッチングされます。

図8は、結合インダクターを使用して設計できるインターリーブTPPFCを示しています。この回路は、連続電流モードで使用できます。または、ターンオン損失がなくなるため、臨界導通モードではるかに高い周波数で動作できます。 SiC FETを使用すると、効率を犠牲にすることなく非常に高い電力密度を実現できますが、リップル電流が高く電流ゼロ交差点を検出する必要がある場合、制御とおよび磁気設計の複雑さが増します。

2つの高速スイッチングと1つのライン周波数スイッチング・ハーフブリッジを採用しています。結合インダクターアプローチにより、臨界導通モード動作を使用できるため、周波数を大幅に増加させることができます。

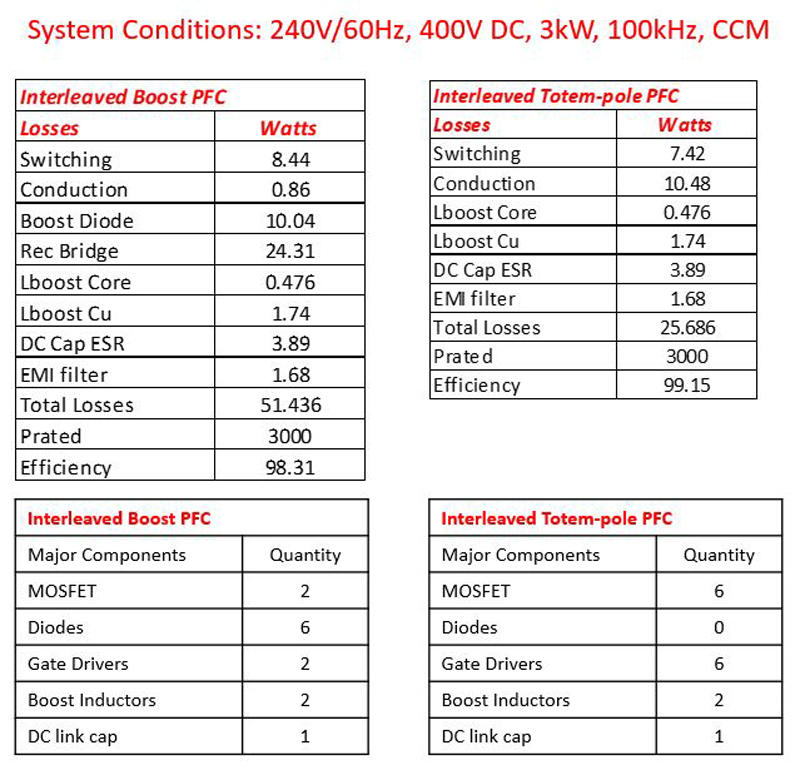

表4は、図1に示されているインターリーブPFCトポロジーと図8のインターリーブトーテムポールPFCを使用した損失の内訳の比較を示しています。どちらの場合も、各スイッチを100kHzで動作させる3KWクラスのコンバーターを想定しています。インターリーブは、インダクターのリップル周波数が200kHzに見えることを意味します。トーテムポールPFCは損失を大幅に削減(51.4Wに対して25.7W)し、Titaniumの純効率の目標を達成することを可能にします。これは、ブリッジ整流器からの24.3Wの損失を排除することによって推し進められます。この例で使用されているトーテムポールPFCには、さらに4つのFETとゲートドライブ回路が必要です。

電流交差の検出を必要としない別の方法は、追加の補助スイッチを使用して、ターンオン時にゼロ電圧遷移を実現することです。ターンオン損失とターンオフ損失の両方を排除する補助共振整流極(ARCP)などの共振技術を使用して、同様またはより良い結果を得ることができます。ただし、より高度な技術を使用した場合の価格性能は、5KWをはるかに超える電力レベルでのみメリットがあるようです。

回路トポロジ– DC-DCステージ

出力電圧が固定されているため、図1のフルブリッジLLCコンバーターは優れた電力密度と効率を提供し、現在、より高い電力レベルで業界の主力製品となっています。電力レベルが低くなると、ハーフブリッジLLC実装を使用できます。 12V出力での高電流のアプリケーションでは、100〜500kHzの範囲の周波数が一般的に使用されており、損失低減の主な取り組みは二次側のトランスおよび、二次側のMOSFETを改善することが主になります。

高電圧のFETの場合、オフ状態からダイオード導通へのVDS遷移では、出力容量を充電する必要があります。これをすばやく行うには、低いCOSS(TR)が必要です。ただし、ボディーダイオードの導通による損失を減らすために、FETを駆動する前に、デッドタイムを最小限に抑える必要があります。オン状態では抵抗が低いため、導通損失が最小限に抑えられ、ほとんどのスーパージャンクションスイッチとWBGスイッチのEOFFが低いため、スイッチング損失を最小限に抑えることができます。

近い将来の展望

シリコンスーパージャンクションFETの改善は続いていますが、今後数年間におけるSiCとGaNデバイスの改善レベルは、シリコンで達成できるものをはるかに上回っています。 RdsAの改善(2〜3年ごとに30〜50%の改善)に加えて、パッケージテクノロジーの多くの改善が期待されます。一番の挑戦は、低インダクタンス化と、小さな表面実装パッケージでのより効率的な熱除去です。

考えられる1つの方法は、直接表面実装、もしくはPCBへ埋め込んで、設計されたハーフブリッジ要素への移行です。これにより、PCBレイアウトが簡素化され、インダクタンスを下げ、ゲートループ回路の改善が可能になります。

もう一つの方法としては、ドライバーとパワーデバイスを統合する、つまり単一のドライバー+スイッチ、またはハーフブリッジ素子として統合することです。ほとんどのSiCおよびGaNデバイスは、独自の駆動電圧レベルと回路を必要とするため、この複雑さはパッケージ化された、集積化された製品に吸収されることにより、ユーザーにとってより簡単になります。さらに、各デバイスを最大限に活用することができます。これは間違いなくシステムコストと電力損失の大幅な節約につながり、WBGの採用を促進します。

上記のとおり、35m、1200V SiC FETを使用した統合ハーフブリッジゲートドライブを備えたSIPハーフブリッジは、このシリーズの以前の記事で説明しました。表面実装オプションはさまざまなサプライヤーから出てきており、その傾向は加速するでしょう。

650V-WBGスイッチのコストは急速に低下しています。 Qorvo 650V FETは、今後2年以内にシリコンと同等の価格に近づくと予想されています。この点においても、使いやすさに加えて、サーバーおよびテレコム電源アプリケーションでのWBGデバイスの展開を急速に加速することが期待されています。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

オンセミメーカー情報Topページへ

オンセミメーカー情報Topページへ戻りたい方は、以下をクリックください。