超高耐圧SiCとSupercascodes

シリコンIGBTやIGCTテクノロジーよりも、システムのソリューションコストと動作損失が大幅に低い高電圧スイッチテクノロジーを必要とする新しいアプリケーションが登場しています。これは、ソリッドステートトランス、MWモータードライブから、スマートグリッドアプリケーション(FACTS、STATCOM)やHV DCブレーカーに至るまで、幅広い範囲に及びます。 SiC MOSFETは、近い将来この分野をブレークする優れた選択肢と考えられており、オンセミは、ワイドバンドギャップ(WBG)の高電圧スイッチが、加速的に市場で普及できるように、独自のアプローチを提供しています。このアプローチはSupercascodeと呼ばれます。このアプローチとその実証された性能を、シリコンテクノロジーとシリコンカーバイドMOSFETテクノロジーを使って比較します。

SiCデバイスとモジュール

この10年間で、高耐圧SiCデバイスには多くの進歩がありました。理論的には、SiCデバイスは、シリコンデバイスの最大電圧定格の少なくとも10倍に達するように開発できます。これに沿って、最大15KVの単一のSiC MOSFET、さらには最大27KVのSiC IGBT等の多くのデモンストレーションがおこなわれています。6.5KV-10KV範囲のMOSFETがモジュールベースの製品として登場しています。 SiC MOSFETが3.3KVを超えるシリコンIGBTと比較して劇的な損失低減を提供することは十分に実証されています。

10-25KV電圧のSiC IGBTの場合、キャリア寿命の向上と制御、超厚エピタキシャル層の成長、デバイスの信頼性と最適な特性の課題が研究されており、製品化にはまだ5〜10年かかります。

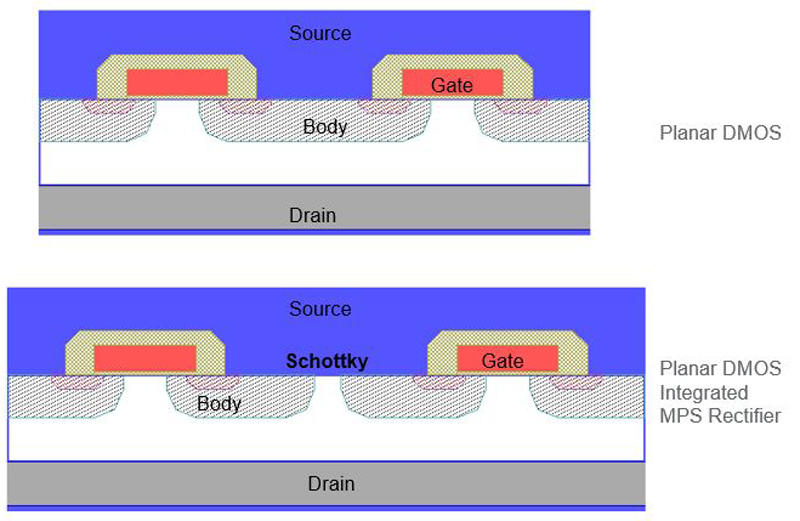

3.3KVを超える分野において現在使用されている、もしくは開発されている主なデバイス構造は、プレーナMOSFETと、図1に示す統合型P-i-Nショットキー(MPS)ダイオードが組み込まれたMOSFETです。後者のデバイスは、モジュール内にSiC ショットキーダイオードを追加する必要がないため、MOSFETを実装するためのスペースを確保でき、各セル内にショットキー領域を追加するためのチップサイズの増加が少ないため、使用可能な定格電流を増加させることができます。しかし、ターゲットしているアプリケーションは高電流定格が必要とされるため、0.5〜1cm2のアクティブ領域を備えた比較的大きなデバイスが必要であり、SiCで高い生産歩留まりを実現することは困難です。

このようなデバイスの多くは、所望の電流定格を達成するためにモジュール内で並列接続する必要があり、各チップはバス電圧にてスイッチングします。

高耐圧デバイスの重要な課題の1つは、エピタキシャル層が厚いほど、最初のエピタキシャルウェーハに多数の欠陥が発生することです。これらの厚くて軽いドーピング層はドーピングレベルが10 14cm3レベルに達すると、厳密なドーピング制御を維持することが難しくなるため、ドーピングバリエーションをたくさん持つことになります。また、厚みの増加に伴い、エピタキシー工程中に使用される消耗品のコストも高くなります。現在の最新技術では、3.3KVデバイスまでの30umエピタキシャル層が高品質に実現されており、今後数年間で生産品質に到達するために6.5kV~10kV(50~90um)層の強化が進められています。定格が1.7KV以下のエピタキシャル層は、6インチ4H-SiC基板上で非常に高品質でタイトなパラメーター分布が実現されており、現在市場で使われています。

超高電圧スイッチをパッケージングするとき、多くの興味深い課題が浮かび上がります。 1つのスイッチが5KVバス電圧で動作し、25nsでスイッチオフする場合、dV/dtは200V/nsになります。 10pFの浮遊容量(たとえば、チップドレインからベースプレートまで、またはゲート回路の絶縁バリアを挟んで)は、チップあたり2A(C * dV/dt)の変位電流が発生させます。高出力モジュールは多くの(10〜20)のチップを並列に配置する傾向があるため、この問題は非常に深刻になる可能性があります。これらの漂流電流により、さらなる損失を引き起こし、低電圧ゲート駆動電子機器の重大な誤作動問題を引き起こす可能性もあります。過度の変位電流の流れは、モジュール内および外部配線、回路の絶縁を弱める可能性もあります。

10KV定格のデバイスでは、10KVはデバイスの終端の上部にある1mmのゾーンを横切って落下します。エアポケット、部分放電、およびバスバーとボンドワイヤーからこのフィールドの近傍の破壊的な電位を回避するために、モジュールの製造時にデバイスのカプセル化と清浄度に非常に注意を払う必要があります。スイッチをベースプレートから隔離するために厚いセラミックも必要であり、これにより熱抵抗が増加します。たとえば、15KVデバイスに単一のセラミックDBCを使用するには、1mm以上のAINの厚さが必要があります。セラミック上のトレースのフィールド分布は、モジュール内のチップからベースプレートへの部分的な放電と最終的な壊滅的な短絡を制御するために適切に管理する必要があります。

Supercascodeとは?何故これが必要なのか?

オンセミは、複数の低電圧デバイスを直列接続するSupercascodeコンセプトを使用して、単一のゲートドライバーで動作する高電圧SiCデバイスを開発しました。このアプローチの背後にある基本的なロジックを検討していきましょう。表1は、1cm2 SiC JFETの抵抗値とブレークダウン電圧定格を示しています。 6500Vのデバイスを並列に使用して6500V、12.5mΩモジュールを構築する例を考えてみましょう。それには、並列に接続された1cm2の面積を持つ4個のチップを並列に接続する必要があります。あるいは、1cm2の3mΩ、1700Vのチップを4個直列に配置することで同じ抵抗値を実現することができます(3x4 = 12mΩ)。つまり、直列ソリューションは本質的に同じ数のSiCの量を使用しますが、低電圧デバイスの方が明らかにコストが低く、より高い歩留まりと、より良いパラメーター分布で、製造を容易にすることができます。

|

BV Rating |

JFET RdsA |

|

Volts |

mΩ-cm2 |

|

1700 |

3 |

|

3300 |

12 |

|

6500 |

50 |

|

10000 |

120 |

表1:1700Vから30KVまでのSiC JFETのオン抵抗の比較

4個直列接続された1c㎡のチップは、4個の6.5kVの並列接続されたチップと同じ抵抗を持つことに注意してください。これがSupercascodeのアプローチの基本ロジックです。

同じ概念をSiC MOSFETで使用することができますが、各低電圧モジュールにはそれぞれ独自の同期ゲートドライブが必要となります。これではより複雑さが増します。 Supercascode方式では、直列チェーンの下部にある1つの低電圧MOSFETが直列スイッチ全体を制御します。これにより、Supercascode方式のゲートチャージ要件は、並列接続されたHV MOSFETや直列接続されたHV MOSFETモジュールを駆動するのに比べて、はるかに低くなります。表2は、Supercascodeモジュールの特性と、SiC MOSFETを並列接続した同等のモジュールの特性を比較しています。

|

Module Approach |

Conventional |

Supercascode |

|

|

SIC Chip Technology |

Die |

6.5kV MOSFET Chip |

1.7kV JFET Chip |

|

RDSA |

63mΩ-cm2 |

3m0-cm2 |

|

|

Die Size |

8.33 x 8.33 mm2 |

7.7 x 7.7 mm2 |

|

|

Die Max. Ron @ RT |

160mO |

5.5mf2 |

|

|

Half-Bridge Module Technology |

Max. Ron @ RT |

20mO |

20ma |

|

Switch Configuration |

8 dies in parallel |

5 JFETs (each has 2 dies in parallel) in series |

|

|

Total Die Count |

16 |

20 |

|

|

Total SiC Area |

1.110 mm' |

1.186 mm-' |

|

|

Module Features |

Typical Vth @ 150*C |

2.0V |

3.7V |

|

Practical Gate Drive |

-5V to +20V |

Standard 0V to +12v |

|

|

Total Gate Charge Og |

2360 nC |

100 nC |

|

|

Anti-Parallel Diode |

Built-in |

Built-in |

|

|

High Orr |

Low Oc |

||

|

Knee voltage: > 2V |

Knee voltage: 0.7V |

||

表2:Supercascodeモジュールと、ショットキーダイオードを内蔵したSiC MOSFETを並列接続したモジュールとの比較。ゲートチャージの違いに注目してください

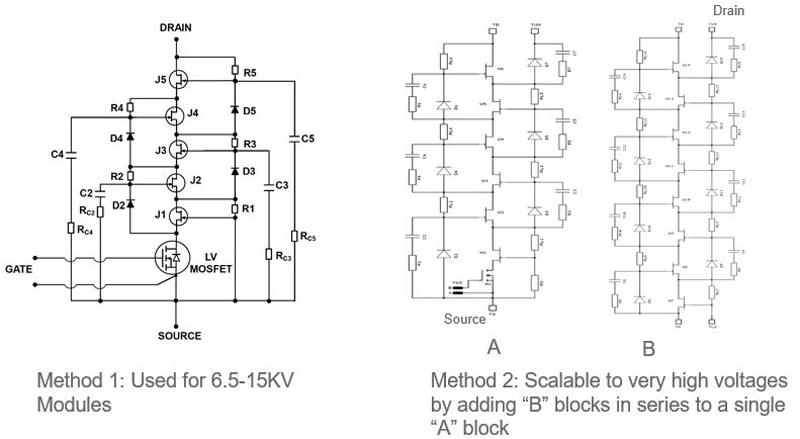

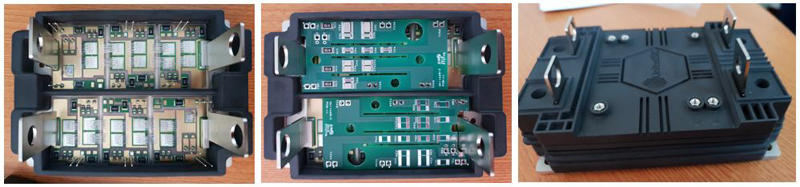

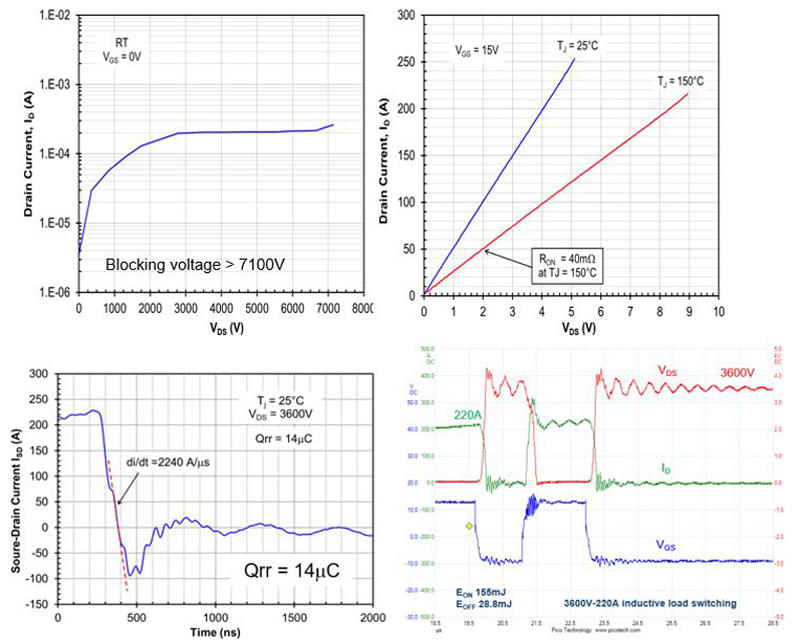

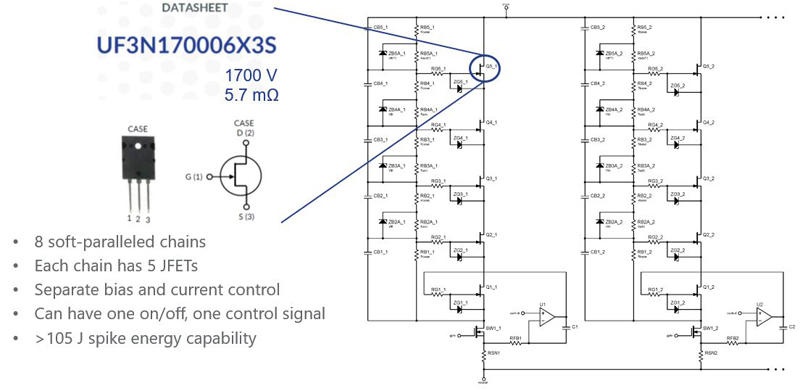

Supercascodeには多くの実装回路が考案されていますが、図2はオンセミによって開発された2つの回路を示しています。このモジュールには、図3に示すように、モジュール内に埋め込まれたパッシブバランスネットワークが必要です。損失はSiCJFETによって支配されるため、効率的に熱を除去するためにDBC(Direct Bonded Copper)基板上に配置されます。他のネットワークコンポーネントは、この層の上のPCB層にあります。図4は、オンセミで開発されているSupercascodeモジュールの電気的特性を示しています。このデバイスは必要な電圧をブロックし、オン抵抗は20mΩ(25℃)であり、第三象限のニー電圧がSi MOSFETからわずか0.7Vであり、直列のJFETの19mΩ抵抗が続くため、SiC JBSダイオードは必要ありません。ダイオード回復電荷であるQRRは非常に低く(14uC)、温度に依存しません。ハーフブリッジスイッチング波形は、3600V-220Aで非常に低いEON(155mJ)およびEOFF(28.8mJ)スイッチングを示しています。

各段に同じコンデンサーを備えた2番目の回路(b)は、最大40KVのスイッチで使用されています。

電力の大部分はDBC基板上にあるSiCカスコードJFETで消費されます。バランスネットワークは、電力消費が少ないのでPCB基板上に配置されています。

ハーフブリッジモジュールは、非常に低い導通損失とスイッチング損失を特長としています。 Supercascodeのリカバリー特性により、Qrrは非常に低くなっています。

表3に示すように、電力損失はIGBTを使用した場合よりも劇的に低くなります。以降の段落では、これらの低損失がさまざまなアプリケーションに与える影響を調べます。

Supercascodeは、スイッチング損失が低いため、10倍の周波数で使用することができます。

HVスイッチのアプリケーション: 中電圧ソリッドステートトランス

ソリッドステートトランスは、一般的に中・高電圧のAC入力(例えば4160V AC、13.8KVAC)から、分厚い60Hzトランスを使用せずに、より低電圧出力に変換します。基本的な概念を図5に示しており、AC電圧が最初に整流され、その後に5〜100kHzの範囲の高出力高周波ACに変換されます。より小型の中・高周波トランスによって、2次電圧を低減し、これを整流して低電圧DCバスを供給することができます。この電圧は、自動車の充電や低電圧のモータを管理するためのDC-ACインバーターを駆動に使用することができます。ソリッドステートトランスは一般的な60Hzトランスに対して僅かなサイズで、非常に高い電圧で電力の分配し、使用時に低電圧へ変換することができます。これにより、電力を分配に電流が減り、銅の重量とコストが減り、さらに損失も低減されます。これはメガワットの電力レベルで特に効果的であり、例えば、250〜350 kWで8〜10台の自動車を充電する必要があるDC高速充電ステーションや、大型船で、低AC電圧を配電するときに発生する銅損を減らす場合に有効です。

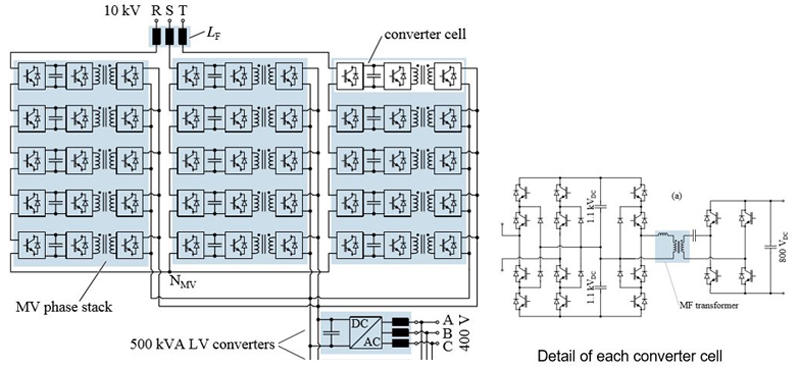

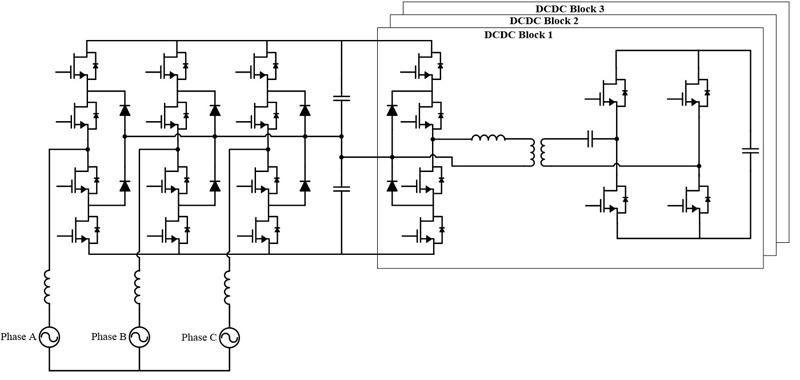

1次側整流電圧は6KVを超え、500Hz-1KHz以上のスイッチング周波数が必要な場合、3.3KV-6.5KVクラスのIGBTまたはIGCTを使用することができません。その代わりにユーザーは、7+レベルの1700V IGBTを備えたマルチレベルインバーターアーキテクチャー、または段階的正弦波出力が供給できるようにタイミングが調整された多くのカスコードされた低電圧コンバーターを備えたMMC(モジュラーマルチレベルコンバーター)を使用することを選択できます。図6にモジュラーマルチレベルコンバーターの例を示し、コンバーターの各段は、1次側に3レベルの1700V IGBTモジュールを使用しています。図7は、10KVスイッチを使用した3レベルSiCを構成した場合を示しています。明らかにSiC構成は、このようなDC-ACコンバーターのアーキテクチャーと制御を簡素化でき、比較的高い周波数で動作させることができます。

カスコード接続された各コンバーターセルの中に、1次側に3レベルの1700Vモジュールがあります。これらすべてのスイッチとすべてのコンバーターは、必要な出力正弦波を供給するために制御する必要があります。

制御の複雑さと高電圧デバイスの数が大幅に削減されています。小型のトランスを使用するには、スイッチング周波数をシリコンソリューションの10倍にする必要があり、熱の管理が複雑にならないように、損失を管理可能な状態に保つ必要があります。これこそがHV SiCデバイスが優れている点です。

メガワットクラスモータードライブ

DOEがまとめたアメリカの電力使用の調査によると、全発電電力の14%がMWクラスの産業用モータードライブによって消費されています。これらのモータを直接グリッドに接続の代わりに可変速ドライブで使用することで、運転コストを大幅に削減することができます。これらのモータードライブは、動作電流を削減して銅線のサイズと損失をうまく扱うために、より高いバス電圧で動作する必要があります。 500 Hz〜2kHzで動作するSiベースのインバーターを使用する代わりに、SiCベースのインバーターを10倍の高い周波数で使用でき、冷却の必要性とシステムサイズを大幅に削減できます。

システム設計者は、最後のセクションで説明したシリコンを使用した同じマルチレベルコンバーターのアーキテクチャーか、SiCモジュールを使用したよりもシンプルな2レベルまたは3レベルのソリューションのいずれかを選択することができます。 またSiCを使用して動作電圧を上げることが可能で、発電や配電の上流でのコストを削減することができます。しかし、SiCの能力を十分に活用するためには、モーターの設計と技術面で大きな開発が必要です。しかし、現在でも電流リップルの低減によるモーターの運転効率の向上や、損失の低減によるインバーターの効率を向上など、SiCのメリットは十分に理解されています。いくつかのアプリケーションでは、SiCを使用することで、より小型の高RPMモーターを使用することが可能になり、ギアボックスが不要になる可能性があります。

高電圧システムの補助電源

上記のすべてのシステムでは、システム制御電子機器(+/-5V、12V、24V)および小型の補助照明や冷却システムのために低電圧が必要とします。高電圧機能を備えた電流定格が小さいモジュールは、中電圧ACからこの電力を簡単化するのに役立ちます。このアプリケーションにSupercascodeコンセプトを応用すれば、スイッチの電圧を簡単にスケールアップすることができます。また、低電力のノーマリ―オフのMOSFETと直列の並べたSiC JFETのノーマリオン特性を利用して、低電力フライバックコンバーターで実証されているように、起動回路を簡素化することもできます。ユーザーは電力レベルに応じて、パワーモジュールを使用するか、市販のJFETコンポーネントを使用して、PCB上でディスクリート構成にするかを選択することができます。

HV DCブレーカー

DC発電とDC負荷の普及に伴い、信頼性の向上、サイズの縮小、アーク放電の懸念の軽減、システム保護のためのインテリジェンスの追加等をするために、機械式ブレーカに代わるソリッドステートサーキットブレーカーをどうように使用するかに新たな注目が集まっています。ソリッドステートブレーカーには可動部がなく、機械的に電流を切断しようとしないため、アーク放電の懸念や接点の機械的摩耗の影響を受けません。共振ゼロ電流交差を強制せずにDC電流を遮断するソリッドステート向けに対する主な価値は、1ms以内で簡単に実行できることです。その後、はるかに小さい切断スイッチをゼロ電流でオンすることができ、ガルバニック絶縁を実現します。この方法により、下流回路とソースが対処しなければならない故障電流の継続時間と大きさが劇的に減少します。

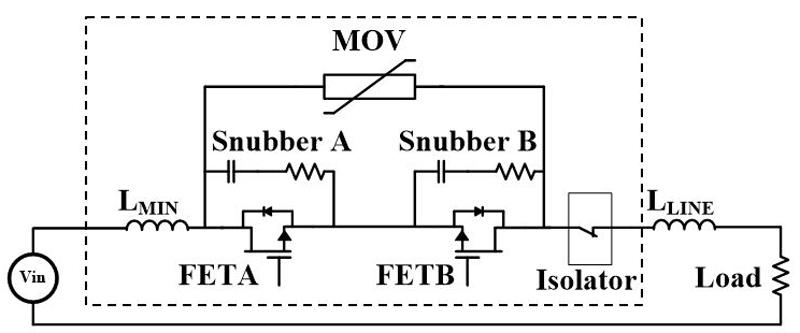

図8は、双方向機能を備えたソリッドステートサーキットブレーカで一般的に使用されるタイプの配置の例を示しています。大規模な電力システムでは、ケーブル配線と負荷インダクタンスが大きく変化する可能性があるため、DC故障電流を遮断するときに、ラインインダクタンスに蓄積されたエネルギーを消費させる必要があります。このエネルギーは非常に大きくなる可能性があるため、図8で並列に使用されているMOVによって消費されます。スナバ回路は、ターンオフ時にdV/dtおよびdi/dtを緩和します。

バック・ツー・バック・スイッチは、どちらの方向にもスタンドオフ電圧を供給します。 RCスナバは、スイッチング電圧の遷移を緩和します。 MOVは、ラインインダクタンスの蓄積された最悪の状態のエネルギーを消費するサイズになっています。 Supercascodeスイッチを使用することで、実質的にあらゆるレベルの電圧または電流を処理することができます。

このアプリケーションで使用されるスイッチの主な要件は、低導通損失、電圧と電流のスケーリングの容易さ、高い故障電流のターンオフ時の堅牢な動作です。ここでもSupercascodeアプローチが効果的です。 SiC カスコードJFETは、オン抵抗の温度係数が良く、温度に対してほぼフラットなVTHを持つため、非常に簡単に並列化できるため、大電流のスケーリングが非常に簡単におこなうことができます。またSupercascode技術を使用することで、電圧スケーリングも簡単となり、1つの共通ソース基準に対して低電圧MOSFETを駆動するだけで、ブレーカの動作を制御することができます。

図9に示すように、シンプルなオペアンプ回路と低電圧MOSFETのSupercascodeを組み合わせて使用することで、ピーク故障電流を最小限に抑えながら、非常に低い挿入損失で高速動作の電流ブレーカーを実現することができます。このタイプの回路は、突入電流を管理し、実際のフォルトが発生した場合にのみトリップするように変更することができます。この例では、電圧スケーリングは直列接続されたデバイスによっておこなわれ、電流スケーリングは並列ステージでおこなわれます。

並列接続された8つの並列で構成され、それぞれに5つの直列接続されたJFETがあります。トリップ電流は、オペアンプの電圧基準を使用して設定できます。電流は図のように、または低電圧MOSFETのVDS(ON)を使用して検出することができます。

結論

SiCデバイスは、中高電圧アプリケーション上でのパワーエレクトロニクスを改善するための優れた候補です。ソリッドステートトランスからメガワットクラスのモータードライブ、補助電源システムからソリッドステートサーキットブレーカーに至るまで、一般的なSiC MOSFETと特にSiC JFETベースのSupercascodeが、非常に魅力的な高性能で簡素化されたシステムを提供することを示しました。これらのアプリケーションの成長は、2020年代のEVブームをはるかに超えて、将来的にSiCベースのパワーエレクトロニクスの成長を牽引することでしょう。

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

オンセミ メーカー情報Topページへ

オンセミ メーカー情報Topへ戻りたい方は以下をクリックしてください。