「リンギング」 「オーバーシュート」 「アンダーシュート」のリスク

基板設計されるエンジニアの方の中には、「発振器の終端方法」で困ったことがあるかもしれません。

本記事ではシングルエンド発振器の終端方法について、詳しく解説していきます。

急激な立ち上がりや立ち下がりを持つクロック信号の場合、単なる配線ではなく伝送線路としてプリント基板(PCB)上のトレースを扱う必要があります。トレースの長さが一定の限度を超える場合、トレースのインピーダンスはソースまたは負荷のインピーダンスにマッチングする必要があります。インピーダンスの不整合が発生すると、伝送線路上で信号の反射が引き起こされ、「リンギング」 「オーバーシュート」 「アンダーシュート」といった信号の歪みが発生する可能性があります。

具体的な終端方法の手引き・ポイント

1.集中定数回路と分布定数回路

・集中定数回路は、クロックソース、PCB トレースまたクロックレシーバーが同じタイミングで応答する

・分布定数回路は、各応答がトレースに沿って遅延を持って伝達される

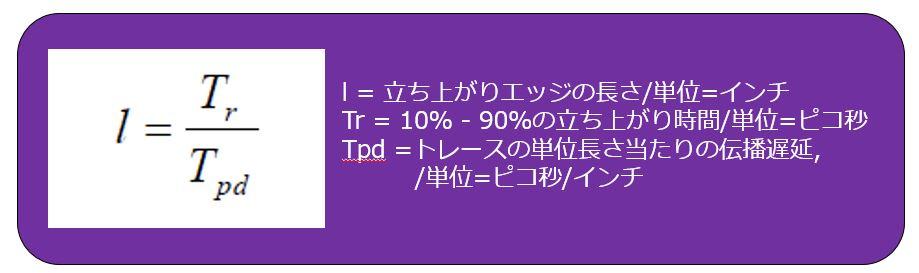

実際、信号が伝搬する際には遅延が生じますので、完璧な集中定数回路というものは存在しません。しかし以下の式1で表されるクロックエッジの立ち上がり実効長とPCB トレース長の比率が1/6 以下であれば、集中定数として考えることができます(終端は考慮する必要はありません)。

例えば、FR-4 のPCB トレースの伝播遅延は、140〜180 ピコ秒/インチの範囲となっています。

Tpd = 150ピコ秒/インチと仮定すると、1 ナノ秒の立ち上がりエッジの実効長は6.7インチとなります。

そのため PCB トレース長が1.1 インチ(立ち上がりエッジ実効長の1/6)以下であれば、回路は概ね集中定数回路と考えることができます。Tr を20%- 80%で定義する場合は、この比率は1/4 に変更してください。

SiTime の データシートには、駆動能力(Drive strength)と負荷容量に対する出力信号の立ち上がり/立ち下がり時間が記載されています。式1 で立ち上がりエッジの実効長を計算の際には、各製品のデータシートに記載されているTr 値table の中で最も低い負荷のオプション(通常5pF)の値を採用してください(レシーバ端の負荷容量はクロックソース端の立ち上がり/立ち下がり時間に影響を与えない為)。

クロックドライバーが伝送線路にクロックエッジを送り込むと、一定時間後にエッジは負荷に到達しますが、負荷のインピーダンス(𝑍𝐿)と伝送線路のインピーダンス(𝑍𝑂)が異なる場合、負荷からソースに向かって信号の一部が反射し信号品質が悪化します。また、ソース端でもインピーダンス不整合が生じると、上記の反射信号の一部がさらに負荷に向かって反射される為、信号品質がさらに悪化してしまいます。

以下のセクションより、単一または複数の負荷を駆動する際に、反射を最小限に抑え、

シグナル・インテグリティー(SI:デジタル信号品質、伝送信号品質)を改善するための終端方法について説明します。

2.駆動する対象(デバイス)がひとつの場合

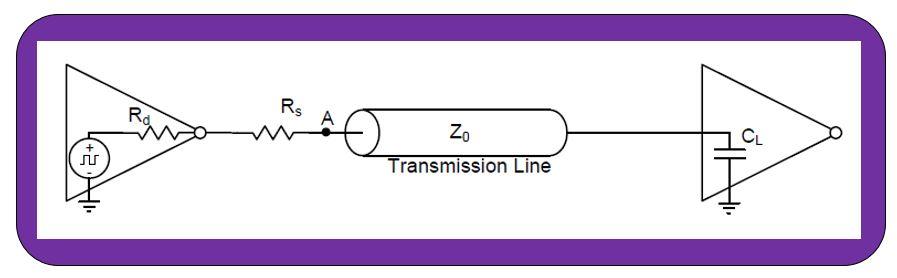

直列終端を使用する場合は、トレース上に抵抗を直列に配置し、出来るだけソースに近くなるようにしてください(下記図を参照)

インピーダンスの整合を取るために、クロックドライバーと直列終端抵抗との出力インピーダンスの合計が、トレースのインピーダンスと等しくなるようにする必要があります。

SiT8208を例に取り、最適な終端抵抗値の計算方法が以下に示されています。

動作電圧が3.3Vであり、デフォルトのドライブ強度により60Ωのトレースを駆動することを仮定しています。

SiT8208のデータシート内では、デフォルトのドライブ強度の設定コードは「F」と規定されています。

このサフィックスに適合する出力インピーダンスは15.3Ωであることが分かります。

この値を式に代入すると、ソース終端抵抗値は、Rs = 60Ω - 15.3Ω = 44.7Ωと計算できます。

通常、レシーバー端の入力インピーダンスは非常に大きく、数メガオームくらいになるため、

レシーバー端ではエネルギーが全く吸収されず、信号全体がソースに向けて反射して返されることがありますが、

上記のようにソースと伝送ラインのインピーダンスが整合しているため、それ以上の反射は発生しません。

また、レイアウトのシミュレーションを実施することを勧めています。

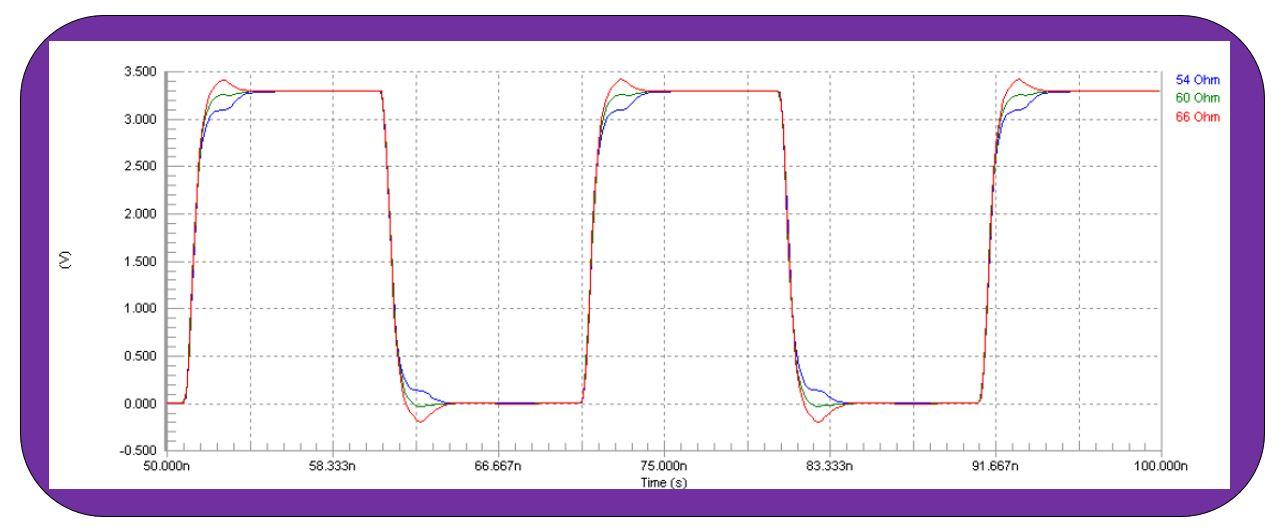

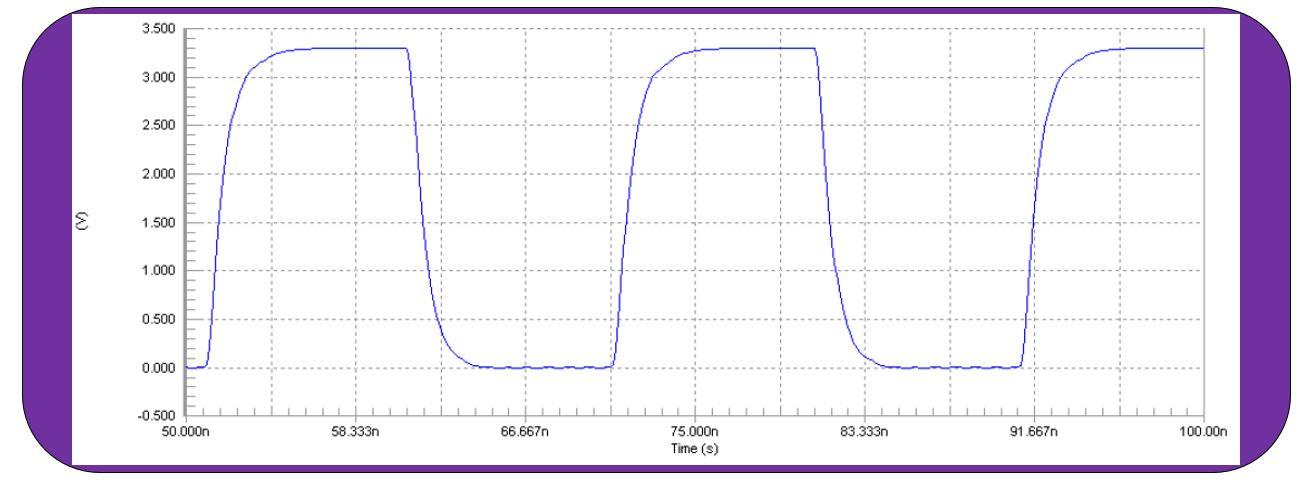

SiT8208が5インチ、60Ωの伝送ラインを駆動する想定したレシーバー端の信号波形が下の図に示されています。

このシミュレーションでは、終端抵抗Rsとして43Ωを選択し、60Ωの伝送ラインとのインピーダンス整合を取っています。また、PCB製造上のばらつきを考慮して、伝送ラインのインピーダンスが+/-10%変動した場合の結果も図に載せています。

※ シミュレーター:Altium Designer社 Signal Integrity Analysisツール

3.駆動する対象(デバイス)が複数の場合

②以外に、PCB上の複数のICが、同一周波数の入力クロックを必要とする場合もあります。

1つのクロック源で複数の負荷を駆動するための1つの方法として、クロックバッファー (複数のクロック出力端子をもつデバイス)の使用がありますが、これは追加の基板スペースと電力を必要とします。

その代替として、1つの出力端子で複数の負荷を駆動する方法があります。

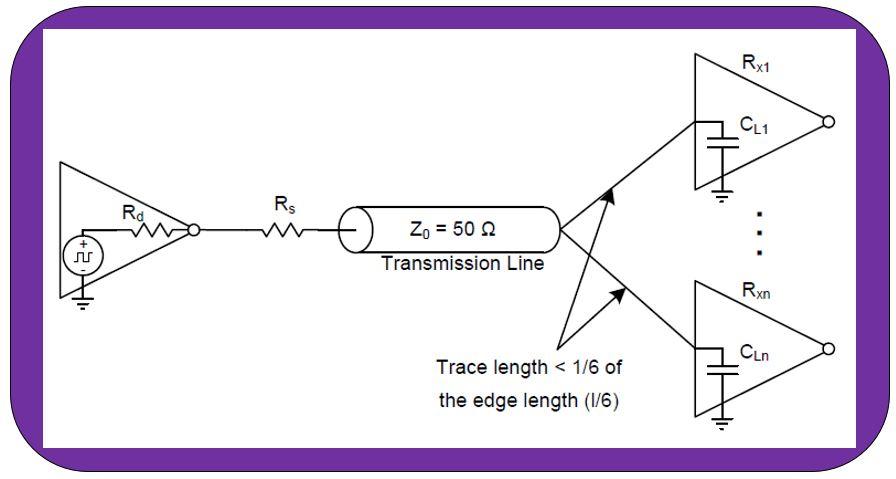

ポイントは、1つの出力端子で複数負荷を駆動するためにレイアウトを伝送ラインから複数負荷への分岐を1つにし(=スター型接続)トレース長をできる限り短くすることです。

これにより、複数負荷を集中定数回路として表現することができます。この方法では、各負荷が十分に近くなるように配置することが必要です(3-1)。

もし、各負荷の間の距離が長い場合は、1つの出力端子が1つの伝送ラインを駆動するのではなく、2つの伝送ラインを駆動する回路モデルを考慮する必要があります(3-2)。

一つの伝送ラインを駆動するよりも高い駆動能力が出力ドライバーに必要になります。また。設計前にIBISモデルを使用して、シグナル・インテグリティーのシミュレーションを実行することを推奨しています。

一部の製品は2つの伝送ラインを駆動するのに十分な駆動能力を持っていない場合がありますが、発振器の出力端子と負荷の間隔が十分に小さい場合には、システムをスター型トポロジーで表現できる可能性があります(3-3)。

※ SiTime製品の出力ドライバーは50-60Ωのインピーダンスを持つ伝送ラインを3つ以上駆動することは通常できませんので、単一のドライバーで3つ以上の伝送ラインを駆動することは推奨しません!

3-1. 近くにある複数の負荷を駆動する場合

複数の負荷が近くにあるのは、シンプルです。

クロックエッジの実効長を1/6 した値と伝送ラインから各負荷までの距離を比較し、後者の値のほうが短い場合、システムをこの回路モデルで表現することができます。下記の図に示すように、負荷をスター型の形状で接続しなければなりません。この場合の直列の終端抵抗の値は、単一負荷の場合と同じ計算で問題ありません。

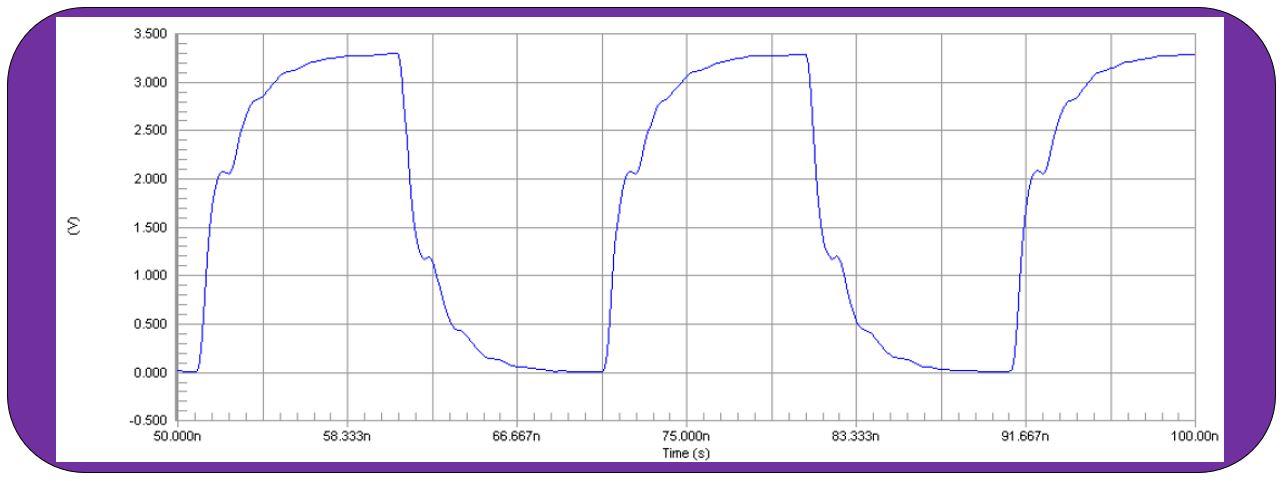

電源電圧3.3V のSiT8208 がこの構成回路を駆動した場合のシミュレーション結果も載せます。

※各パラメータ:Rs=43Ω、CL=5pF、レシーバーの数=2、伝送ラインからレシーバーまでの距離=0.5 インチ(〜75 ps)

伝送ラインからレシーバーまでの距離が長過ぎると、反射でシグナル・インテグリティーに問題が起きることも、シミュレーション結果を見ていただければ分かります。

3-2. 1つのソースから2本の伝送ラインを駆動する場合

クロックのレシーバーがお互い離れているケースです。レシーバー端の負荷を集中定数回路として配置することができませんので、このような場合には、負荷毎に個別の伝送ラインをクロックの出力端子が駆動する回路モデルを考える必要があります。

この方法は、伝送ライン毎に終端抵抗を1 つだけ必要とし、負荷側でフルスイングの信号振幅が得られるため、低コストです。ただし、最適なシグナル·インテグリティのために、以下の条件を満たす必要があります。

1. エッジの伝送中に、クロックドライバが十分なピーク電流を供給できる

2. すべての伝送ラインが同じ長さである

3. レシーバー端での負荷容量がほぼ同じである

4. 終端抵抗が以下から計算される値になっている

Rs = Z0 ー Rd ・N

Rs - ソースの終端抵抗

Z0 - 伝送ラインのインピーダンス

Rd - ドライバ出力の抵抗

N - 駆動ラインの数

3-3.スター型トポロジーで、2つの負荷を駆動する場合

二つの伝送ラインを駆動するのに、ソースの駆動能力が十分強くない場合には、スター型トポロジーの適用を検討することもできます。

このトポロジーでは、下記図中Rt の抵抗を中間の終端として使用します。通常Rt の抵抗値は伝送ラインのインピーダンスの1/3の値になるようにします。

スター型トポロジーでは通常、負荷側に終端抵抗を配置します。この場合、ソースドライバからの信号は中間終端によって分岐点で反射し返すことなくこれを通過し、負荷に到達した信号は負荷側の終端により再度ソース側に反射し返すことはありません。これにより、負荷側では反射のない良好な信号品質となりますが、非常に低振幅であり、多くのクロックレシーバには許容されない信号になります。もし、負荷側の終端がなく、負荷が高インピーダンスであれば、すべての信号エネルギーがソースに反射し返すことになります。Rt のネットワークにより中間点ではインピーダンスは整合されていますが、二つの反射した信号がここで結合されます。この場合、反射と結合のバランスを取り許容可能なシグナル・インテグリティーを実現することが非常に難しくなります。

負荷側の終端がなく、かつ伝送ラインの長さが信号エッジの実効長の3 分の1 よりも長い場合、このスター型トポロジーは推奨できません。例えば、1 ns の信号エッジの実効長では、伝送ラインの長さが2 インチを超えてはなりません。シミュレーション結果等についてはお気軽にお問い合わせください。

おわりに

いくつかシミュレーション結果も用いながら、終端方法を解説いたしました。

何かご不明点等ございましたら、お気軽にお問い合わせください。

お問い合わせ / サンプル依頼 / お見積り

SiTime製品に関してご質問、サンプルご希望などございましたら以下「お問い合わせボタン」よりご連絡ください。

製品のお見積もりをご希望の場合、「お見積りボタン」よりご依頼ください。