検証に便利な機能を豊富に備えており、その検証機能の1つであるコード・カバレッジについてご紹介します。

HDL の設計現場の状況

FPGA の大規模化により、HDL やテストベンチ全体を理解するのは困難になってきました。それにより、テストに穴が開いたり、不要な HDL 記述による無駄な回路増大が起きています。

コード・カバレッジとは?

シミュレーションを実行しながら、HDL コード内の各実行回数をカウントする機能です。

・ 検証対象の HDL デザインに対して用意したテストパターンによってシミュレーションが『どの程度』行われたか?を定量的に評価します。

・ 未検証部分がある場合、RTL の見直し、またはテストパターンの追加を行います。

コード・カバレッジを使うメリット

● テスト品質の向上

コード・カバレッジで実行されなかった箇所が『必要な機能』なら、テストに穴があることになります。テストベンチを追加してテスト品質を向上できます。

● 回路面積を縮小(コストダウン)

コード・カバレッジで実行されなかった箇所が『不要な機能』なら、該当する HDL 記述を削除して回路面積を小さくすることができます。

● FPGA の開発依頼元やプロジェクト・マネージャーからの信頼度が向上

FPGA 開発をデザイン・ハウスへ委託した依頼主やプロジェクト・マネージャーには、開発を依頼したデザインのテスト品質や回路のオーバーヘッドが見えません。コード・カバレッジによる高いカバー率を開発依頼元やプロジェクト・マネージャーへレポートすることで、信頼性の高い開発を行っていることをアピールできます。

コード・カバレッジの詳細な機能

コード・カバレッジの種類

Questa Sim / ModelSim は、様々な種類のコード・カバレッジをサポートしています。

(1)ステートメント・カバレッジ:ステートメント毎

・ 1行に複数のステートメントが記述されていても、各ステートメント毎にカバレッジをカウントします。

・ ステートメント毎に実行回数をレポート

例:if sig1 then hit <= ‘1’ ; out <= ‘1’ ; else hit <=………;

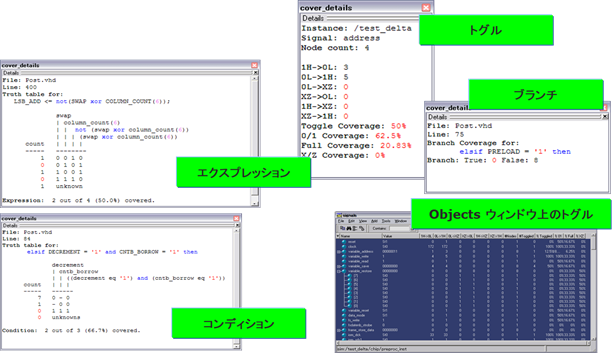

(2)ブランチ・カバレッジ:条件分岐

・ if 文や case 文などの条件分岐で、すべての分岐先が実行されたかどうかをカウントします。

・ 条件分岐を通過した回数、if 文での真偽の回数、case 文での検証した選択肢ごとの回数、分岐先での実行回数をレポートします。

例:if ( a or b ) then

(3)コンディション・カバレッジ:条件の組み合わせ

・ ブランチ・カバレッジの拡張機能で、分岐条件の入力と出力の組み合わせの実行回数を測定します。

・ 条件内の変数や条件の論理的な組み合わせを解析します。

・ 真偽を導く、変数や条件の組み合わせに対しての回数をレポートします。

例:if (a or b) then この例では4つの組み合わせ

(4)エクスプレッション・カバレッジ:アサインされる値を持つ式の組み合わせ

・ コンディション・カバレッジと同様ですが、代入文の右辺の式の実行回数を測定します。

・ アサインされる値を持つ式内の変数の論理的な組み合わせを解析します。

・ 式内の変数の組み合わせに対しての回数をレポートします。

例:a <= b or c ;

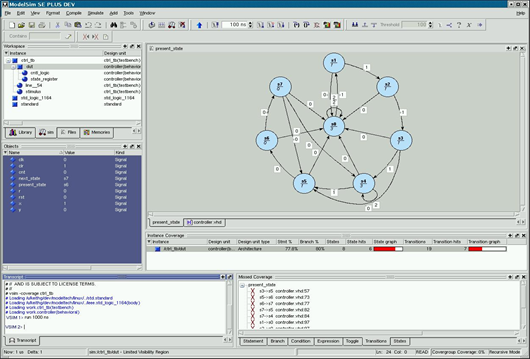

(5)FSM カバレッジ:状態・遷移

・ 論理ステートマシンの遷移回数を測定します。各ステートが実行されたか、遷移が実行されたか、各ステート毎の実行回数をレポートします。

(6)トグル・カバレッジ:トグル状態

・ 信号が 0 ⇔ 1 の変化した回数(活性化しているか)、トグル (変化) した回数を測定します。

カバレッジ範囲のコントロール

以下の方法により、カバレッジ対象を制御することができます。

● Exclusionsファイルの読み込みと保存

● Missed Coverage より指定(Exclude の設定)

● HDL 内で専用プラグマを挿入(プラグマ間のコードを対象外に自動設定)

コード・カバレッジのレポート

Questa Sim / ModelSim のコード・カバレッジは、レポートの内容をカスタマイズして、GUI とファイルで出力することができます。

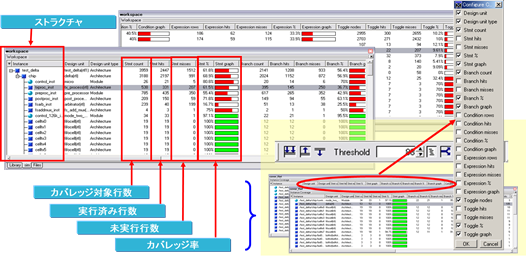

(1)GUI による解析

Workspase / ストラクチャ部 は、階層毎に下位階層の累計を表示します。Instance ペイン では、下位は含まないインスタント毎に表示します。

(2)Details ウィンドウ

詳細な情報を表示します。

(3)FSM カバレッジの GUI 表示

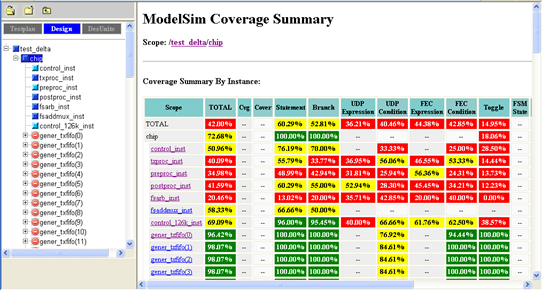

(4)コード・カバレッジ結果のファイル出力

コード・カバレッジの結果は GUI だけでなく、ファイルでも出力可能です。出力する際に、下記のように様々な形式でレポートすることができます。

① カバレッジ率のしきい値を変えて解析できます。

例えば、カバー率が 30% 以下の箇所だけを表示できます。

② カバレッジの解析結果からレポート除外する箇所を設定できます。

③ カバーされなかったステートとトランジションをレポートできます。

テストベクタを追加する際の情報になります。

④ 複数シミュレーション結果をマージできます。

一般的に、各ブロック内とブロック間の検証は論理シミュレーションで行い、システムレベルの検証は FPGA を使って実機で検証します。複数のテストベンチによるコード・カバレッジ結果をマージして、回路全体のカバー率をレポートできます。

⑤ インスタンス別、デザインユニット別、HDL のファイル別に出力できます。

⑥ テキスト、XML ファイル、HTML のファイル・フォーマットで出力できます。

HTML によるレポートは豊富な情報を階層化とカラー化で見やすくしています。お勧めするレポート形式の1つです。

関連情報

セミナー/ワークショップ

▶ [オンラインセミナー] ModelSim によるアサーション検証 <無料>

Questa / ModelSim のデバッグ機能であるアサーションベース検証(ABV)やコード・カバレッジ、拡張データフローの効果を紹介するセミナーです。特に、アサーションベース検証は FPGA デザインの半数以上で活用されているお勧めの検証手法です。

▶ 関連のイベント・セミナー

お問い合わせ

メーカー情報 Top へ

メーカー情報 Top ページへ戻りたい方は、以下をクリックください。

シーメンス(Siemens)が所有する商標や登録商標:こちら