はじめに

パワー MOS デバイスには、さまざまな構成材料とゲート構造のパワー MOSFET、JFET、IGBT などがあり、ゲートによって電流の流れが制御される 3端子デバイスです。ほとんどのパワーエレクトロニクスアプリケーションでは、ゲートはデバイスが完全にオフの状態で電流の流れをブロックするか、伝導損失を最小限に抑えて完全にオンになるように駆動されます。オン状態とオフ状態の間の遷移によって高熱が発生するため、スイッチング電力損失を最小限に抑えるために遷移時間は可能な限り短く保たれます。これが、ハードスイッチのスイッチモード電源 (SMPS) 設計の技術です。

スイッチング遷移が必然的にスイッチのオン/オフ状態に比例したり、動作点が遷移領域内に意図的に設定されたりするアプリケーションは数多くあります。本記事では、これらのアプリケーションにおけるパワー MOS と オンセミ JFET の両方の動作について説明します。

オペレーティング・リージョンの定義

パワー MOS または JFET の出力特性には、図1の オンセミ JFET に示すように、カットオフ、アクティブ、オーミックの 3つの領域があります。カットオフでは、非常に小さな電流しか流れないため、デバイスはオフであるとみなされます。ゲート ソース電圧が十分に高くなると、デバイスはオーミック領域に入り、ドレイン ソース電圧 VDS が小さくなり、電流の流れは主にオン抵抗によって決まります。

図1:125℃ における 1200V Qorvo JFET の出力特性

オーミック領域の境界は以下によって定義されます。

オーミック領域とカットオフ領域の間にはアクティブ領域があり、パワー MOS、JFET、バイポーラートランジスターの線形領域と飽和領域の異なる意味の混同を避けるためにこのように指定されています。したがって、アクティブ領域内の動作は、多くの文献では線形モードと呼ばれていますが、本記事ではアクティブモードと呼びます。アクティブモードでのドレイン電流は主にゲートソース間電圧に依存しますが、特に VDS が低い場合は、ドレイン ソース間電圧への依存が図1 でも明確に示されています。

アクティブモードのデバイスは同時にサポートする電流と電圧によって高電力が発生し、これを熱として放散する必要があります。したがって、アクティブモードで経済的に機能するには、前方安全動作領域 (FSOA) を最大限に活用する必要があり、デバイスの制限を理解することは、信頼性の高い動作を実現するために不可欠です。

アクティブモードでのパワー MOS 障害の根本原因

アクティブモードで動作するアプリケーションは、パワー MOS データシートの FSOA 内で適切に動作しているにもかかわらず、障害に最も悩まされます。障害の原因は熱不安定性であり、電流の集中によってホット スポットが発生します。

図2:ホットスポット現象がよくわかる [1] の 5x5 mm パワー MOS 温度分布 (℃)

パワーデバイスチップ全体の避けられない温度勾配は、温度上昇とともに電流が正に変化するため、ホットスポットにつながる可能性があります。チップ上のより高温の領域はより多くの電流を集中させ、それがさらなる加熱を引き起こし、局所的な領域で熱暴走による故障を引き起こす可能性があります。[1]では、アクティブモードのパワー MOS 全体の温度を測定することで、熱不安定性の影響がグラフで示されました。結果は図2 に大まかに再現されており、最低、最高、平均温度の差が大きいホットスポットが明確に示されています。ホットスポットの電流の集中と温度は非常に高くなる可能性があり、その結果、バーンアウトスポットとデバイスの故障が発生します。

スイッチモードアプリケーションでは、電流の集中は通常は問題になりません。アクティブ領域は非常に速く通過し、動作のオーミック領域での電流は、対応する高い正の温度依存性を持つチャンネル抵抗とバルク抵抗によって制限されます。ただし、アクティブモード動作では、熱的に重要な時間にわたって高い電力消費が発生します。したがって、熱不安定性により、アクティブモードのパワー デバイスの真の安全動作領域が制限されます。幸いなことに、多くのパワー MOS メーカーはこれを認識しており、現在では FSOA の高電圧側で一定の電力消費ラインから削減した FSOA 曲線を公開しています。本記事ではこれをさらに一歩進め、[1-3] の研究に基づいて、公開されているデータシート情報に基づいて熱不安定性の実際の開始を推定します。

アクティブモードにおけるパワー MOS の熱不安定性の解析

熱不安定性は、電力が熱的に放散できる量を超えて増加した場合に発生します [4]。電力と熱電力をそれぞれ PG と Pθ で表すと、熱安定性は数学的に以下のように表されます。

∂T=∂Pθ ∙ Zθ かつ ∂PG=∂ID ∙ vDS であり、Zθ は熱インピーダンス(時間依存熱抵抗)であるため、熱安定性の条件は以下のように表すことができます。

アクティブ領域のパワー MOS ドレイン電流は以下のように近似できます。

式 (4) では、KMOS=μn ∙ Cox ∙ W / (2 ∙ L) であり、ここで µn は反転層の多数キャリア移動度、Cox は単位面積あたりのゲート酸化膜容量、W はゲート幅、L はチャンネル長です。容量 Cox は、ゲート絶縁体の誘電率とその厚さによって決まります。したがって、ゲート幅 W とチャンネル長 L と同様に一定です。電子移動度 µn、つまり KMOS の大きさは、温度とドレイン電流 iD の増加とともに減少します。

十分なドレイン電流では、電子移動度の低下による電流制限効果は、温度依存のしきい値電圧による電流の増加を上回ります。したがって、ドレイン電流が温度とともに増加してはならないという安定性基準に基づいて、パワー MOS の熱的に安定した動作条件を大まかに予測できます。一次近似 [1, 2] として、式 (4) を温度に関して微分します。結果はドレイン電流温度係数 (DCTC) であり、ドレイン電流の関数として T(ID) として表されます。DCTC が 0以下であれば、パワー MOS は常に熱的に安定しています。

パワー MOS の場合、∂KMOS /∂T は常に負であるため、熱不安定性は -2 √(KMOS ∙ ID) ∂VGS(th) /∂T 項、具体的には閾値電圧温度係数 (TVTC) である ∂VGS(th) /∂T によって直接引き起こされます。したがって、TVTC が 0以上であれば、デバイスはアクティブモードで常に熱的に安定していることになります。

安定係数 γ は、式 (3) に αT(ID) を代入して整理することで導入されます([1-3]では不安定係数 S と呼ばれます)。

式 (6) を書き直すと、有用な安定性基準が得られます。

現在の課題は、DCTC 曲線 αT(ID) を決定することです。これはデバイス設計パラメータから計算できますが、通常は公開されていません。または、測定できます。幸いなことに、伝達特性(出力特性データから導出)はほとんどのデータシートで公開されており、必要な DCTC データが含まれています。

図3:パワー MOS (a) 伝達特性 (b) 伝達特性から導出された αT 対 iD

伝達特性の情報は、図3(b) に示すように、125℃ での電流から 25℃ での電流を差し引き、125 – 25 = 100 で割ることによって、各データポイントが特定のゲート-ソース電圧にある αT 対 電流のグラフに転置できます。このようなグラフは、熱不安定性の開始を推定したり、さまざまなパワー デバイスの固有の安定性を比較したりするのに非常に役立ちます。

定常状態(非パルス)の場合を考えてみましょう。Zθ は単純に RθJC となり、データシートのジャンクションケース熱抵抗の公開値が使用されます。データシートの RθJC 値を使用すると、パワー MOS メーカー間のマージンの違いにより多少のばらつきが生じ、データシートの最大値を使用すると当然最悪のケースの分析になります。ただし、公開されたデータシート情報に基づいてパワー MOS の熱安定性に関する重要な洞察を提供する妥当な近似値が得られます。式(7) は、次のように vDS のさまざまな値に対して評価されます。図3(b) の線「a」は、1/(vDS ∙ RθJC ) の値を示しており、これは常に αT(iD) 曲線よりも大きいため、パワー MOS は、図 3(a) の電流クロスオーバー ポイントより低い状態で動作している場合でも、この低いドレイン-ソース電圧で常に熱的に安定しています。

線「b」は αT(iD) 曲線のピークと交差しており、ホット スポットが形成され始めるドレイン ソース電圧を示しています。線「c」は αT(iD) 曲線と 2 か所で交差しており、熱不安定範囲を示しています。I1 未満では、消費電力が十分に低いため、電流の集中は重要ではありません。電流が I2 を超えるとホット スポットが形成され、I3 はホット スポットでその後到達するピーク電流ですが、デバイスが先に故障する可能性があります。

解析を FSOA に拡張すると、さまざまなドレイン-ソース電圧で、熱インピーダンスと接合部およびケース温度に基づいて最大消費電力を計算することで、熱不安定性の開始をプロットできます。次に、同じドレイン-ソース電圧ポイントで、1/(vDS ∙ Rθ ) 値を計算します。最後に、必要に応じてドレイン電流(消費電力)を減らし、調整された各 1/(vDS ∙ Rθ ) 値が αT(iD) 曲線以上になるようにします。電流が減少した各ポイントは、熱不安定性の開始を大まかに示します。

αT(iD) グラフの横軸に沿った電流値は、FSOA 分析にとって重要です。図3(b) の曲線は、2つの温度曲線(この場合は 25℃ と 125℃)が同じゲート-ソース電圧を持つ場所に対応するデータ ポイントから作成されました。αT(iD) グラフの横軸の電流値は、図3(a) の 25℃ と 125℃のデータ セットからの平均電流として補間できます。

800V、0.75Ω の従来型 MOSFET の FSOA 分析の例を図4 に示します。約50Vを明らかに超える電圧では、予測される熱不安定性の発生はデータシートの FSOA 境界をはるかに下回っています。この例では、ケース温度が 25℃ に保たれていますが、これも非現実的です。それでも、ケース温度に関係なく、最大安全電力消費と電圧の大まかな関係を示すため、そこから重要な情報を得ることができます。

図4:800V シリコン MOSFET の DC FSOA と TJ = TJmax、TC = 25℃ での推定熱安定性境界

異なるケース温度と接合部温度で FSOA グラフをプロットするのは簡単です。低電圧側の電流は、電力消費ではなく RDS(on) によって制限されます。ピーク電流は最大電力消費で、Ipeak = √(PD,max / R DS(on) として計算されます。ここで、PD,max = (TJ – TC ) / RθJC です。ピークを超えると、電流は単純に PD,max / VDS になります。ただし、電圧が上昇するにつれて電流を減らして、上で説明したように αT,max (ID) = 1/(vDS ∙ RθJC) 曲線が αT(iD) 曲線の下を横切るのを防ぐ必要があります。パルス電力に関して分析する場合は、対応するパルス持続時間での単一パルス過渡熱インピーダンスグラフの RθJC を ZθJC に置き換えるだけです。熱インピーダンスを下げると、αT,max(iD) 曲線が FSOA グラフの熱安定性曲線とともに上側にシフトし、熱不安定動作領域が減少するか、完全になくなります。このため、一部の MOSFET メーカーは DC FSOA 曲線を公開せず、パルス FSOA 曲線のみを公開しています。

ピーク DCTC を低下させる、または同等に負の TVTC の大きさを低下させると、熱安定性の動作範囲が広がります。また、式 (5) から、デバイスは αT(iD) のすべての負の値に対して無条件に安定していることを思い出してください。特殊なリニア MOSFET は、ピーク DCTC を低下させ、FSOA を改善しました。ただし、パワー MOS では TVTC をゼロに下げることができないため、動作電圧、電流、温度の特定の範囲では依然として熱不安定性を示します。JFET では、TVTC を 0 にすることができます。

オンセミ JFET の熱安定性と改良された FSOA

JFETのドレイン電流は、ID = IDSS ∙ (1 – vGS / VGS(th) )^2 と大まかに近似でき、これはパワー MOS 方程式(4) と同じ形式で表すことができます。

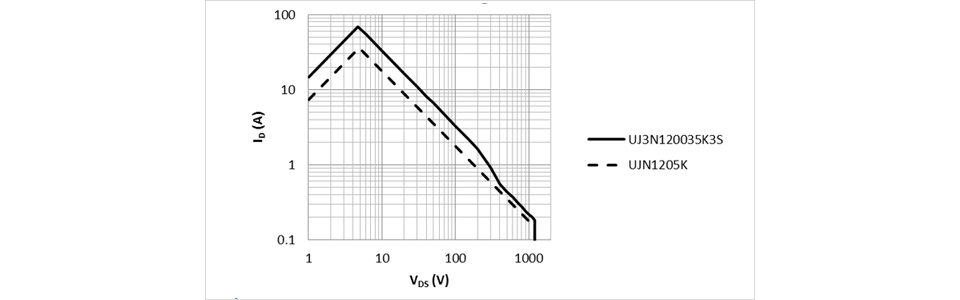

一部の JFET のドレイン電流は、アクティブモードではドレイン-ソース電圧に大きく依存します。ただし、式(8) は、KJFET が vDS とともに増加しても、式 (4) の KMOS と同様に温度とともに常に減少することを考慮すると、熱安定性を示すのに十分です。したがって、TVTC がゼロであれば、JFET は常に熱的に安定しており、これは MOSFET の場合と同じ基準です。オンセミ は、2種類のゲート構造を持つ SiC JFET を製造しています。1つは TVTC がゼロで、もう 1つは TVTC が低いです。どちらのタイプもアクティブモード動作に非常に適しています。オンセミ JFET とさまざまなパワー MOS デバイスの DCTC の違いは、図5 にグラフで示されています。

図5:各種デバイスにおけるドレイン電流に対する αT(iD)

DCTC のピークは、デバイスの固有の熱安定性の指標であり、デバイスタイプ間の大まかなですが不完全な比較に役立ちます。図5 では、オンセミ 1200 V SiC JFET UJN1205K は DCTC が常に負であるため、常に熱的に安定していることがわかります。次は、同じく 1200 V SiC JFET である オンセミ UJ3N120035K3S です。TVTC はわずかに負であるため、DCTC のピークは正です。図5 によると、800V の従来の MOSFET は、特殊な 1200V リニア MOSFET と同等のピーク DCTC を持ち、それぞれ 800V で終了する FSOA を持っています。ただし、これらのデバイスの FSOA は、後で示すようにかなり異なります。最後に、オンセミ JFET と同様の RDS(on) を持つ 1200 V SiC MOSFET は、比較的高い DCTC を持っています。

通常の固定接合部温度とケース温度とは多少異なるアプローチを採用し、最大消費電力を熱安定性境界での最大消費電力と一致するように調整して図6 を作成しました。つまり、図6 のそれぞれの FSOA 曲線内で動作している場合、各デバイスは常に熱的に安定しており、最大消費電力は一定です。

図6:熱安定性境界内のさまざまなデバイスのFSOA

予想どおり、SiC MOSFET は高電圧での FSOA が最も低く、従来の 800V MOSFET に匹敵します。ただし、シリコンベースの MOSFET とは異なり、SiC MOSFET と SiC UJ3N120035K3S JFET は RDS(on) の大きな利点があり、それに応じてピーク電流が高くなるとオン電圧が大幅に低下します。リニア MOSFET と SiC JFET はどちらも、ピーク DCTC が低く熱抵抗が組み合わさっているため、熱安定性の境界が広くなっています。UJ3N120035K3S JFET のみが、800V を超えるドレイン ソース電圧で大きな使用可能な FSOA を持ち、高電圧アクティブモードアプリケーションに有利です。UJN1205K は、TVTC がゼロであるため、消費電力に関係なく常に熱的に安定しているため、図6 から省略されています。代わりに、UJN1205K を以下の図7 の UJ3N120035K3S と比較します。

これらの JFET のチップ サイズと RDS(on) は非常に似ていますが、UJ3N120035K3S は製造プロセスの改善により RθJC が低くなっています。この場合、UJ3N120035K3S の低い熱抵抗は、熱安定性の限界の減少を上回り、400V 以上での消費電力を 220W に制限します。

上に示したように、特定の条件下で熱不安定になりやすいパワーデバイスは、FSOA を低く抑えることでアクティブモードで確実に動作できます。SiC デバイスは、シリコンベースのデバイスとは異なり、最大定格接合温度からのマージンを減らしても、あるいはまったくマージンがなくても安全に動作できると言えます。いずれにしても、FSOA を低く抑えて動作させることで、平均チップ温度が十分に低くなり、大きなホットスポットが形成されず、チップのピーク温度によって障害が発生することもありません。これは通常、さまざまな動作条件で複数のデバイスを破壊し、統計的に有意な安全マージンを適用することで実験的に決定されます。DCTC 分析を使用すると、そのような破壊テストは必要なくなるか、必要でなくなるかのどちらかが少なくなり、実際の FSOA は動作の物理的性質に基づいてよりよく理解できます。

オンセミ JFET は、実際には高速スイッチングと MOSFET-SiC JFET カスコードでの使用向けに設計されているため、内部ボディーダイオードはありません。オンセミ JFET は、効率的な設計と合理化された製造プロセスにより、スイッチモード電源 (SMPS) アプリケーションで魅力的であり、高電圧アクティブモードアプリケーションでも他のデバイスタイプよりも優れています。

並列化

SMPS とアクティブモードの両方のアプリケーションでは、熱放散要件により並列化が必要になることがよくあります。両方ともアクティブ領域の特性に関連して以下で説明します。

SMPS

複数の並列デバイスを考えてみましょう。それぞれのしきい値電圧は変動します。しきい値電圧が最も低いデバイスは最初にオンになり、最後にオフになります。そのため、スイッチング損失と発熱が不釣り合いに高くなります。全体的な電力損失が大きい場合、つまり重い負荷で動作している場合、最も熱いデバイスの負の TVTC により、動的電流の不均衡がさらに増加し、自己強化される可能性があります。これは、スイッチング損失が伝導損失を支配している状況では、たとえば MOSFET や NPT IGBT のように伝導損失が正の温度係数を持つ場合でも、信頼性の問題になる可能性があります。これが、パワー MOS デバイスを並列接続するときに十分な電流マージンを適用する必要がある理由の 1つです。

オンセミ JFET では、パワー MOS と同様に、デバイス間でしきい値電圧にばらつきがあります。ただし、TVTC が低減されているため、動的電流共有が改善されます。これは、デバイス間でスイッチング損失が完全に均一であるという意味ではなく、最も高温のデバイスがスイッチング中にますます増加する電流を流す可能性が低いことを意味します。この点は オンセミ カスコードにも当てはまります。カスコード内の JFET はスイッチング中に高電圧を処理するためです。カスコード MOSFET は、JFET がスイッチング プロセスを完了する前にオンまたはオフになります。伝導損失に関しては、オン抵抗の正の温度係数により、静的電流の不均衡により単一のデバイスが熱暴走に陥らない熱平衡が保証されます。その結果、オンセミ JFET とカスコードは、静的伝導とスイッチングの両方で熱的に非常に安定しているため、並列接続すると信頼性が高くなります。

アクティブモード

パワー MOS と同様に、しきい値電圧と温度依存ゲインの部品間のばらつきは、並列オンセミ JFETの定常アクティブモード動作の課題です。この課題を解決する一般的な方法は、図8 の簡略化された回路図に示すように、オペアンプと電流センス抵抗器を使用して各JFETの個別のフィードバック制御を使用することです[5]。

図8:定常アクティブモード動作のためのオンセミ JFETの並列接続の簡略化された例

負のしきい値電圧を持つ各オペアンプでは、オンセミ JFET のゲートを駆動するために当然負の電源が必要です。

デモンストレーション

プロトタイプの電子負荷ボードは、6つの独立したチャンネルで構成され、各チャンネルには オンセミ UJ3N120035K3S が JFET として搭載されています。図9(a) の上面図は、6 つのチャネルの回路を示しています。各オペアンプはデジタル制御カードからコマンド信号を受信し、冷却ブロワーは約14W しか消費しません。図9(b) では、JFET が回路基板とヒートシンクの間に「挟まれて」見えており、JFET の背面ドレインパッドとヒートシンクの間には電気絶縁材はありません。各 UJ3N120035K3S は、電流と電圧(BVDS まで)のあらゆる組み合わせに対して常に熱的に安定しており、消費電力は 220W です。

図9:プロトタイプの電子負荷テストボード (a)上面図、(b)ヒートシンクとPCB間のJFETを示す側面図

予備テストでは、電圧が 20V から 1000V に上昇するにつれて指令電流を調整することで、各 JFET に安定した 75W の負荷がかかり、ヒートシンクのピーク温度は 97°C に達しました。空冷が改善されれば、各 JFET は 100 W をはるかに超える電力を処理でき、液体冷却ではさらに多くを処理できます。執筆時点ではまだテストが進行中ですが、広い電圧範囲にわたってヒートシンクの温度が上昇しても一定の負荷電力が維持されることが実証されたことで、TVTC が低い オンセミ JFET の熱安定性の理論が実証されました。

参考文献

[1] P. Spirito, G. Breglio, V. d’Alessandro, N. Rinaldi; “Thermal Instabilities in High Current Power MOS Devices: Experimental Evidence,

Electro-thermal Simulations and Analytical Modeling”, Proc. 23rd international conference on microelectronics (MIEL 2002), May 2002

[2] P. Spirito, G. Breglio, V. d’Alessandro, N. Rinaldi, “Analytical Model for Thermal Instability of Low Voltage Power MOS and SOA in Pulse Operation”,

Power Semiconductor Devices and ICs Proceedings, May 2002

[3] P. Spirito, G. Breglio, V. d’Alessandro, N. Rinaldi, “Modeling the Onset of Thermal Instability in Low Voltage Power MOS: An Experimental Validation”,

Proceedings of the 17th International Symposium on Power Semiconductors and ICs, May 2005

[4] P. Hover, P. Govil; “Comparison of one- and two-dimensional models of transistor thermal instability”, IEEE Transactions on Electron Devices ,

Volume 21, Issue: 10, Oct 1974

[5] R. Frey, D. Grafham, T. Mackewicz; “New 500 V Linear MOSFETs for a 120 kW Active Load”, PCIM Europe, June 2000

お問い合わせ

本記事に関してご質問などありましたら、以下より問い合わせください。

オンセミメーカー情報Topページへ

オンセミメーカー情報Topページへ戻りたい方は、以下をクリックください。