シリーズ2回目はVceo(コレクター・エミッター間電圧)とVces(コレクター・エミッター間降伏電圧)について説明します。

コレクター・エミッター間電圧Vceo

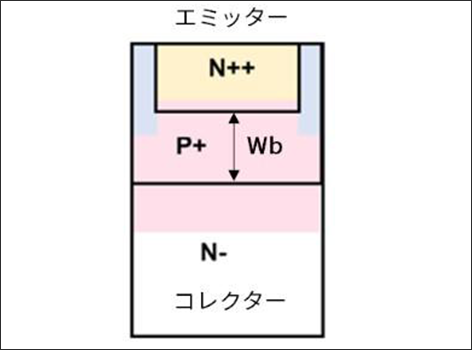

Vceoはベースからエミッター側に広がった空乏層とEBジャンクションからベースに広がった空乏層がぶつかった時が耐圧です。

(下の左図5参照)

これはディスクリートもプレーナー構造も同じ場所で、図5のEBジャンクション直下のベース幅(Wb)、Vcboが決まればこのベース幅(Wb)によりVceoは決まります。

さてこのベース幅(Wb)、実はhFEを決める物理ファクターのひとつです。

ベース幅(Wb)が広ければhFEは低く、狭ければhFEは高くなります。

また従来の熱拡散法でトランジスターをつくると、ここの制御が難しく一般的にhFEは1/2~狙い目~2倍でばらつくと言われています。

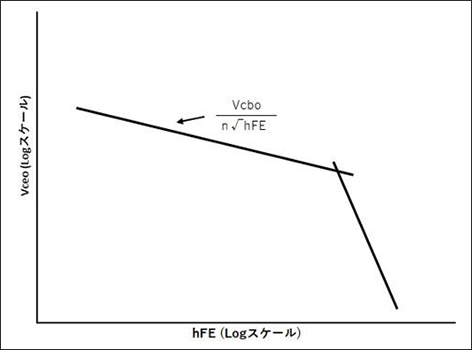

今までの話を式で表すと、

Vceo=Vcbo/n√hFE の関係です。

nは実験により求められる係数です。

今も新規にバイポーラトランジスターを開発しているメーカーがいたらT-CAD(プロセスシミュレーションツール)でnを求めているかもしれません。

実験によってnを求めるときはhFEをばらつかせて下の右図6のグラフを作成します。直線の傾きがnです。

コレクター・エミッター間降伏電圧Vces

続いてVcesについて説明したいと思います。

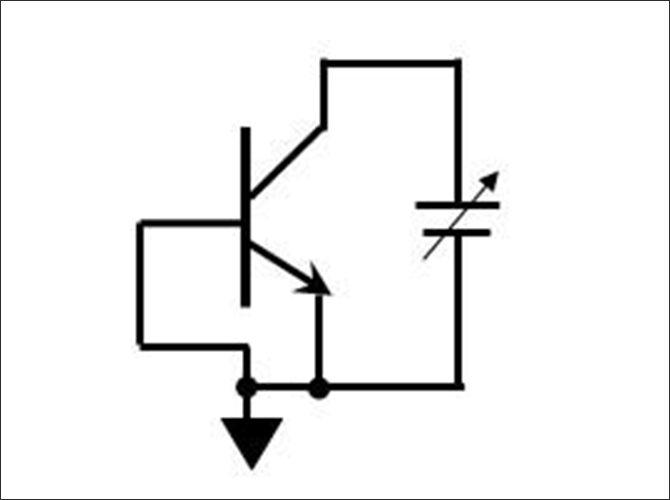

Vcesは図7のように、エミッターベースをショートした状態でのコレクターベース間の耐圧です。

EBショートなので耐圧波形はどうなるかと言うと、実はDC測定とパルス測定では全く耐圧波形が異なります。

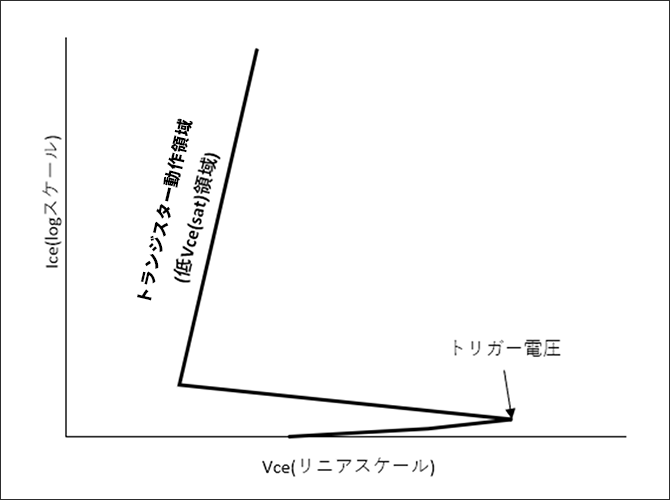

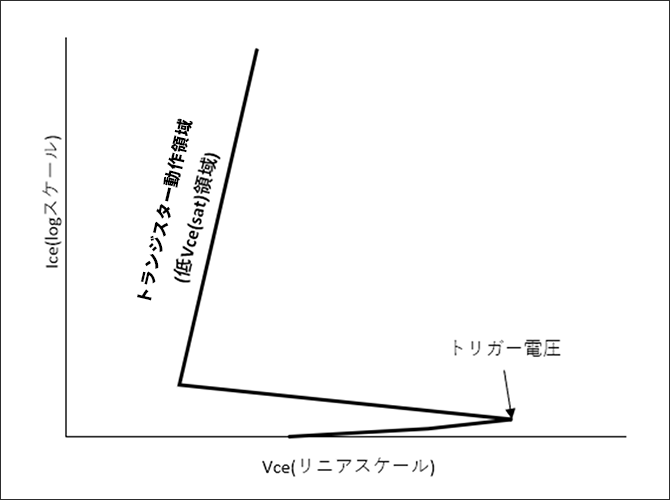

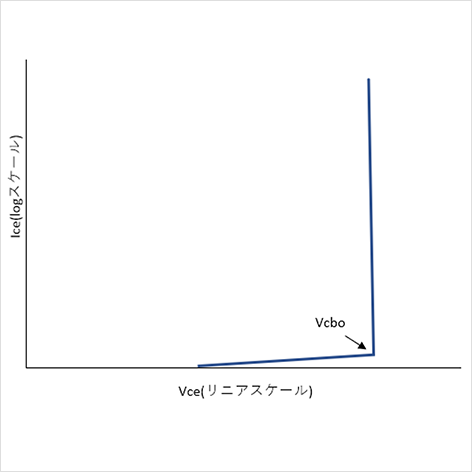

カーブトレーサーを用いたDC測定だと下の図8のような波形です。

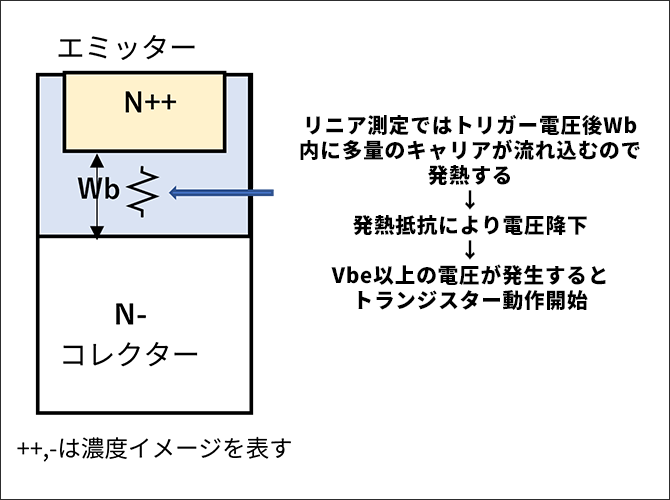

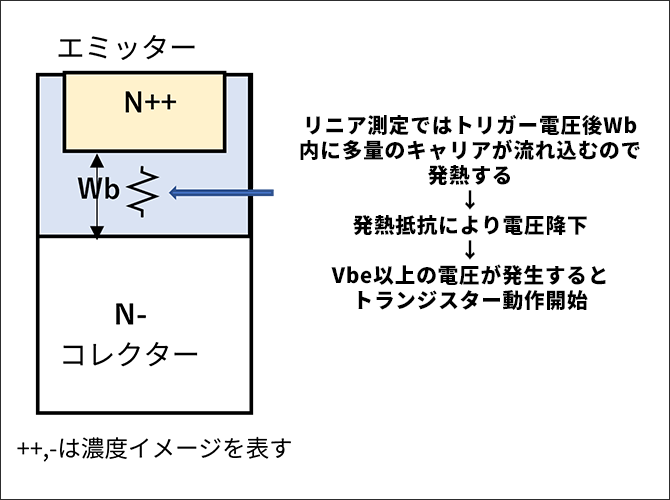

これはベースに注入された少数キャリアと発熱によりベース幅(Wb)内で電圧ドロップが起きトランジスター動作が起きたためです(下右図9参照)。

パルス測定での耐圧波形は、Vcboと同一です。(右図10参照)

普段から電源にSMU(ソースメージャーユニット)を使ってトランジスター特性を測定している若手エンジニアだと、DC測定とパルス測定で波形が異なる事をまだ経験していないのでベテランエンジニアのアドバイスが必要かと思います。

さてパルス波形でのVcesがVcboと同一になるのは、パルス入力ではベース幅(Wb)での発熱が低く、電圧降下が生じないので単純にダイオード特性が測定されます。

別の言い方をすれば、ベース幅(Wb)内で発熱するだけのエネルギーを与えてあげれば、トランジスター動作をするということです。

一般的にEBショートでエミッター接地で、コレクターバイアスでの使い方をオフトラと呼んでいます。IC上ではこの形でエネルギーの大きい静電気エネルギーの破壊防止素子としてよく使われます。ベース幅(Wb)の調整でいかようにも静電パルスに対する動作電圧設定ができるので静電気破壊保護素子として非常に重宝されています。

次回シリーズ3回目はエミッターベースジャンクション耐圧Veboについて説明します。

連載記事一覧ページへ

このトランジスター連載記事の一覧および他の記事を確認したい方は以下をクリックしてください。

お問い合わせ

本記事にて紹介した内容に、ご興味がある方は、ぜひお問い合わせください。

オンセミ メーカー情報Topへ

オンセミ メーカー情報Topに戻りたい方は以下をクリックしてください。