目次

1. 高電圧系ゲートドライバーって何?

2. どんな製品?どんな保護機能があるの?

3. NCV57000シリーズを使いこなそう!!

4. 磁気方式Galvanic Isolatedタイプ使用時のレイアウトで注意するポイントは?

1. 高電圧系ゲートドライバーって何?

高電圧系ゲートドライバーは、大きく2グループの製品群にわかれます。

・Junction Isolatedタイプ

・Galvanic Isolatedタイプ

それでは、それぞれのタイプについて、どういったものなのか概要を説明します。

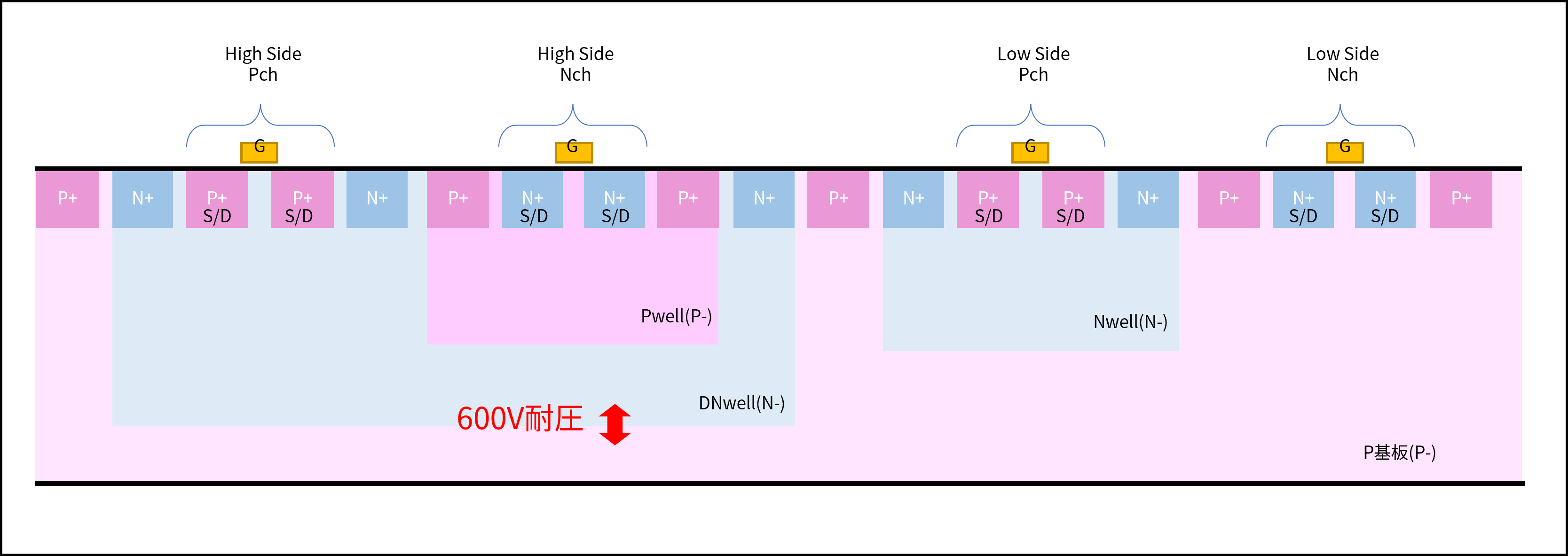

Junction Isolatedタイプとは

“P型半導体”と“N型半導体”、いわゆるPN Junctionの逆耐圧を利用して、高圧に対応した耐圧を確保し、一例としては、High Sideの島の電位をGND基準で600V以上持ち上げられるような構成を取っているゲートドライバーです。断面構造のイメージを図1に示します。

おわかりのように、物理的にはPとNが接合していますので、言い換えたら“直接的な導電パスが存在する“ことになり、一般的には“非絶縁タイプ”と呼ばれることが多いように感じます。

Galvanic Isolatedタイプとは

Junction Isolatedタイプとは対照的に、物理的に絶縁されているタイプ、言い換えたら“直接的な導電パスが存在しない“ゲートドライバーです。

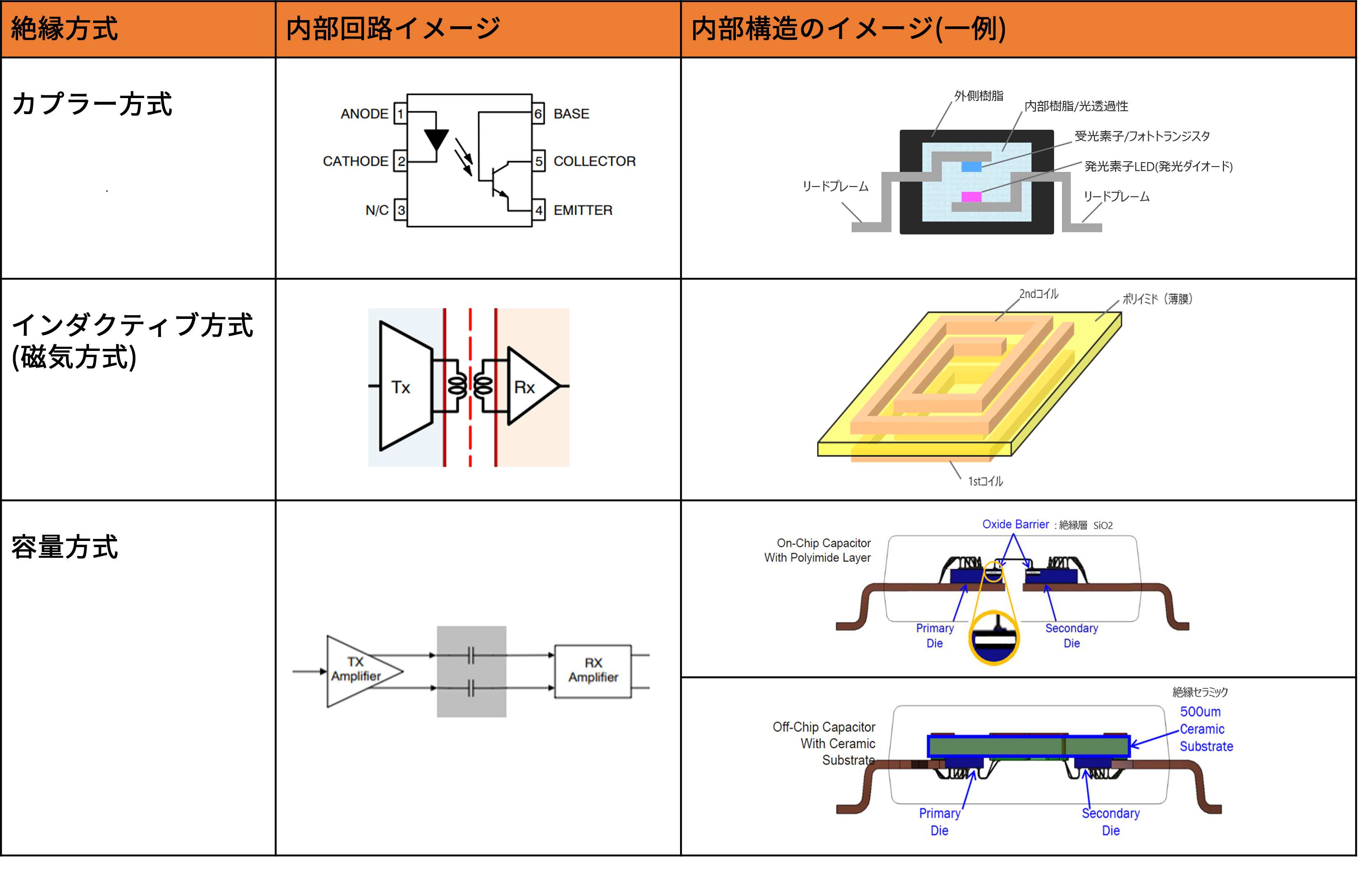

絶縁方法としては、大きく下記の3つの方式があります。

オンセミ製のGalvanic Isolatedタイプ絶縁ゲートドライバーは、カプラー方式とインダクティブ方式の製品がありますが、現在注力製品としては後者のインダクティブ方式の製品です。続々と新製品をリリースしていて、パワー半導体とセットで最適なゲートドライバーも検討できるようにラインナップを拡充しています。

本内容については、あわせて下記リンクより、デジタルアイソレーターの記事も参考にしてください。

他社製と何が違うの!?オンセミ社製デジタルアイソレーターの特長とは何?

次章にて、Flagship製品である、NCD(V)57000/NCD(V)57001の紹介をします。

2. どんな製品?どんな保護機能があるの?

製品について

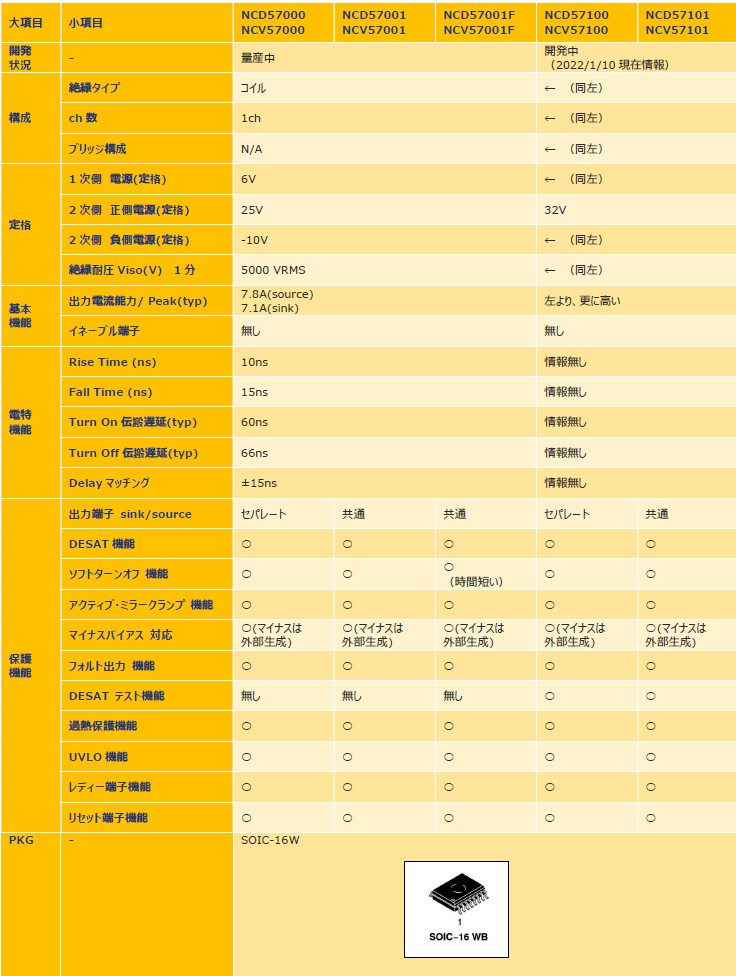

NCD(V)57000シリーズは、ガルバニック絶縁ゲートドライバー製品のFlag Shipモデルとして、NCD(V)57000が2019年に初めてリリースされました。IGBTやSiCMOSを駆動させるメイン機能に加え、様々な保護機能が搭載されています。

その後、機能を様々な用途ごとに最適化した製品や更に機能の取捨選択した製品開発など、ラインナップを拡充しています。ラインナップが多いと、どれを使えばよいのか選択に悩んでしまいそうですが、お客様の様々な用途に合わせて最適部品を選択できるようにとのオンセミの開発思想が反映されていると思います。選択に悩んだ際は、いつでもお問い合わせください。

それでは、NCD(V)57000シリーズの特性及び機能マトリクス表を紹介します。なお、NCD(V)57000は1chタイプ(シングル品)ですが、ブリッジ構成の2ch出力品などもラインナップにあります。本記事の下方にメーカーHPへのリンクが掲載されていますので、そちらからご確認ください。

製品名の上段は民生品、下段は車載品です。

保護機能について

NCD(V)57000シリーズには、一般的に求められる保護機能のほとんどの機能が盛り込まれていると言えると思います。

下記表にて簡単に説明します

|

表2:保護機能一覧

3. NCV57000シリーズを使いこなそう!!

NCD(V)57000シリーズを使用する際に、注意する点などについて、いくつか下記に記載します。

本項目の内容については、オンセミ社のアプリケーションノート(AND9949-D.PDF)を参照しています。

・入力(IN+,IN-)と出力(OUTH,OUTL)の論理関係

・1次側の入力電源

・2次側の入力電源

・損失および熱に関して

以下、詳細を説明します。

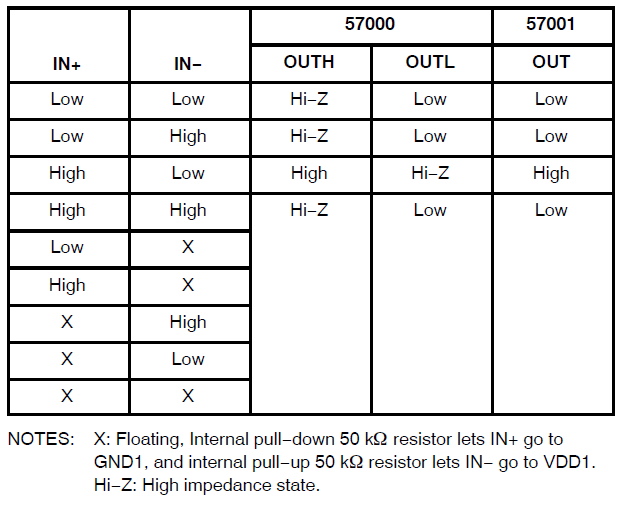

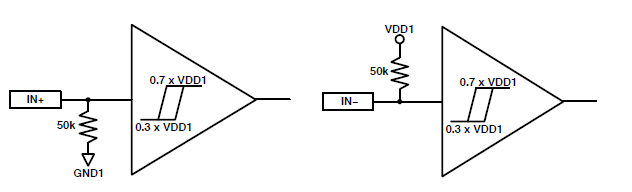

入力(IN+,IN-)と出力(OUTH,OUTL)の論理関係

下記表3と図3,4,5はオンセミ社のアプリケーションノート(AND9949-D.PDF)を抜粋したものです。

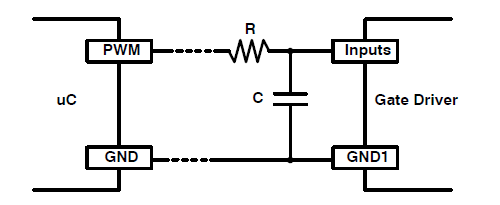

一般的には、入力(IN+,IN-)はマイコンから信号をもらいますが、信号品質を向上させるためにRCフィルター回路を挿入することができます。

RとCの値は、駆動周波数やDutyなどシステム要件によって異なります。また、入力信号(マイコンの出力)は、標準の CMOS またはプッシュプル駆動回路が推奨され、オープンドレイン構成は避けた方がよいでしょう。

PBCレイアウトでは、RとCをできるだけゲートドライバー側に近づけ配線を短くする必要があります。

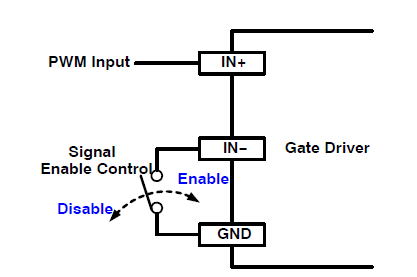

また、IN+のみを駆動用端子として使用し、IN-端子をEN信号用の端子として使用することも可能です。

もちろん、IN-のみを駆動用に使用することも可能です。ただし後者は入出力の論理が逆になります。

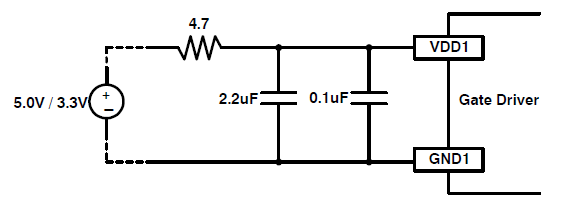

1次側の入力電源

直列抵抗とデカップリング コンデンサーは、VDD1 と GND1 の間に配置する必要があります。

コンデンサーは、高周波ノイズを除去して入力バイアス電圧を維持するために、可能な限り、ゲートドライバーICに近づけて配置する必要があります。

一般的にコンデンサーは、低ESL及び低ESR のチップ コンデンサー (MLCC: 積層セラミックチップコンデンサー) を推奨します。

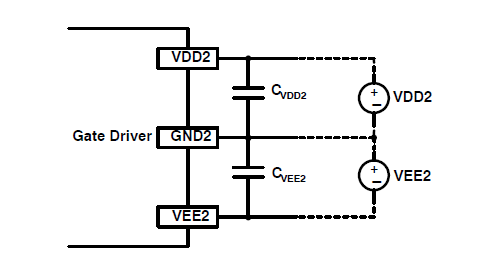

2次側の入力電源

出力端子は高い電流能力をそなえていますので、IC内部の出力MOSがオンする際、非常に高いピーク電流が発生します。ゆえに、PCBレイアウトはとても注意が必要になります。

VDD2-GND2の間及び, VEE2-GND2の間にデカップリング コンデンサーを配置する必要があります。これらコンデンサーは、PCBの配線を含む寄生インダクタンス成分によるオーバーシュート電圧とアンダーシュート電圧を防ぐために、可能な限り、ゲートドライバーに近づけて配置する必要があります。

また、過大なピーク電流は、外部の負荷容量起因が主なので、出力MOSのゲート抵抗(外部抵抗)に依存します。

一般的なアプリケーションでは、ゲート抵抗値が 10Ω を超える場合、正 (VDD2) および負 (VEE2) バイアスごとに 10uF のコンデンサーが必要です。

ゲート抵抗が 10Ω より小さい場合、20uF のコンデンサーが推奨されます。

一般的にコンデンサーは、低ESL及び低ESR のチップ コンデンサー (MLCC: 積層セラミックチップコンデンサー) を推奨します。

損失および熱に関して

一般的なことですが、損失は熱に変換され自己発熱します。そこで、自己発熱分をΔTとし、ΔTを考慮しIC内部のシリコン(ジャンクション)温度がTj_maxを超えないように使用する必要があります。

Tjは、周囲温度TaとΔTによって下記関係式になります。

次に、ΔTについて考えてみましょう。ΔTは損失PallとPKGの熱抵抗θjaによって求められます。

なお、少しだけ横道にそれる話をしますが、ここでは、熱抵抗をθjaとして考えることにします。熱抵抗は、θja以外にもθjcやψjtなどがあり、どの熱抵抗が実使用に近いのか疑問に思われるケースが多くあると認識しています。また各社各製品を見渡すと、全て記載していたり、いずれか一つしか記載がなかったりまちまちです。

本資料では、各種熱抵抗についての説明はテーマからそれるので割愛しますが、それぞれ定義が異なりますので、設計者はしっかりとこれら熱抵抗の種類について正しい認識を持っておくことが必要だと思います。

なぜなら、過剰マージンで高価な部品を選択したり、あるいは過小判断してマージンの少ない設計をしてしまい熱的な不具合に遭遇したりと様々な課題つながるからです。迷ったら、都度メーカー技術や各代理店技術にお問い合わせすることをお勧めします。

それでは本題に戻ります。

次は、Pallの損失を考えてみましょう。大きく3つの損失要素の合計と考えられます。

・入力バイアス回路部の損失:PD-IN

PD-IN=VDD1×IDD1

・出力バイアス回路部の損失:PD-OUT1

内部ロジック回路の動作電力であり、無負荷条件で測定します。なお、等価的には、内部回路のスイッチング損失と考えることができます。

PD-OUT1=(VDD2×IDD2)no-load+(VEE2×IEE2)no-load

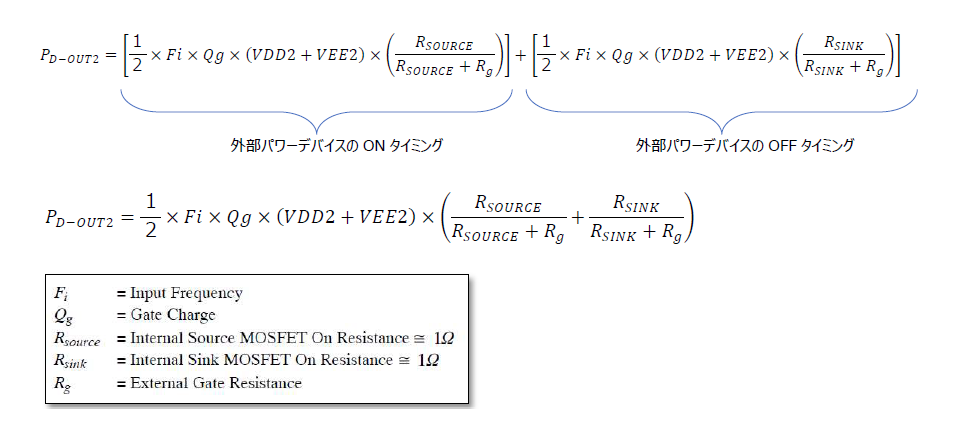

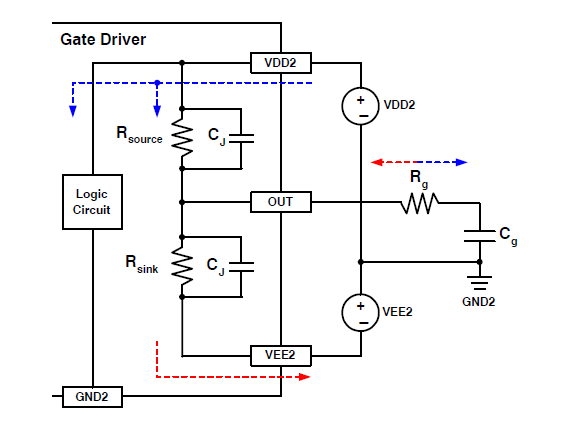

・出力駆動回路部の損失:PD-OUT2

ドライバーICの出力段MOSFETのオン抵抗と、外部パワーデバイスのゲート抵抗による損失の合計で構成されます。

参考までに、ドライバーICの出力段と外部パワーデバイスの電力経路イメージとして、下図8を参照ください。

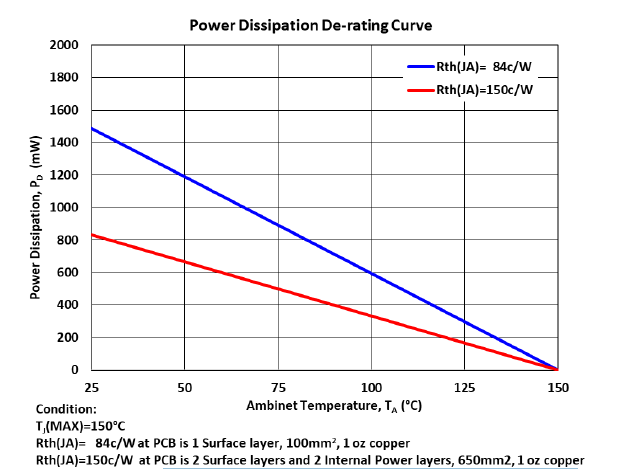

損失と熱のまとめると下記計算式を使って最大接合部温度Tj_maxが 150°C の場合、周囲温度 (TA) での最大許容消費電力 (PD) を計算することができます。

図9は、特定のPCBレイアウト、層、および表面積に基づく NCV57000シリーズの電力ディレーティング曲線を示しています。

その他、使用上のポイントになること

本記事に記載できなかった周辺部品の定数の決め方(計算式)など考慮するポイントが、オンセミ社のアプリケーションノートに記載されていますので、下記リンクより確認ください。

オンセミ社アプリケーションノート:AND9949-D.PDF

4. 磁気方式Galvanic Isolatedタイプ使用時のレイアウトで注意するポイントは?

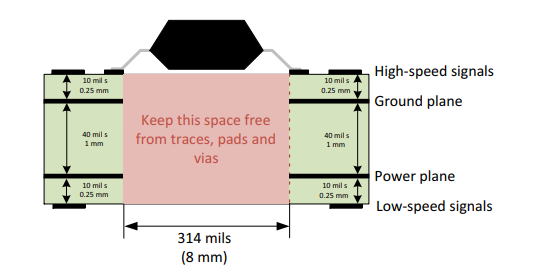

磁気方式Galvanic Isolatedタイプのゲートドライバーを使用する際、一次側信号を二次側へきちんと伝達させるために、磁気経路を確保することが重要です。よって、基板レイアウトにおいて、下記注意点と合わせて図 10を参照ください。

・多層基板において、ゲートドライバーの直下には、GNDパターンや信号パターン、ビアなどを配置しないこと

・ゲートドライバーが配置してある箇所の裏面には、他のICを配置しないこと

・DCDCなどに使用しているインダクター部品の近くに、ゲートドライバーを配置しないこと

その他、レイアウトでの注意事項については、オンセミ社のアプリケーションノート(AND9949-D.PDF)にも記載がありますので、参照ください。

さいごに

今回紹介した製品については、下記オンセミ社のリンクも確認ください。

・ゲートドライバー製品一覧ページ

・NCV57000データシート

お問い合わせ

本記事にて紹介した製品に、ご興味がある方は、ぜひお問い合わせください。

オンセミ メーカー情報Topへ

オンセミ メーカー情報Topに戻りたい方は以下をクリックしてください。