位相比較器

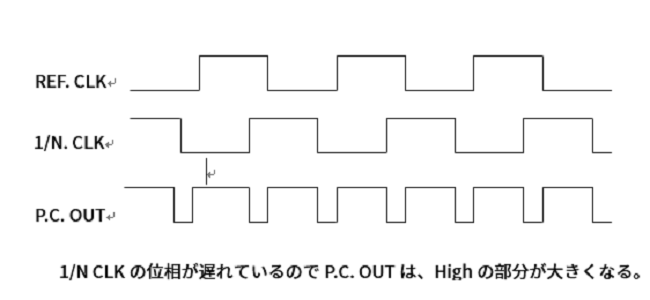

位相比較器は、入力されたREFCLKとVCO出力の1/N分周後の位相を比較することにより、VCO出力の位相進み/遅延を検出します。図3は、VCO出力がREFCLKから位相が遅れていることを示しています。図1で使用しているのは、三角波位相検出方式となりEOR等で簡単に構成することができます。Logicで構成するにはJ-K FF、RS FFを使用することもできます。

位相比較器と併用されるのがチャージポンプで、位相比較の結果によりコンデンサーに位相遅れの場合はチャージ、位相進みの場合はディスチャージをおこない位相比較情報を電圧に変換する場合もあります。無線通信では、位相の比較をおこなわず周波数同期のみおこなうケース(Frequency Locked Loop)もあり、使用用途によって構成もさまざまとなります。

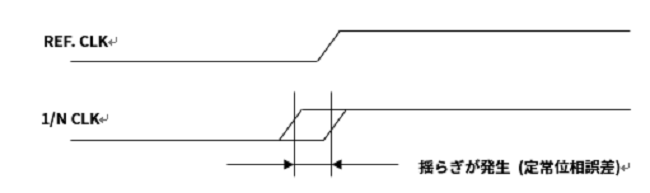

Analog PLLは、位相比較周波数の選定もPLL設計の重要な要素になります。比較周波数が低い場合、位相比較情報を更新する周期が長くなりPLLの引き込み時間に影響します。また、更新周期が長くなることによって、PLL自体が持つ定常位相誤差(Analog PLLは完全に位相が同期することはなく、ある一定の位相誤差を持つ)が大きくなります。

次回は、位相比較器の出力を平滑化するLow Pass Filterについて記載します。

お問い合わせ

本記事に関して、お問い合わせ、ご質問があれば以下のボタンからお願いします。

Microchip メーカー情報Topへ

Microchip メーカー情報Topページへ戻りたい方は、以下をクリックください。