検証に便利な機能を豊富に備えており、その検証機能の1つである拡張データフローについて紹介します。

機能の紹介

拡張データフローの機能

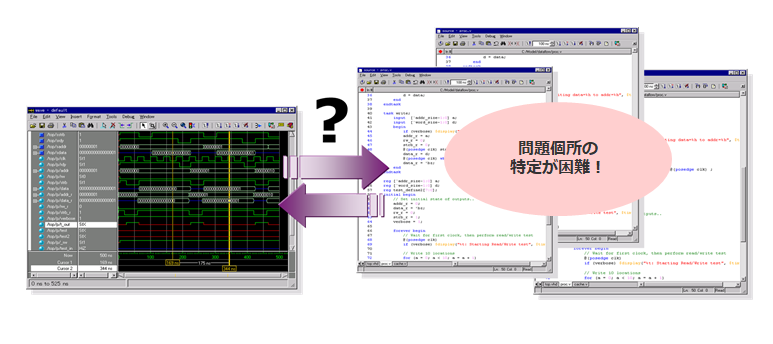

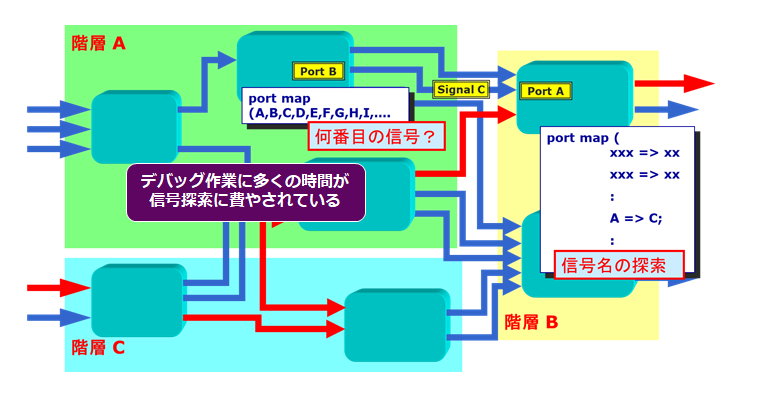

論理シミュレーションの出力波形に不具合を見つけた時に、どのように不具合原因の探索をおこなっていますか?

波形ベースのデバッグで、以下のようなことを経験されているのではないでしょうか?

● 問題を波形で確認したら、その信号をソース上で確認

● 波形とソースの往復によるデバッグ

● 記述量やファイル数の増加により、信号のトレースが困難に...

回路規模が大きくなると、論理段数や分岐が多くなるので、不具合原因の探索に時間がかかると思います。このような場合に、拡張データフローの機能を使用すると便利です。

拡張データフローは実際の解析フローに沿って紹介するとわかりやすいので、今回は出力ピンが X(不定)時の解析例で説明します。

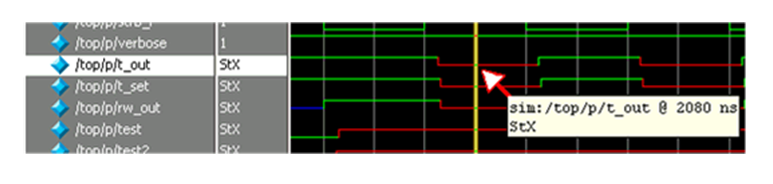

(1)波形ウィンドウの表示

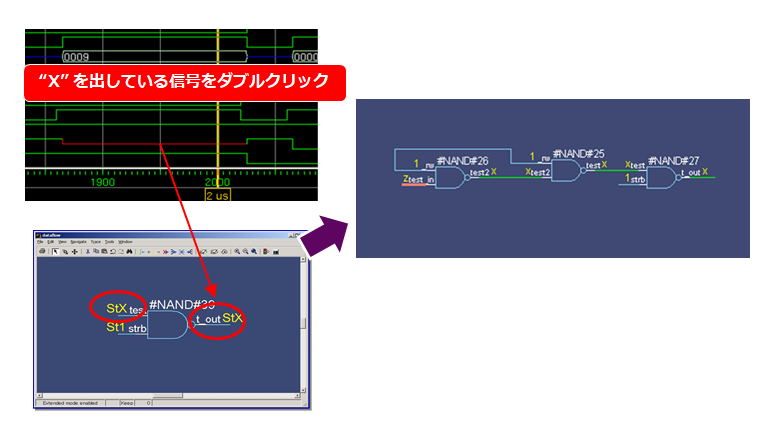

まず、シミュレーションを実行して波形ウィンドウを表示します。図3の波形を確認すると、信号 t_out が X(不定)になっています。この原因箇所を探索してみます。

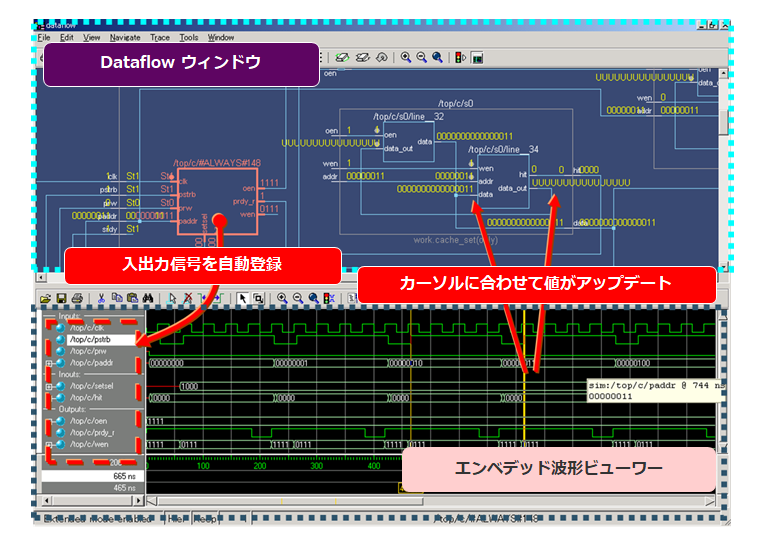

(2)データフロー・ウィンドウの表示

図3の矢印の波形が X(不定)になっているところをダブル・クリックすると RTL から自動的に、図4のように該当する回路図と信号だけの波形がすぐに表れます。これが、データフロー・ウィンドウです。該当する回路図だけを表示するのでわかりやすいと思います。

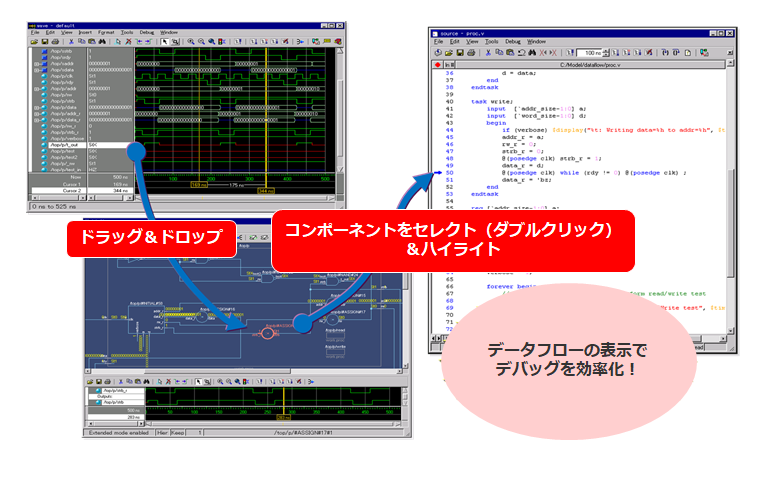

(3)データフロー・ウィンドウの回路図と波形のリンク

波形と回路図上の信号値はリンクされています。図4の下の波形にある黄色のボーダーを左右に移動させると、図4のように回路図上の信号値も同時に変化します。出力ピンの変化がどの入力ピンによる影響なのかがわかるので、時間のトレースバックによる原因特定に便利な機能です。

(4)回路図のバックトレース

NAND セルの出力ピンが X(不定)時には、入力ピンの片方が X(不定)になっています。その入力信号をクリックしていくと、更に回路図が展開されて図5の回路図になります。階層を経由しても、自動的に階層間を探索します。このように、データフロー・ウィンドウは、デザインの物理的な接続関係を調べるために使用します。プロセスからプロセスへと表示を展開していくことによって、接続が確認できます。

(5)不具合原因の特定

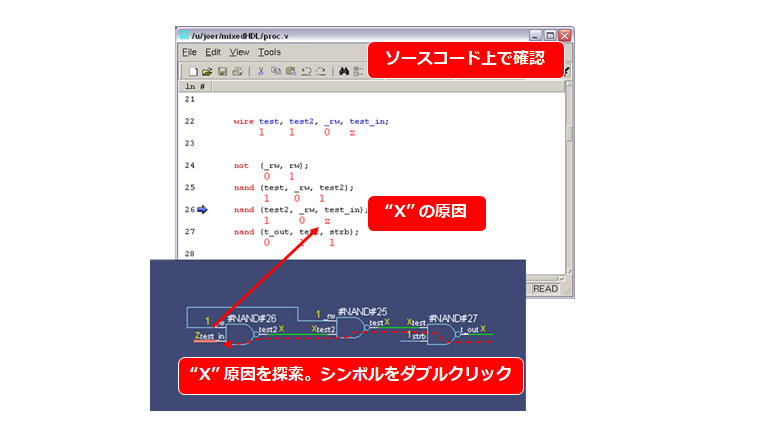

図5の NAND セルの入力ピンの Hi-Z まで展開すると、この先へは回路図を展開しませんので、この NAND セルを調べます。

(6)RTL 記述の確認

回路図上の NAND セルをダブルクリックすると、自動的に RTL のウィンドウが開いて、該当する行が表示されます。回路図で Z になっている test_in ピンが浮いていることが RTL の解析で判明します。これで、信号 t_out の X(不定)の原因が test_in ピンが浮いていることだとわかります。

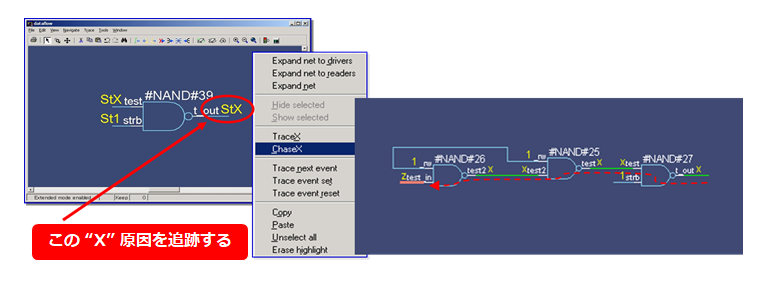

(7)ChaseX 機能

上記はマニュアルで X の原因を探索しましたが、自動的に X の原因箇所まで探索する機能があります。NAND セルの出力ピン X を選択して、ChaseX を実行すると自動的に信号経路を探索して、NAND セルから NOR セルまでの回路図だけを展開します。不要な信号経路の回路図は表示されませんので視認性の高い回路図です。

拡張データフローの主な機能をまとめると、以下のようになります。

● RTL から該当する信号周辺の回路図を自動生成

● 波形 ⇔ 回路図 ⇔ RTL の相互リンク

● 時間のトレースバックによる原因の特定

● 不定値 X のバックトレース機能

関連情報

セミナー/ワークショップ

▶ [オンラインセミナー] ModelSim によるアサーション検証 <無料>

Questa Sim / ModelSim のデバッグ機能であるアサーションベース検証(ABV)やコード・カバレッジ、拡張データフローの効果を紹介するセミナーです。特に、アサーションベース検証は FPGA デザインの半数以上で活用されているお勧めの検証手法です。

▶ 関連のイベント・セミナー

お問い合わせ

メーカー情報 Top へ

メーカー情報 Top ページへ戻りたい方は、以下をクリックください。

シーメンス(Siemens)が所有する商標や登録商標:こちら