検証に便利な機能を豊富に備えており、その検証機能の1つであるアサーション・ベース検証についてご紹介します。

回路規模や設計の複雑さの増大により、FPGA 開発業務の中心は設計から検証に移っています。アサーション・ベース検証は、既に ASIC で多く利用されている検証手法で、FPGA 開発でもお勧めする検証手法の1つです。

従来の検証方法

検証の種類

● シミュレーション

● 実機検証(実機デバッグ)

論理完成後にシミュレーションを実施し、FPGA 内部の配置配線後に実機動作確認を行います。修正や変更は設計の初期段階に完了しておくことが理想的で、シミュレーションで論理のバグを潰しておくことが、とても重要です。

シミュレーションの特長

入力ベクターに対して、出力される結果が期待値どおりか否かを確認します。検証対象の論理回路はブラック・ボックスとして検証され、出力に問題があった場合にバック・トラックして問題箇所を絞り込んでいきます。

従来のシミュレーション手法における問題

昨今、システムの高機能化に伴い、設計が複雑化傾向にあります。回路規模が大きくなると、従来のシミュレーションによる検証ではいくつかの問題が発生します。

(1)内部バグを見落とす可能性が高い!

論理段数が深くなったり クロック系統が複雑になると、信号経路が複雑になります。信号経路が複雑になると、回路内部で発生した誤信号が後段ブロックでマスクされて、誤信号が出力ピンまで伝播しないことがあります。出力ピンに誤信号が現れないと、論理シミュレーションでバグを見つけるのは困難です。

出力ピンの波形で検証するので、内部バグを発生できるテストベンチ(各ブロック検証用のテストベンチ)だけでなく、その信号を出力ピンまで伝播させるテストベンチが必要になります。

このような検証手法で開発した製品は、市場に出てから様々な信号の組み合せを試されると検証時には見つからなかったバグが発覚して問題になることがあります。

(2)デバッグ工数の増加

運よく出荷前の実機検証で不具合を発見できても、論理段数や分岐数、クロック数が多い回路でバグを探索するデバッグ作業は大変です。その理由は、不具合現象が見つかったポイント(出力ピン)とその原因となった不具合箇所は 時間 と 場所 が異なるのと、論理設計時の信号の流れ と デバッグ時の信号解析の流れ は 逆方向 になるからです。

特に、FPGAの実機検証でバグが見つかると、修正のたびに長時間のコンパイル作業が必要になるので開発遅延につながります。メイン機能は修正の簡単なシミュレーターで検証、コーナー・バグやシステムの検証は高速なFPGAを使った実機で検証されることをお勧めします。

アサーション・ベース検証(ABV)

RTL シミュレーションによる課題に対して注目されているのが、アサーション・ベース検証(ABV)です。

アサーション・ベース検証は、回路内部やインターフェース部に内部信号の振る舞いを予め定義しておき、回路が仕様どおりに動作することを自動的に監視させる検証のことです。回路内部の振る舞いを検証できるので、ホワイト・ボックス検証とも言われています。FIFO のオバーフローやアンダーフロー、ステートマシンの割り込みやリセット、アービトレーションの公平性などの誤動作しやすい箇所や、RTL 内のコメントを入れているような条件をアサーション制約で定義します。

結合テストで誤動作した自分のブロックを必死で解析したら、他の人が作成した前段ブロックのバグが原因だったと言う事を過去に経験したことはないでしょうか。このような無駄な解析作業を避けるために、各ブロックの入力部にアサーション制約を設けて入力信号を自動監視させると便利です。

品質向上と検証工数削減に有効なアサーション・ベース検証の特徴をまとめます。

(1)自動検証で検証漏れを防ぐ

モニターピンによる内部検証と違って、アサーション・ベース検証は自動で監視します。

アサーションで期待動作を記述するため、期待動作と異なる結果が出た場合、シミュレーターがエラーとして表示します。ツールがエラーを出すたため、目視による検証漏れを防ぎ、検証工数を大幅に削減できます。

(2)デバッグ工数の増加

運よく出荷前の実機検証で不具合を発見できても、論理段数や分岐数、クロック数が多い回路でバグを探索するデバッグ作業は大変です。その理由は、不具合現象が見つかったポイント(出力ピン)とその原因となった不具合箇所は時間と場所が異なるのと、論理設計時の信号の流れとデバッグ時の信号解析の流れは逆方向 になるからです。

特に、FPGA の実機検証でバグが見つかると、修正のたびに長時間のコンパイル作業が必要になるので、開発遅延につながります。メイン機能は修正の簡単なシミュレーターで検証し、コーナー・バグやシステムの検証は高速な FPGA を使った実機で検証されることをお勧めします。

(3)内部信号の振る舞いを定義することで検証項目を明確化

検証項目が明確でないと、信号の振る舞いとなるアサーション制約をどこに定義すべきか迷います。アサーション制約を導入する作業は面倒に感じますが、実はこの作業が最も重要です。

(4)不具合箇所の近くで検証するので、バグの探索が速い

デバッグ工数の大半はバグの修正ではなく、バグの探索に費やされます。

論理シミュレーションや実機検証で不具合を発見したら、不具合信号の上流の懸念箇所にアサーション制約による罠を仕掛けて、不具合の原因を早期に特定できます。該当機能へはアサーション機能を設けることを、社内の設計基準に追記します。この作業の繰り返しが社内の設計品質を向上させるためにとても重要です。

アサーション・ベース検証を導入すると検証を意識して設計するので、社内の設計品質が向上するだけでなく、デバッグ工数が大幅に少なくなります。

<< 制約の書式は非常にシンプル >>

アサーション・ベース検証を行うには内部動作の振る舞い(機能の仕様)を定義する必要があります。アサーション制約の定義は従来の Verilog や VHDL でも使えますが、SystemVerilog (SVA) や PSL (Property Specification Language) の専用言語を使うと記述をシンプルにできます。

[例1]

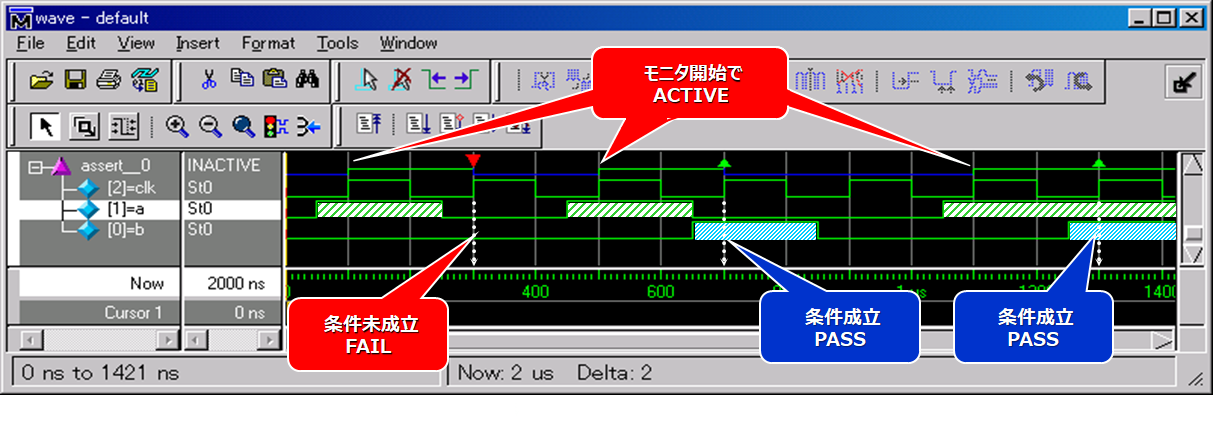

この例は svademo01 という module 内にアサーションを記述したシンプルな例です。このアサーションは、「a=1 が成立した次のサイクルで b=1 が成立する」という内容です。@(posedge clk) とあるので、クロックの立ち上がりで各信号の値をチェックする仕様になっています。波形で見ると、a=1 でチェックが開始され、次のサイクルで b=1 にならなければ FAIL、成立すれば PASS となっていることがわかります。

[例2]

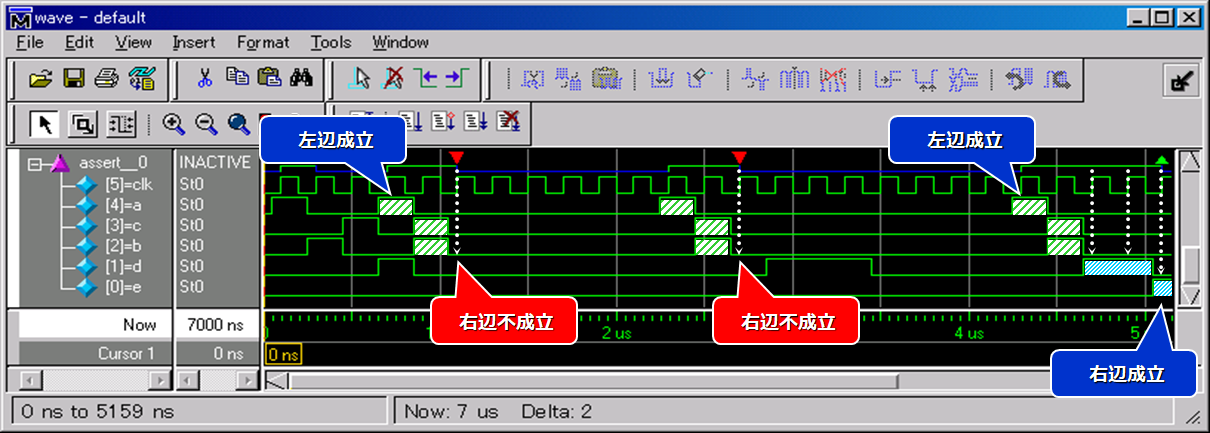

次の例は svademo02 という module ではなく、program となっており、アサーション記述を別ファイルで記述するスタイルとなっています。

アサーションの内容は、「左辺の a=1 の1サイクル後に b=1、c=1 の事前条件が成立した次のサイクルで、右辺の d=1 を2回繰り返した後の次のサイクルで e=1 の事後条件が成立する」という内容になります。こちらも、@(posedge clk) とあるので、クロックの立ち上がりで各信号の値をチェックする仕様になっています。

波形で見ると、 左側と真ん中の波形は事前条件は成立していますが、事後条件が成立していないため FAIL となっています。右側の波形は事前条件と事後条件が成立しているので PASS となっていることがわかります。このように、いくつかの信号の状態を事前条件や事後条件として組み合せることもできます。

<< アサーション・エラーの解析 >>

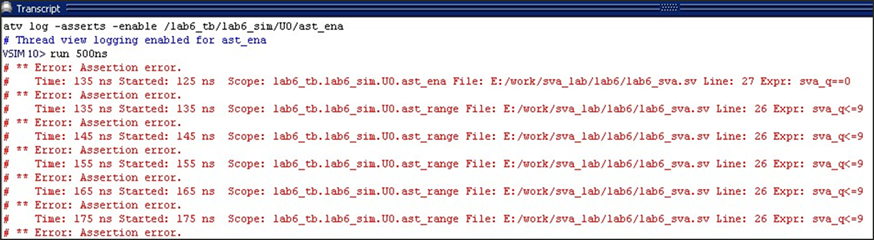

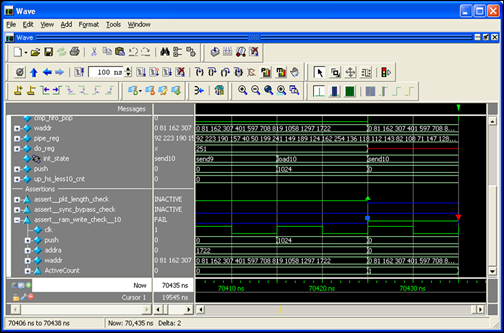

GUI を使用したアサーション検証では、シミュレーションの実行後に Transcript ウィンドウにアサーション・エラーが表示されます。

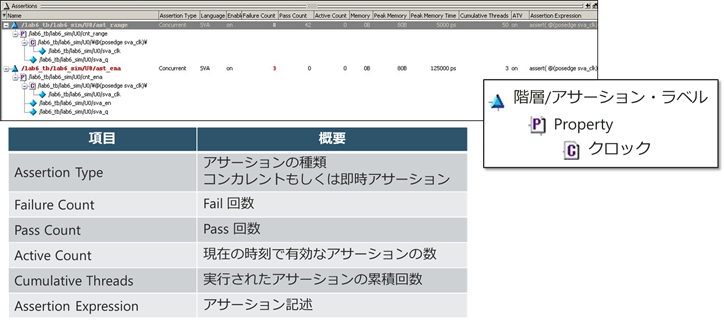

Assertions ウィンドウには、シミュレーション後に結果が反映されます。

Wave ウィンドウには波形結果が表示され、アサーションの PASS / FAIL が表示されます。

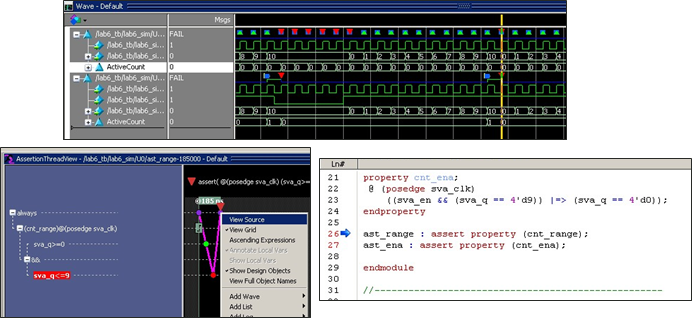

Questa / ModelSim にはバグの解析に便利な機能、アサーション・スレッド・ビュー(ATV)があります。この ATV は、シンプルな制約を分割してデバッグする機能です。下図のように1行で定義した部分の何処にエラーがあるのか簡単にわかります。

アサーション・エラーの原因をこれらの GUI で用意された機能を使用して解析することができるので、デバッグも容易に行えます。

関連情報

▶ アサーション・ベース検証

▶ コードカバレッジ

▶ 波形比較

▶ 拡張データフロー

セミナー/ワークショップ

▶ [オンラインセミナー] ModelSim によるアサーション検証 <無料>

Questa / ModelSim のデバッグ機能であるアサーションベース検証(ABV)やコード・カバレッジ、拡張データフローの効果を紹介するセミナーです。特に、アサーションベース検証は FPGA デザインの半数以上で活用されているお勧めの検証手法です。

▶ 関連のイベント・セミナー

お問い合わせ

メーカー情報 Top へ

メーカー情報 Top ページへ戻りたい方は、以下をクリックください。

シーメンス(Siemens)が所有する商標や登録商標:こちら