はじめに

こんにちは!なみぃです。ついに二年目社員となり焦ってきました。

前回は Hyper-Registerを用いた Hyper-Retiming という新しい機能についての記事を書きました。

今回も Hyper-Register を使用した機能の紹介です。

念のため Hyper – xx の復習を…。

【HyperFlex】

Stratix® 10 から導入された FPGA のパフォーマンスを上げる仕組み全体のこと

【Hyper-Retiming、Hyper-Pipelining、Hyper-Optimization など】

実際にパフォーマンスを上げるために働くデバイス構造や機能

【Hyper-Register】

上記の機能を実現するために Stratix 10 から導入されたレジスタ

今回は機能の一つである Hyper-Pipelining を紹介します!

まだ前回記事を読んでない方はぜひとも「Stratix 10 新機能~Hyper-XX の謎 (Hyper- Registerとは?)~」と

「Stratix 10 新機能~Hyper-XX の謎 (Hyper-Retiming とは?)~」を読んでから今回の記事を読み進めてみてください。

まずはパイプライン化について少し説明します。

パイプライン化とは?

クリティカル・パスにレジスタを挿入し遅延のバランスを取ることで、性能を向上させる手法です。

【例】

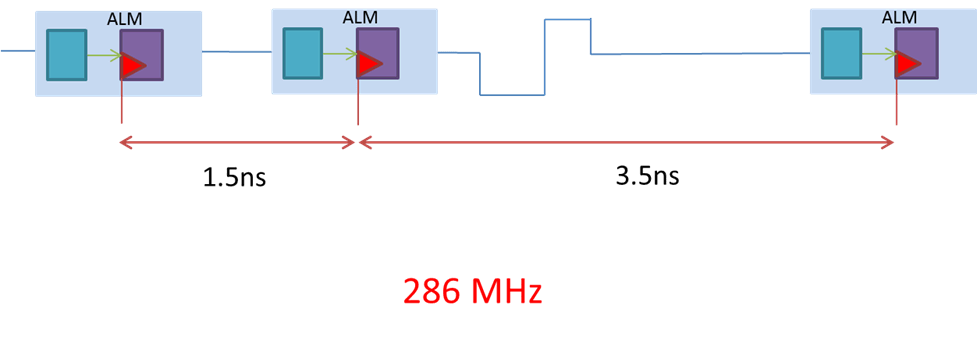

今回も前回同様、FPGA を 300 MHz(3.3ns) で動作させたいとします。その場合、データは 3.3ns 以内に ALM レジスタ間を伝搬する必要があります。今、ALM が図.1 のように接続しているとします。

それぞれのレジスタ間の遅延が 1.5ns と 3.5ns です。この状態だと3.5ns の遅延が発生し、動作周波数は 286MHz となり希望動作周波数(300MHz)を満たしません。ここまでは前回と同じですね。

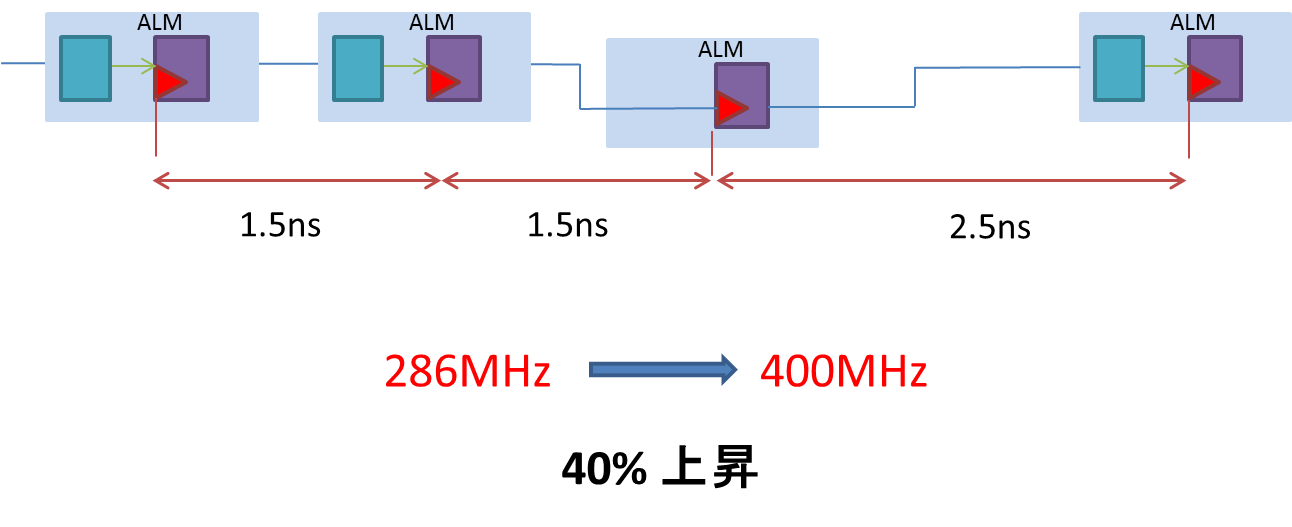

ここで、パイプライン化を行います。

Quartus® を使用しコンパイルすると、クリティカル・パスに対してタイミングの最適化が可能な位置にある未使用のALMレジスタにパイプライン・レジスタが自動で配置されます。パイプライン・レジスタを追加したことにより下記のようにタイミングを満たすことができました。

パイプライン化について学んだ時、私はこう思いました。

「Retiming と何が違うというのだ…?」

私以外にもこう思った方はいるでしょう。

しかしこの2つには大きな違いがありました。

Retiming ではレジスタの位置を変えるだけなのでレイテンシに変更はありませんが、パイプライン化ではレジスタの挿入をするので、それに伴ってレイテンシが増加してしまいます。つまり図.1 では 3サイクル後に演算結果が出力されていましたが図.2 では 4サイクル後に出力されることになります。

ただし、パフォーマンスの改善率は Retiming よりパイプライン化の方が高いという利点が!

しかし、リソース使用率が高くすでに多くの ALM が使われている場合はパイプライン・レジスタの追加が行えません。

それでは、ここで今回の本題である Stratix 10 の Hyper-Pipelining についてみていきましょう!

Hyper-Pipelining

Hyper-Pipelining とはパイプライン・レジスタを Hyper-Retimer (ALM register の代わりに Hyper-Register を使用する機能) によって最適な位置の Hyper-Register に再配置することでレジスタ間の配線遅延のバランスを取りクリティカル・パスを解消し、動作周波数 (パフォーマンス) を向上させる機能です。

ただ、パイプライン・レジスタをどこのパスに追加すればよいか分からない、とお困りの方もいるかもしれません。

そんな方でもご安心ください。何と Hyper-Pipelining によるレジスタの追加箇所はツールが自動で判断してくれます!Quartus ありがとう。

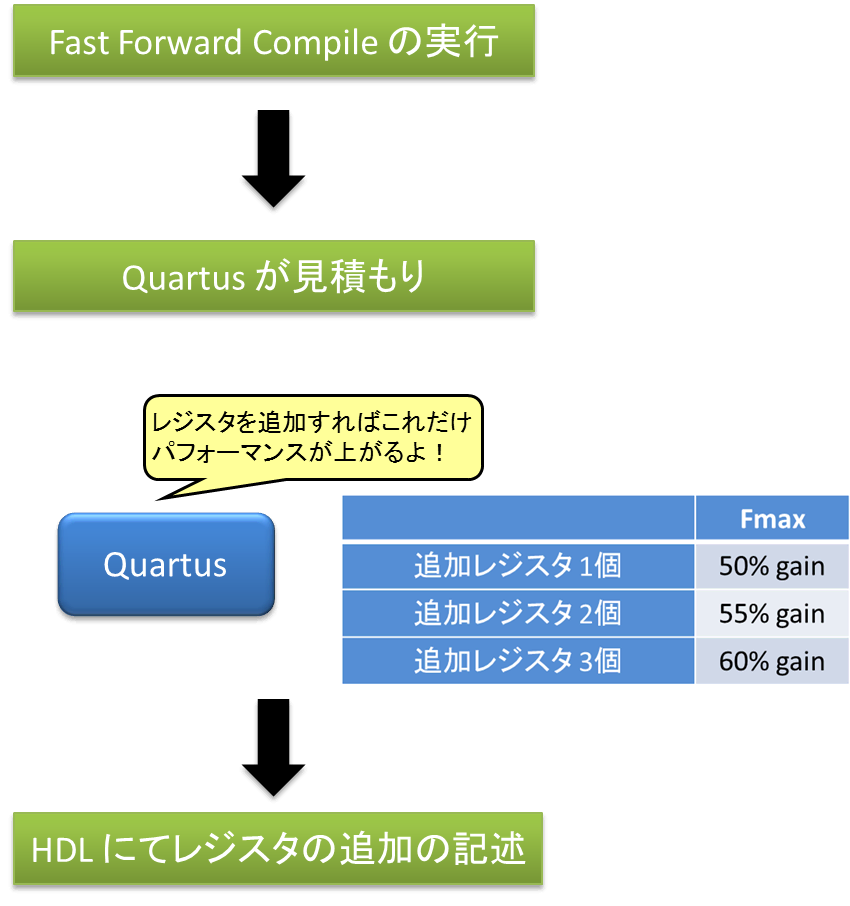

まずそのためには Fast Forward Compile というフローを行います。そうしますと Quartus がレジスタを何段追加すれば、どれだけパフォーマンスが上がるのかを見積もってくれます。その後、HDLの記述にてクロックドメインの前後やデザインの入出力にパイプライン・レジスタを希望の数だけ追加することでツールが自動的にレジスタを最適な位置に配置してくれます。

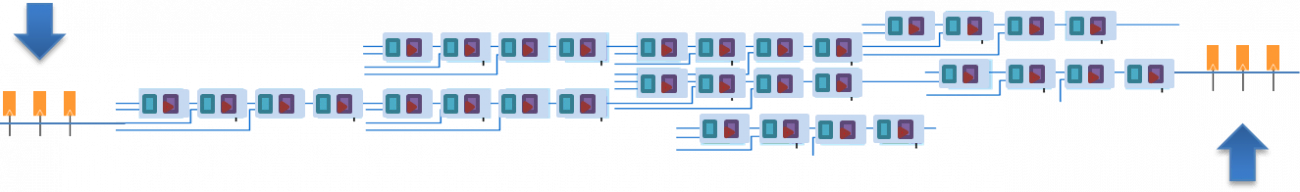

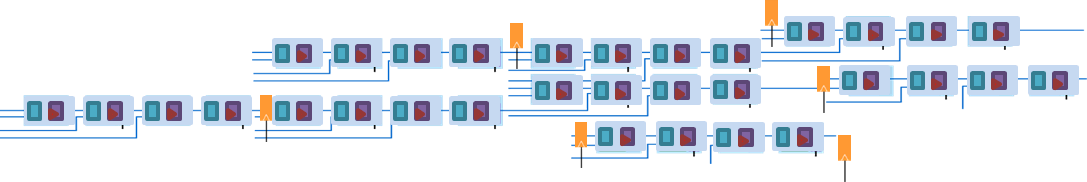

そして、追加レジスタは図.5 のように最適なパスへ移動してくれます。

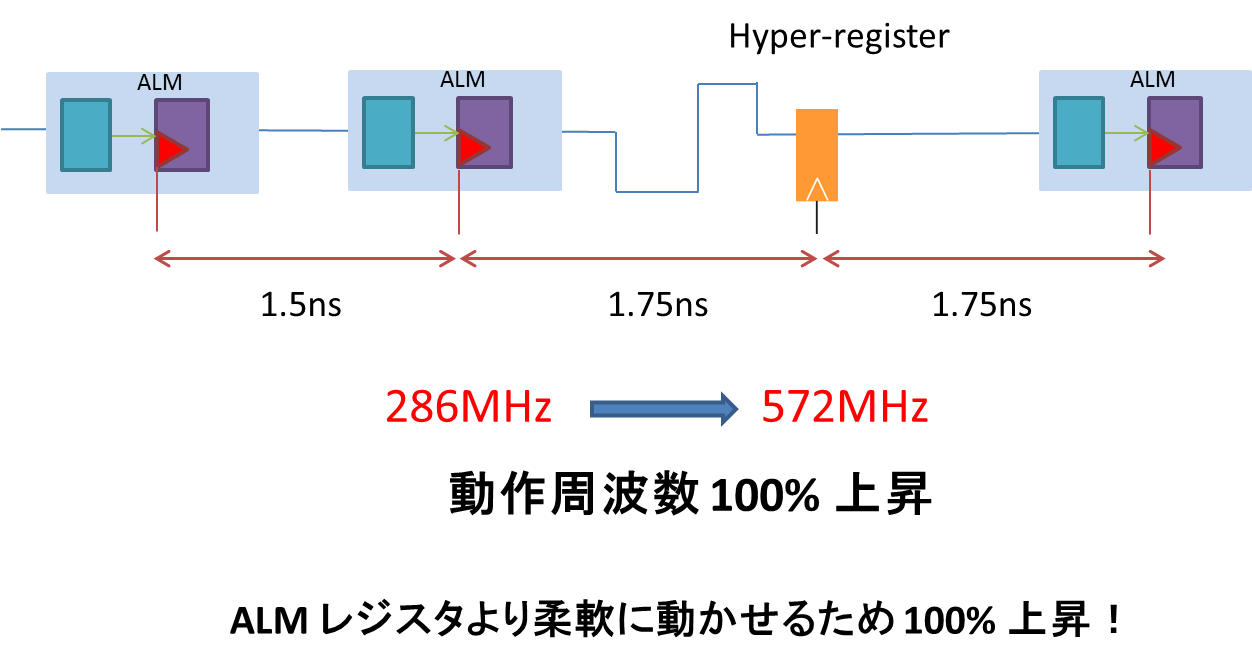

移動した Hyper-Register は図.6 のように作用し、パフォーマンスの向上を行ってくれます。

従来のパイプライン化では改善後は 400MHz であったのに対してHyper- Pipeliningを使用すると 572MHz まで動作周波数を向上させることができました!

また、レイテンシは増えていますが、デザイン全体で見ると Hyper-Retiming よりタイミングの改善率が高くなっています。

このようなフローで Hyper-Pipelining を使用してパフォーマンスを向上させることができます!

まとめ

Hyper-Pipelining のメリット

1.ALM レジスタより柔軟に配置ができるためタイミングの改善率が高い(Hyper-Register の使用)

2.ALM の使用率に依存しないタイミングの改善が可能(Hyper-Register の使用)

3.レジスタの移動はツールが自動的に判断し行ってくれる

Hyper-Pipelining は Hyper-Retiming だけでは目的の動作周波数を満たせなかった時に使用します!