はじめに

こんにちは!なみぃです。

前回は Stratix® 10 FPGA の HyperFlexTM という新しい仕組みを実現するためのHyper-Register についての記事を書きました。

今回はその続きです。

念のため Hyper–xx の復習を…。

・HyperFlex

Stratix 10 から導入された FPGA のパフォーマンスを上げる仕組み全体のこと

・Hyper-Retiming、Hyper-Pipelining、Hyper-Optimization など

実際にパフォーマンスを上げるために働く機能

・Hyper-Register

上記の機能を実現するために Stratix 10 から導入されたレジスタ

今回は機能の一つである Hyper-Retiming について書きます!

まだ前回記事を読んでない方はぜひとも

【Stratix 10 新機能~Hyper-XX の謎 (Hyper-registerとは?)~】

を読んでから今回の記事を読み進めてみてください。

Hyper-Retiming の話の前に従来の Retiming 機能について…。

Retiming とは?

Retiming とはALM レジスタ間の遅延のバランスを取りクリティカル・パスを解消することで性能を向上させる Quartus® Prime の機能です。

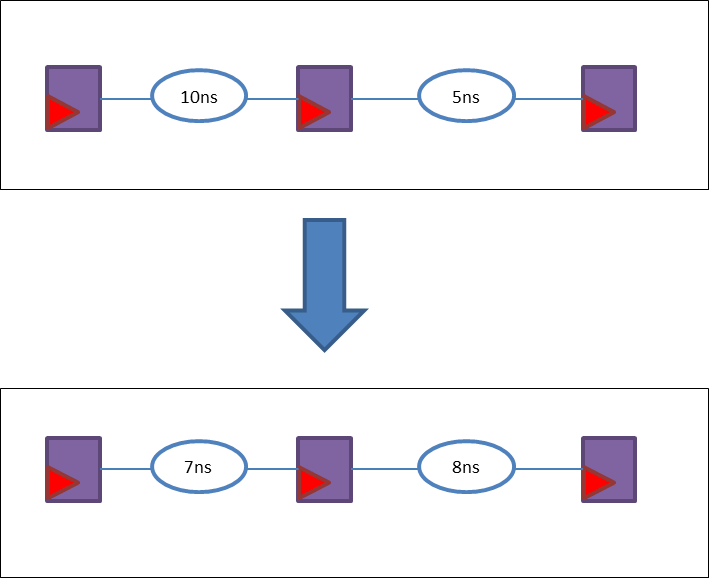

図.1 のように論理機能は変更せずにレジスタを移動させることでタイミングを満たしていないパスの遅延を少なくすることができます。

その他、配線遅延が長い場合は遅延を短くするようにレジスタを移動させたりもします。

【例】

仮に、FPGA を 300MHz(3.3ns)で動作させたいとします。

その場合、データは 3.3ns 以内に ALM レジスタ間を伝搬する必要があります。

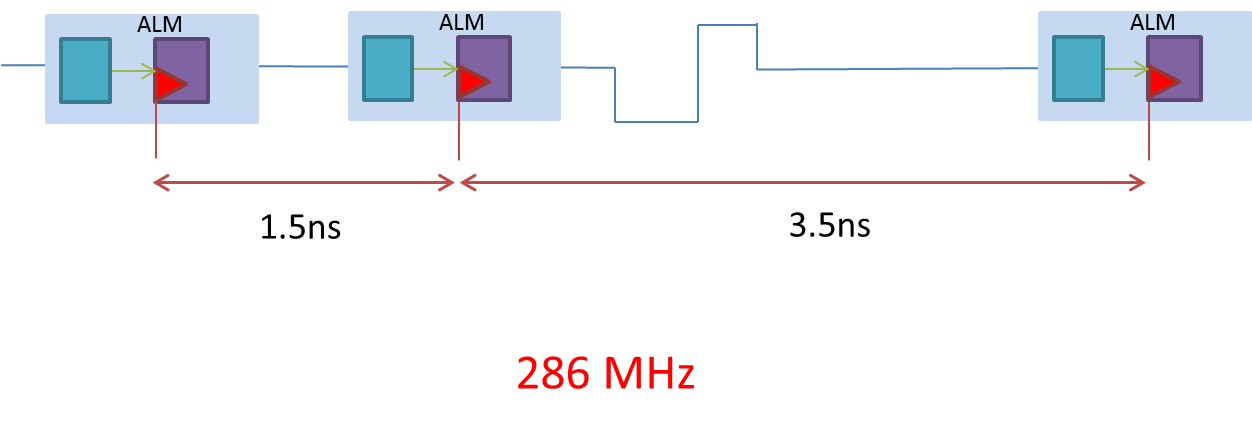

今、ALM が図2 の図のように接続しているとします。

それぞれのレジスタ間の遅延が 1.5ns と 3.5ns です。

この状態だと 3.5ns の遅延が発生し、動作周波数は 286MHz となり希望動作周波数(300MHz)を満たしません。

こんな時に Retiming 機能を使います!

具体的にはクリティカル・パスの最適化が可能な位置にある、未使用の ALM レジスタを利用してタイミングの改善を行います。

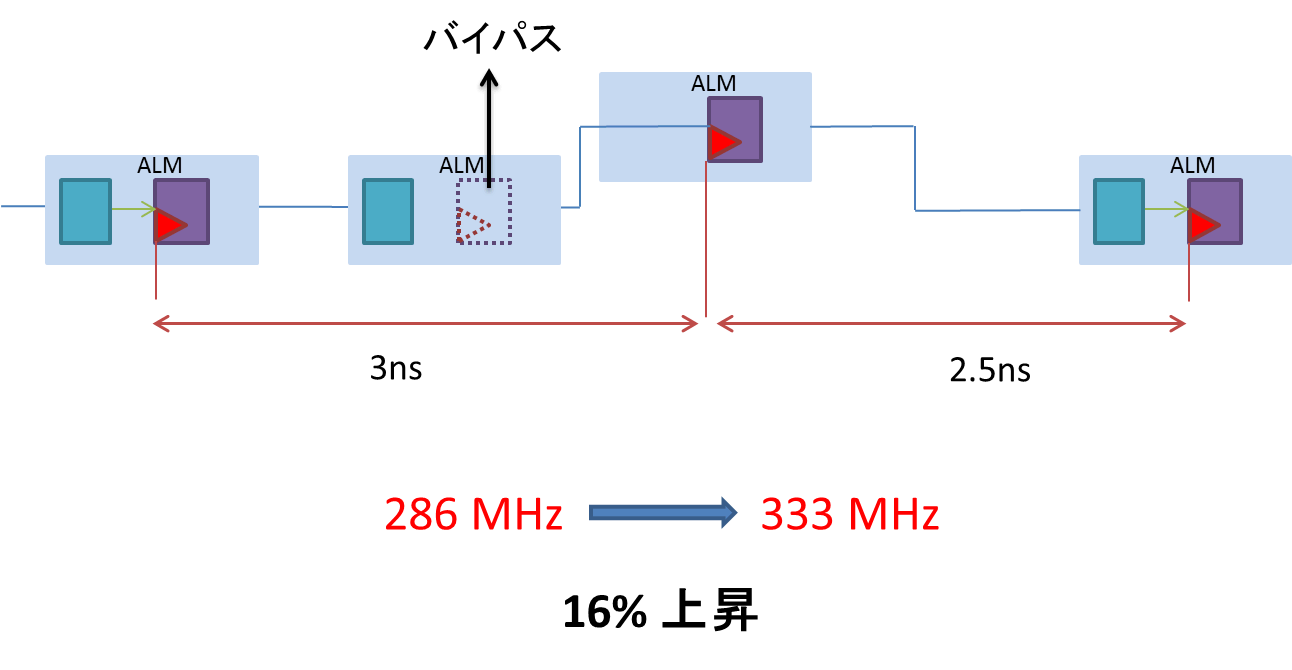

このようにして希望動作周波数を満たすよう調整してくれます(図3)。

上記の例ではタイミング改善を行うことができましたが、リソース使用率が高くすでに多くの ALM が使われている場合はタイミングが改善できないこともあります。

また、もっと動作周波数を上げたいという希望もあるかと思います。

そこでついに Hyper-Register を使用した Hyper-Retiming の出番です!

Hyper-Retiming とは?

Hyper-Retiming とは

Hyper-Register を使ってレジスタ間の配線遅延のバランスを取りクリティカル・パスを解消し、

動作周波数 (パフォーマンス) を向上させる機能です。

Hyper-Retiming の方法は以下2つです。

【1】レジスタの配置のみを変えてパフォーマンスを向上

【2】組み合わせ回路とレジスタの順序も変えてパフォーマンスを向上

【1】レジスタの配置のみを変えてパフォーマンスを向上

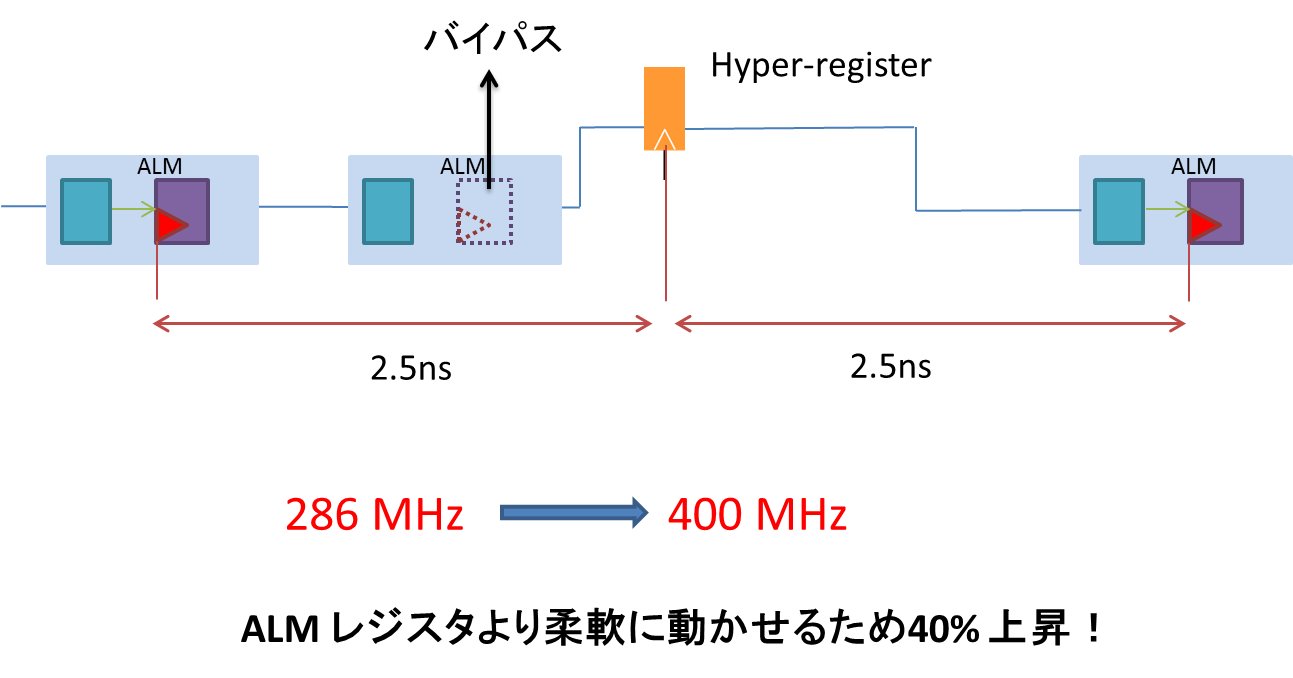

Hyper-Register を使うと図4 のようになります。

先ほどとは異なり配線上にある Hyper-Register を使っています。

結果、従来の Retiming では改善後は 333MHzであったのに対してHyper-Retiming を使用すると 400MHz でも動かせるようになりました!

前回記事で書いた通り Hyper-Register は非常に豊富に配置されているのでちょうど良い位置の Hyper-Register を使えます。

だから、先ほどよりタイミングの改善率が高いのです!

更に Hyper-Register は ALM レジスタとは別に配置されているため仮に全ての ALM が使われている場合でも Retiming 可能です!

【2】組み合わせ回路とレジスタの順序も変えてパフォーマンスを向上

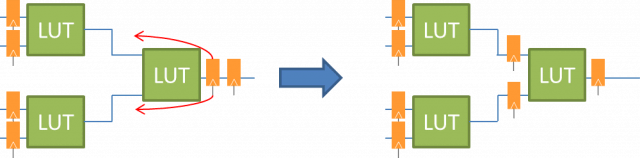

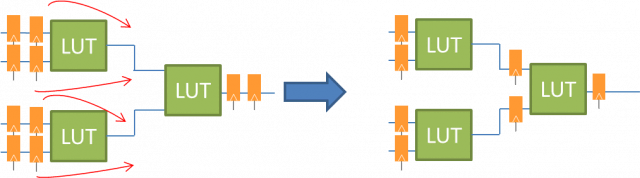

Hyper-Retiming 機能では組み合わせ回路とレジスタの順序を変更することでパフォーマンスを向上させる場合もあります。

例えば LUT 二段部分がタイミングを満たせていない場合は二つの LUT の間にレジスタを移動することでパフォーマンスを向上させます。

Retiming によりレジスタを論理の上流に移動させることを Backward Retiming、レジスタを下流に移動させることを Forward Retiming と呼びます。

この機能のメリットはファンクションを維持したままパフォーマンスを向上させられるという点です。

図.5 、図.6 のように、レジスタを組み合わせ回路の前後に移動させることによって遅延を減少させます。

Hyper-Register はこのように柔軟性を活かして機能しているのですね!

しかし、そんな Hyper-Register にも注意点が…。

Hyper-Retiming 使用時の注意事項

便利な Hyper-Retiming ですが使用する際に注意しなければいけないことがあります。

例えば、非同期クリア使用時には Retiming ができなかったり初期値が維持できないことがあります。

そのため、Hyper-Retiming が有効にならないケースについてまとめました。

Retiming できない箇所

・非同期クリア付きレジスタ

・シンクロナイザー・チェイン

・I/O との境界のレジスタ(Virtual pin 設定も同様)

・非同期クロック・ドメイン間のパス

・SDC 制約でディスティネーションに指定されているレジスタ

・Synt hesis attribute “preserve” が宣言されているレジスタ

・RAM/DSPs ブロック

・Latch

詳細は以下、資料の「Facilitate Register Movement (Hyper-Retiming)」の項目をご参照ください。

Hyper-Register が有効にならずパフォーマンスの向上が得られなかった場合でも上記の何がネックになっているかを Quartus Prime で確認することができますので対策を立てることができますね!

Stratix 10 High-Performance Design Handbook:

また、Hyper–xx について詳しく知りたい方もこちらをご覧ください。

まとめ

Hyper-Retiming のメリット

1. ALM レジスタより柔軟に配置ができるためタイミングの改善率が高い

2. ALM の使用率に依存しないタイミングの改善が可能

記事で書く予定の残りの機能は

・Hyper-Pipelining

・Hyper-Optimization

です。

次回は「Hyper-Pipelining」について紹介予定です。

お楽しみに!