マルチコアCPUを高速実装させるブリッジの活用

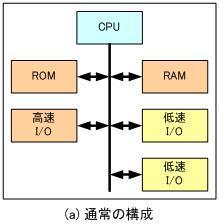

FPGAは実装率が高くなると動作速度が上げにくくなるというのはご承知の通りです。マルチコアCPUも例外ではありません。そこでマルチコアを組み込む前に、ソフトコアCPUを高速実装するノウハウを1つお教えします。図 3(a)はソフトコアCPUでモジュール設計する際の一般的な構成です。1つのバス上にメモリや高速/低速のI/Oが全て接続されています。ベンダーのサポートツールはCPUをとりまくハードウェアを全て1つのモジュールとした論理を生成します。この構成が良く解らない方は前回の解説やベンダー提供のドキュメントを参考にして下さい。

一般的にI/OモジュールはCPUに比べてその動作速度が遅いので、高速バスに接続する必要はありません。更に機能(I/O)を追加していくとCPUも含めたモジュールの論理規模が大きくなり、その結果CPUの動作速度が低下してしまいます。そのままの構成で目標性能を達成できた場合は良いのですが、もしツールを駆使しても達成できなかった場合、論理に手を加えるしかありません。

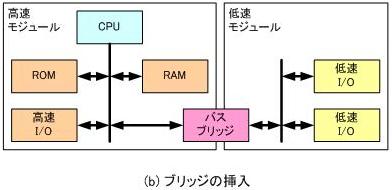

その場合私は図 3(b)に示す様に高速動作と低速動作部分をモジュールとして分け、その間をバスブリッジで接続する手法をとっています。これはSoC(System On Chip)ではごく当たり前に行われています。モジュール分割することでチューニングもし易くなり、開発工数を抑えながら高性能な論理を実現することができます。

図 3 ブリッジによる低速I/Oの分離

ただバスブリッジを用いる事で1つ問題が出ます。それはCPUからはバスブリッジが1つの大きなアドレス空間として見えるので、その先にある低速I/Oの存在が隠れてしまい、その結果たとえ標準提供のモジュールを使用していても、ソフトウェアのヘッダファイルやアクセスする標準関数が生成されないのです。その対策として低速I/Oを同じアドレスに配置した図 3(a)の構成でプロジェクトを作成しソフトウェア開発用にはそちらを使用します。2度手間に見えるかもしれませんが、手作業で行うよりも正確で高効率ですので、目標性能を達成するための不可欠な作業として捉えて下さい。

バスブリッジの採用には、割り込みやバースト転送の取り扱い他、色々検討しなければならない事がありますが、今回はその説明は割愛させて頂きます。

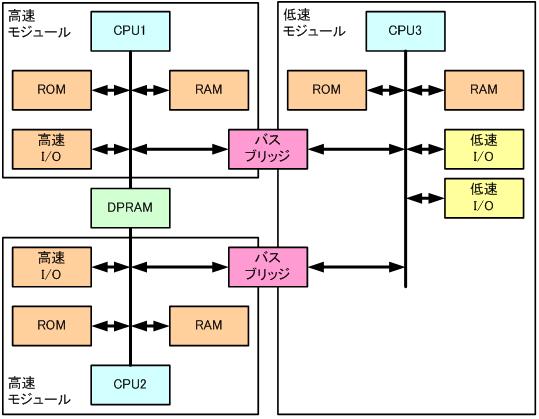

図 4にバスブリッジを活用した3CPUでの構成例を示します。高速モジュール間通信には共有メモリとしてDPRAMを用いています。また低速I/Oの制御用にもCPUを実装し、高速モジュールの負荷を更に低減しています。これまでの解説を理解頂ければ、詳細説明は不要でしょうし、「マルチコアCPUのシステムを設計するのはそれ程難しくない」と感じて頂けたのではないでしょうか。

ただ機能分散によるシステム設計は自由度が高く要求仕様により近い構成が可能ですが、その分基本設計には深い検討が必要になります。この検討を怠り安易に設計してしまうと、プロジェクト自体が爆発してしまう危険もありますので、その点だけは十分に注意して下さい。

図 4 3CPUによる機能分散構成例

このバスブリッジを介した機能分散が実現できれば、CPUはFPGA内部/外部を問いません。つまり高速モジュールの一方もしくは全てが市販マイコンでも同様の構成が可能です。言い換えればFPGAの柔軟性があるからこそどの様なシステム構成でも実現できるのです。

おわりに

どうでしょう、ソフトコアCPUをハードウェアの側面から解説してきましたが、おもしろそう、もしくは使ってみようと思って頂けたでしょうか?システム設計者の皆さん!現在自分が担当しているシステムを何の制約も無しに1から設計したら、今採用している構成とどの程度違ってくるのか一度考えてみて下さい。資産の流用とか設計期間短縮とかの言葉に翻弄され、ユーザにとって真に良い物を提供するというメーカの本質からはずれた設計をしていませんか?

設計自由度が高く要求仕様により近い解を導けるソフトコアCPUとFPGAの組合せは「ユーザオリエントなSoCがミニマムオーダ1個から実現できる唯一の選択肢」なのです。

今回でハードウェアの話は終了し、次回よりソフトウェア編に移る予定です。