インテル®社の MAX® 10 FPGA の魅力を分かりやすく解説します。更に詳細な情報が必要な方は インテル社の ハンドブックをご参照ください。

|

インテル社の MAX 10 FPGA は、CPLD よりも 2世代以上 微細化したプロセスを採用することで、高速性と集積度を大幅に向上した不揮発性の FPGA です。 |

特長

ハードウェアで搭載している機能

![]() コンフィギュレーション・メモリ

コンフィギュレーション・メモリ

FPGA は電源を切るとコンフィギュレーション・イメージが無くなります。MAX 10 FPGA は電源を投入する度にフラッシュ・メモリに格納したコンフィギュレーション・イメージを自動で FPGA へ転送して動作します。

- コンフィギュレーション用のフラッシュ・メモリを内蔵しているので 外部に コンフィギュレーション・メモリ は不要です。

- 電源を投入すると 数ms以内 に動作を開始します(インスタント・オン)。

- 電源を落としても コンフィギュレーション・イメージ は失われません(不揮発)。

- フラッシュ用のプロセスを採用したので、フラッシュ・メモリへの再プログラミング(消去&書き込み)が最大で 1万回も可能です。

- コンフィギュレーション以外に ユーザが使用できる領域 ( UFM (ユーザ・フラッシュ・メモリ))が最大で 736Kbあります。

- コンフィギュレーション・イメージを2つ格納(デュアル・コンフィギュレーション)できて、それらをダイナミック(動作中)に切り替えができます。

< 特長を生かした利用例 >

- 出荷時のコンフィギュレーション・イメージを片方の領域に入れて、システム・アップグレード時の新しいイメージはもう一方の領域に入れます。もし、アップグレード後に問題が起こった際は出荷状態に切り替えることができます(フェイルセーフ・アップグレード機能)。

- 人がボタンを押す時間(数百ms)よりも大幅に短いコンフィギュレーション時間(数ms)を利用して、ボタンを押す毎に2つの機能を切り替えることができます。(フラッシュ・メモリの読み出しは回数制限がありません)。

![]() LE (ロジック・エレメント)

LE (ロジック・エレメント)

- MAX 10 FPGA は 最大で 5万個の LE を搭載しています。MAX V CPLD の最大 LE 数が 2,210個 なので 約23 倍も大きくなりました。

LE は論理回路を作るための FPGA の部品です。これを使えばプロセッサも作ることができるので、高性能なマイコンを作ることもできます。

- 最大 18 チャネル入力の 12 ビット、1Msps(百万サンプル数/秒) の ADC (アナログ-デジタル・コンバータ)と補正用の TSD(温度センシングダイオード) を搭載しています。

音声や各種センサーからのアナログ信号を ADC でデジタル信号に変換してからデジタル処理することができます。

![]() 内蔵メモリ

内蔵メモリ

- 最大で1.6Mbの SRAM を搭載しています。

- コンフィギュレーション・メモリの項にも記載していますが、 UFM も最大736Kb利用できます。

![]() DSP (Digital Signal Processor)・ブロック

DSP (Digital Signal Processor)・ブロック

- 18x18 の乗算器(マルチプライヤ)なら最大 144個、9x9 の乗算器なら 2倍の 288 個まで構成できる DSP を搭載しています。

乗算器は LE でも作ることができますが、 18x18の乗算器1個で数百個のLE を使用します。よって、乗算器を作るために最適化した部品 「DSP」 を使うと、 LE を使わずに、LE よりも高速な乗算器を作ることができます。

![]() オシレータ(発振器)

オシレータ(発振器)

- クロック信号を生成するオシレータを内蔵しています。

電源を入れるだけで動作するので、ウォッチドッグ・タイマーやスリープ・コントローラに利用できます。

![]() グローバル・クロック・ライン

グローバル・クロック・ライン

- 最大で 20本のグローバル・クロック・ラインを搭載しています。

グローバル・クロック・ラインは、直接 LE や DSP などの各セルにつながっている遅延とスキューが小さい配線です。

ファンアウトが大きい(LE等の多くのセルに接続されている)クロックやリセット信号に使います。

![]() PLL (Phase Locked Loop : 位相同期回路)

PLL (Phase Locked Loop : 位相同期回路)

- クロック信号を分周/逓倍、位相を合わせる PLL を最大 4個搭載しています。

PLL は1つのクロック信号から周波数が異なる 10 種類の安定した内部クロックと2種類の外部クロック信号を生成できます。

![]() AES (Advanced Encryption Standard)

AES (Advanced Encryption Standard)

- フラッシュ・メモリ と FPGA を1つのチップ上に搭載していますので、外部にフラッシュ・メモリを置くよりも構造的にセキュリティには強い製品ですが、更にコンフィギュレーション・データを暗号化するための 128 ビットの AES を搭載しています。

![]() I/O

I/O

- 3.3V、LVDS、mini-LVDS、PCI 、その他 30 以上の I/O を標準でサポートします。

- IP で提供されたコントローラを使って、SRAM、DDR2/3 や LPDDR2 などの外部に置いたメモリとインタフェースをとることができます。

![]() 電圧レギュレータ

電圧レギュレータ

- 2.5V と 1.2V の 2つの電源を供給する製品と 3.3V (または3V) の単一電源製品があります。

単一電源製品は内蔵したレギュレータで、FPGA コアに必要な 2.5V と1.2V 電源を生成しますので 外部に必要な電源デバイス数を削減できます。2電源製品は2つの電源が必要になりますが、パフォーマンスが高くなります。

その他の機能やパッケージ

![]() スリープ・モード

スリープ・モード

- 動作が不要な時はクロックや I/O を止めて、最大で 95% もの電力を削減するスリープ・モードをサポートします。

![]() ダイナミック入力バッファ・ディセーブル機能

ダイナミック入力バッファ・ディセーブル機能

- FPGA を再度コンフィギュレーション(リコンフィギュレーション)せずに、動作中に双方向バッファの入力バッファ部分を自動で止めることができます。

これにより、例えば DDR3 のアイドル状態や書き込み中で入力バッファが不要な時に、動的(動作中)にパワーダウンが行われます。また、LVDS の場合はユーザ側でON/OFFをコントロールすることができます。

- LE 数の増大と高速化により、32ビットのソフトコア・プロセッサ Nios II を搭載できるようになりました。

マイコンと違って、Nios II のペリフェラルは LE を使って自由に作ることができます。

![]() パッケージ

パッケージ

- スペース制約の厳しいシステ ムに有効な 3mm2の WLCSP (ウェハ・レベル・チップ・サイズ・パッケージ) から

最大ユーザ I/O 数が 500 本の FBGA パッケージまでご用意しています。

製品とパッケージ一覧

製品一覧

| 10M02 | 10M04 | 10M08 | 10M16 | 10M25 | 10M40 | 10M50 | |

| LE (ロジック・エレメント) 数 | 2,000 | 4,000 | 8,000 | 16,000 | 25,000 | 40,000 | 50,000 |

| 内蔵メモリ (SRAM)(Kb) | 108 | 189 | 378 | 549 | 675 | 1,260 | 1,638 |

| UFM (ユーザ・フラッシュ・メモリ)(Kb) | 12 | 16–156 | 32–172 | 32–296 | 32–400 | 64–736 | 64–736 |

| DSP (18x18 ビット乗算器)数 | 16 | 20 | 24 | 45 | 55 | 125 | 144 |

| PLL数 | 1or2 | 1or2 | 1or2 | 1or4 | 1or4 | 1or4 | 1or4 |

| 内部コンフィギュレーション | シングル | デュアル | デュアル | デュアル | デュアル | デュアル | デュアル |

| ADC/TSD 数 | - | 1/1 | 1/1 | 1/1 | 2/1 | 2/1 | 2/1 |

| EMIF | ○ | ○ | ○ | ◎ | ◎ | ◎ | ◎ |

注1:PLL/ADC/TSDなどの個数は、パッケージの種類によって異なります。

注2:EMIF の ○ ⇒ SRAM

注3:EMIF の ◎ ⇒ SRAM, DDR3 SDRAM, DDR2 SDRAM, LPDD

パッケージ一覧

|

|

|

| WLCSP | MBGA/UBGA/FBGA | EQFP |

| パッケージライン | 内容 |

10M02 |

10M04 | 10M08 | 10M16 | 10M25 | 10M40 | 10M50 |

| V36 | WLCSP (3 mm、 0.4 mm ピッチ) |

○ | - | - | - | - | - | - |

| V81 | WLCSP (4 mm、 0.4 mm ピッチ) |

- | - | ○ | - | - | - | - |

| F256 | FBGA (17 mm、 1.0 mm ピッチ) |

- | ○ | |||||

| U324 | UBGA (15 mm、 0.8 mm ピッチ) |

○ | - | - | - | |||

| F484 | FBGA (23 mm、 1.0 mm ピッチ) |

- | - | ○ | ||||

| F672 | FBGA (27 mm、 1.0 mm ピッチ) |

- | - | - | - | ○ | ||

| E144 | EQFP (22 mm、 0.5 mm ピッチ) |

○ | ○ | ○ | ||||

| M153 | MBGA (8 mm、 0.5 mm ピッチ) |

○ | - | - | - | - | ||

| U169 | UBGA (11 mm、 0.8 mm ピッチ) |

○ | - | - | - | |||

注意:同じ 〇 内はピン互換です。

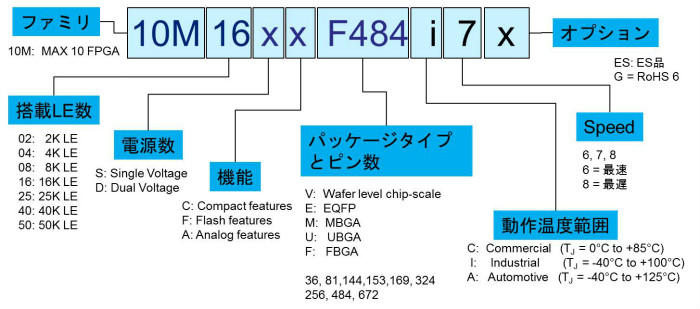

製品コードの見方

開発キット

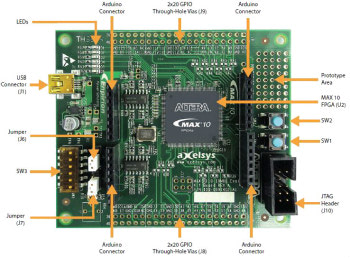

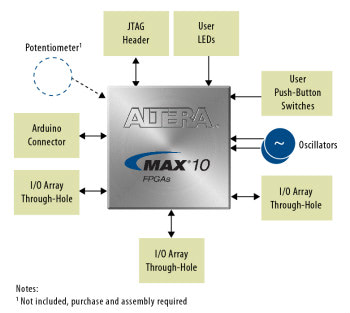

MAX 10 FPGA 10M08 評価キット

MAX 10 FPGA 10M08 を搭載し、80個の I/O スルーホールがあるコンパクトで安価な評価キットです。

拡大画像がある場合は画像のクリックで拡大します。

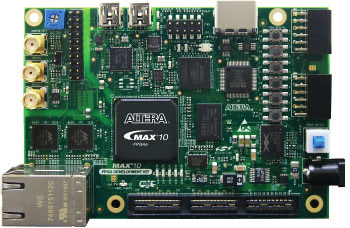

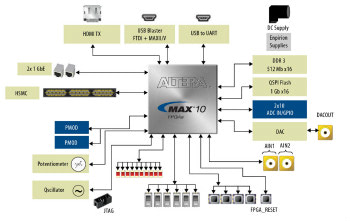

MAX 10 FPGA 10M50 評価キット

MAX 10 FPGA 10M50 、イーサネット、HSMC、SPI、DDR3 などを搭載した評価キットです。

拡大画像がある場合は画像のクリックで拡大します。

Q&A

![]() 無償の Quartus® IIウェブ・エディションでも設計できますか?

無償の Quartus® IIウェブ・エディションでも設計できますか?

- はい、無償のQuartus®II ウェブ・エディション を使って MAX 10 FPGA の全製品を設計することができます。

![]() 2,000 LE よりも小さい規模の製品を使いたいのですが?

2,000 LE よりも小さい規模の製品を使いたいのですが?

- 40~2,210 個の LE を搭載しているMAX V CPLDをご利用ください。 MAX 10 FPGA は MAX V CPLDを置き換える製品では無く、MAX V CPLDも引続き販売致します。

関連情報

上記の仕様は変更される場合がありますので、最新の仕様は下記のページをご参照ください。