こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

インテル FPGA の開発ソフトウェアである Quartus® Prime Pro Edition には、

FPGA コンフィグレーション用のファイル変換ツールとして以下の2つがあります。

いずれの変換機能も FPGA 用の .sof を入力ファイルとし、使用するコンフィグレーション・メモリーに応じた出力ファイル形式に変換します。

各ファイル変換ツールは、サポートしている FPGA ファミリーが異なります。

| FPGA |

ファイル変換機能 |

|

|

Programming File Generator |

Convert Programming Files |

|

|

Intel Agilex® 7 Stratix® 10 |

✔※ |

× |

|

Arria® 10 Cyclone® 10 GX |

× |

✔ |

| 備考 | Quartus Prime Pro Edition 18.0 からサポートされた機能 |

Pro および Standard Edition で従来使用されてきた機能 (操作についてはこちらのコンテンツをご覧ください。) |

※ Quartus® Prime Pro Edition の Programming File Generator は、Intel® MAX® 10 および Intel® Cyclone® 10 LP もサポートしています。

ここでは、Programming File Generator を使用して、コンフィグレーション・メモリー用ファイル .pof / .jic / .rpd を生成する方法をご案内します。

操作方法

- Programming File Generator を起動

- FPGA ファミリーおよびコンフィグレーション・モードを選択

- 生成するファイル・フォーマットを選択

- .sof をセット

- コンフィグレーション・メモリーを選択 (.pof/.jic 生成時のみ)

- Serial Flash Loader を転送する FPGA を選択 (.jic 生成時のみ)

以下より、具体的に画面操作を説明します。

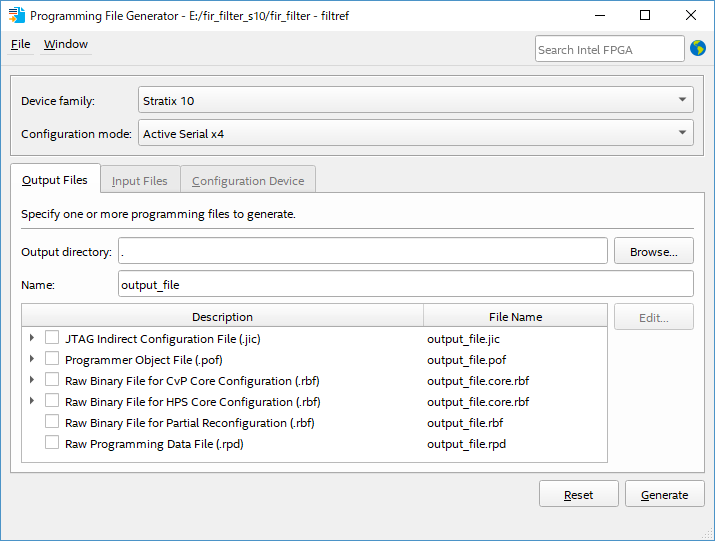

1. Programming File Generator を起動

File メニュー > Programming File Generator を選択し、GUI を起動します。

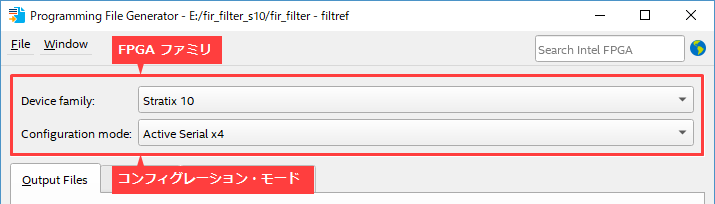

2. FPGA ファミリーおよびコンフィグレーション・モードを選択

該当する FPGA ファミリー、コンフィグレーション・モードを選択します。

|

項目 |

概要 |

選択肢 |

| Device family | コンフィグレーションの対象となる FPGA ファミリーを指定します。 |

Agilex, Stratix 10, Cyclone 10 LP, MAX® 10 |

| Configuration mode | コンフィグレーションの方式を指定します。 |

Active Serial x4, AVST x8, AVST x16, AVST x32 |

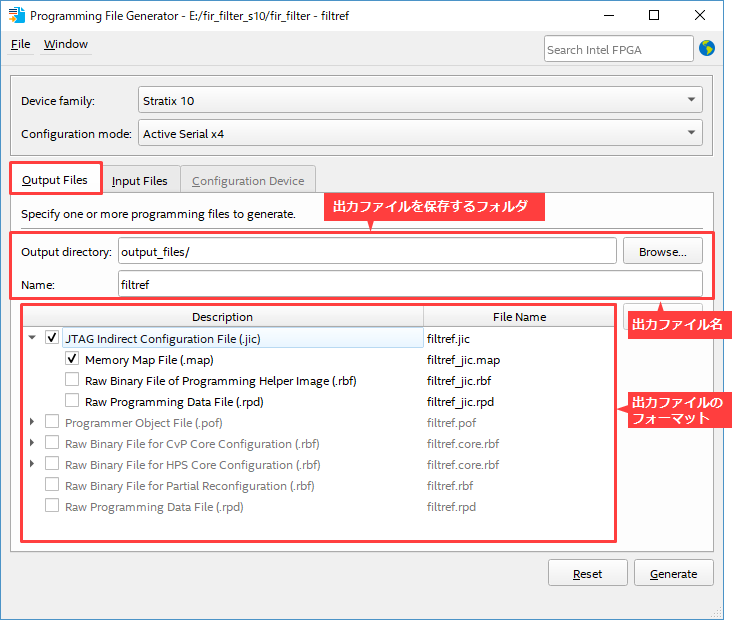

3. 生成するファイル・フォーマットを選択

Output Files タブ において、出力ファイルの保存フォルダー、ファイル名、ファイル・フォーマットを選択します。

|

項目 |

概要 |

選択肢 |

| Output directory | 出力ファイルを保存するフォルダーを指定します。 | 任意 |

| Name | 出力ファイル名を指定します。 | 任意 |

| 生成するファイルのフォーマットを選択します。 |

|

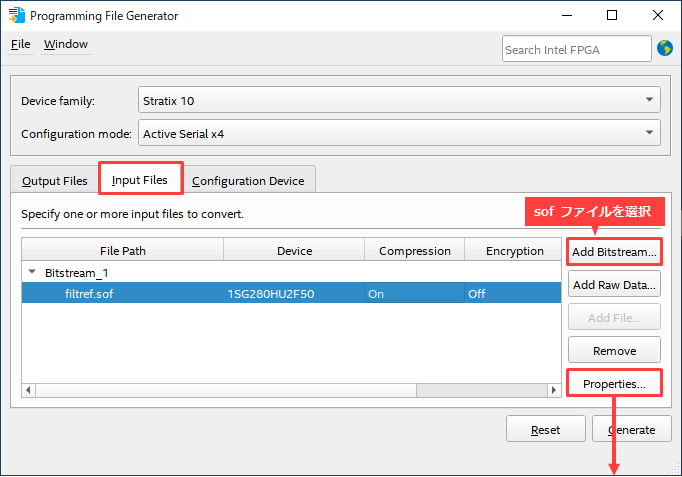

4. .sof をセット

Input Files タブ において [Add Bitstream] ボタンをクリックし、対象の FPGA 用 .sof を選択します。

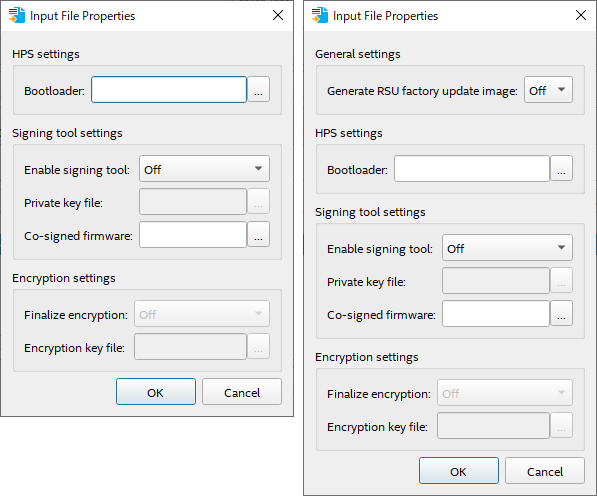

ファイル選択後に sof ファイル部分をハイライト選択すると

[Properties] ボタンがクリック可能になります。

セキュリティオプションや Bootloader の設定をおこなうことができます。

Compression 機能は自動で On に設定されます。

必要に応じて、オプションを追加してください。

rpd ファイルを生成する場合は、[Generate] ボタンをクリックし、作業を終了してください。

pof ファイル および jic ファイルを生成する場合は、次の操作5 へ進みます。

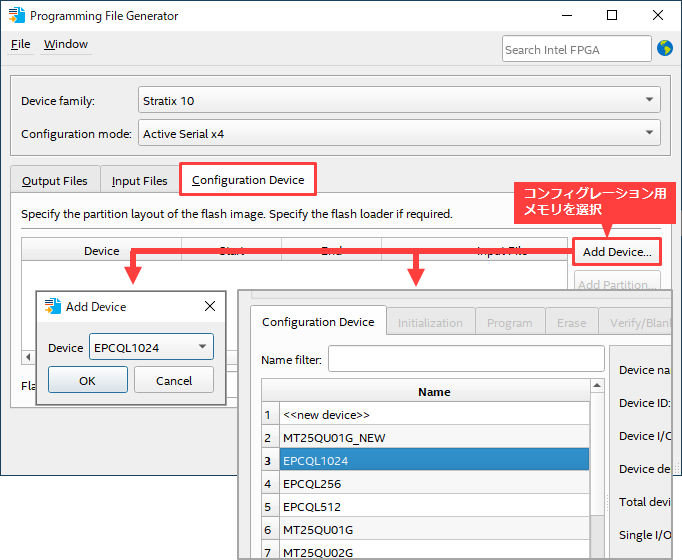

5. コンフィグレーション・メモリーを選択 (.pof/.jic 生成時のみ)

Configuration Device タブ において [Add Device] ボタンをクリックし、コンフィグレーション用メモリーを指定します。

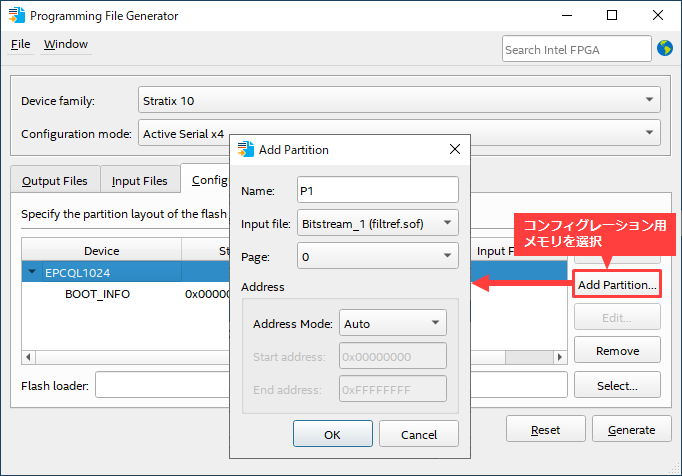

次に、選出したコンフィグレーション用メモリーをハイライト選択後に [Add Partition] ボタンをクリックし、操作4でセットした sof ファイルと格納するページ番号などを指定します。

|

項目 |

概要 |

| Name | 設定した内容に任意名をつけます。 |

| Input file | 操作4 でセットした sof ファイルを選択します。 |

| Page | sof ファイルを格納するページを指定します。 |

| Address | 必要に応じてアドレスを指定します。 |

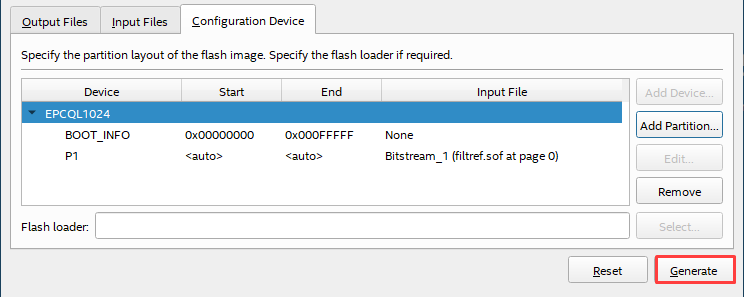

pof ファイル生成する場合は、[Generate] ボタンをクリックし、作業を終了してください。

jic ファイルを生成する場合は、次の操作6 へ進みます。

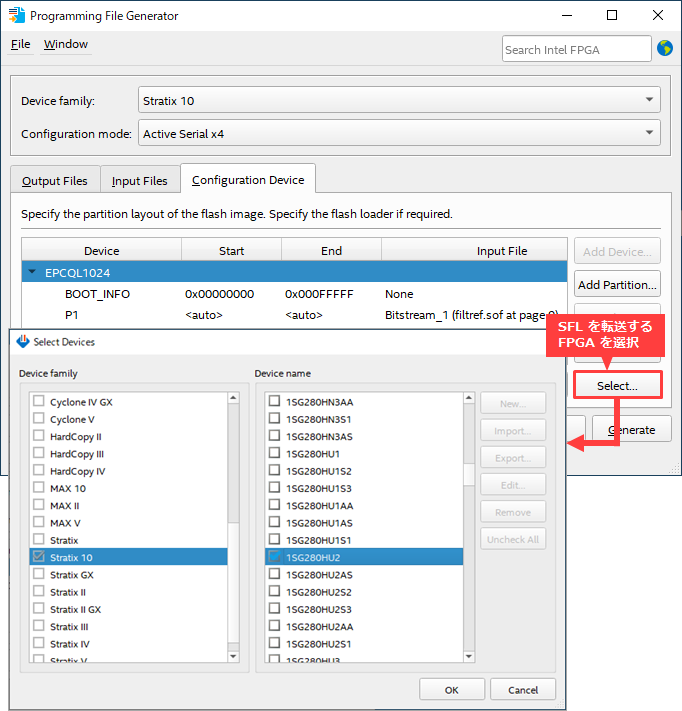

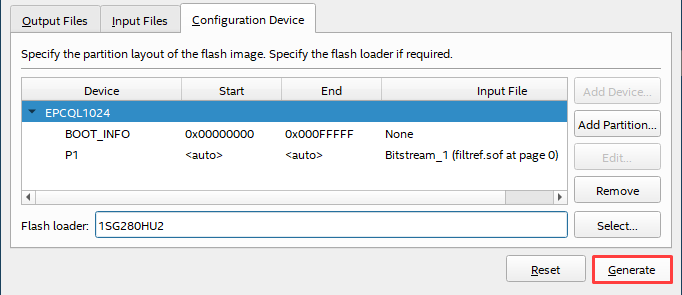

6. Serial Flash Loader を転送する FPGA を選択 (.jic 生成時のみ)

[Select] ボタンをクリックし、Serial Flash Loader (以下 SFL) を転送する FPGA を選択します。

[Generate] ボタンをクリックし、作業を終了してください。

おすすめ記事/資料はこちら

Quartus® ガイド - プログラミング・ファイルの生成と変換(Convert Programming Files)