こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

今回は、インテル Quartus® Prime Pro Edition 開発ソフトウェアで効率良くピンレイアウトが設計できる “インターフェイス・プランナー” をご紹介します。

対象の環境

|

対象の Quartus Prime |

Quartus Prime Pro Edition |

| 対象の FPGA | ご利用の Quartus Prime Pro Edition のバージョンで対応している FPGA ファミリ |

I/O プランニングにおける課題

近年の FPGA において I/O アサイメントを作成する際の主な課題には、以下が挙げられます。

・複雑性の高まる I/O 規格と FPGA の I/O 構造

⇒ デザインの正確なピン配置に必要なガイドラインの手順が増加

・FPGA デザイン設計と同時(あるいは少し前)に行われる PCB 開発

・デザインサイクルの初期段階でのピン・アサイメントの検証

これらの課題に対処するため、Quartus Prime には以下の既存ソリューションがあります。

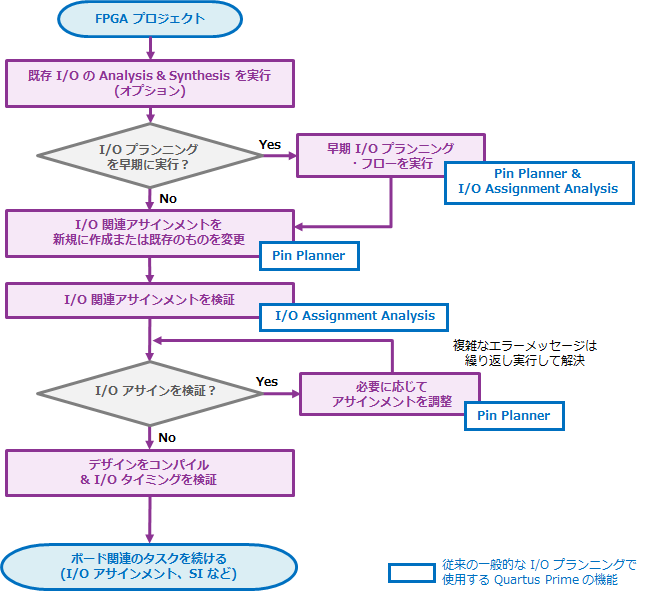

今までは、I/O フロアプランを作成するために、

下図の作業フローにおいて Pin Planner や I/O Assignment Analysisをそれぞれ使用していたと思います。

このフローでは、I/O Assignment Analysis によりピン・アサイメントを解析します。

I/O Assignment Analysis の精度はデザインの完成度に左右されます。

何らかのエラーが検出された場合、Pin Planner やその他のツールで不具合を修正し、再び I/O Assignment Analysis を実行する必要があり、

このサイクルは、すべての I/O アサイメントが完了し、検証されるまで続きます。

インテルの FPGA は現在、市場で要求されている様々なプロトコルをサポートしています。

また、それぞれに固有の配置規則がある多数のメモリ・インターフェイスもサポートしています。

デザインに含まれるインターフェイスが多いほど、複雑なルールや制限が出てきてしまいます。

デザイン・インターフェイスを正確に配置したと思っても、本当に正確であるのかはフル・コンパイル中にFitter を実行するか I/O Assignment Analysis を実行するまで分かりません。

もし、ある要素の配置が無効な位置にあり、それによって不適合となる場合、フル・コンパイルに費やした長い時間は無駄になってしまいます。

インターフェイス・プランナー

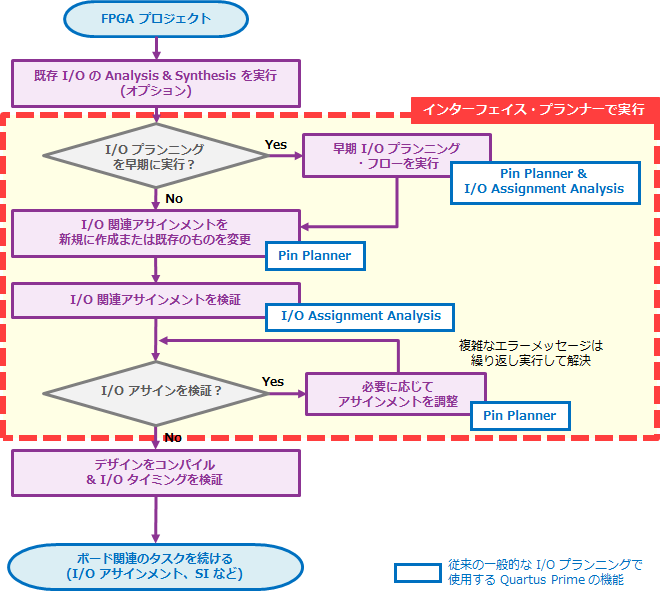

Quartus Prime Pro Edition のインターフェイス・プランナーは、ピンの配置規則に従い、複雑な I/O インターフェイスのアサイメントをグラフィカルに作成でき、リアルタイムに検証することができるピンレイアウト・ツールです。

下図は、インターフェイス・プランナーを採用した場合の I/O フロアプランの作業フローです。

インターフェイス・プランナーは、リアルタイムでピン・アサイメントを検証するため、Fitter を使用します。そのため、事前に論理合成 (Synthesis) を実施しますが、デザインは完全である必要はありません。

インターフェイスのデザインをデバイスのリソースに割り当てるには、フロアプラン上へドラッグ & ドロップ あるいは ダブルクリックするだけです。

作成したアサイメントのプランは、TCL スクリプトとして生成・実行し、プロジェクト反映後にコンパイルを実施します。

作業概要

インターフェイス・プランナーの作業フローは、以下のとおりです。なお、ユーザーによるピン・アサイメントは完了しているものとします。

- デザインを合成

- インターフェイス・プランナーを起動・初期化

- インポート済みのアサインメントをチェックしプランを更新

- デザイン・エレメントを配置

- I/O プランを検証

- プランファイルの書き出し

- プロジェクトにインポートしコンパイル

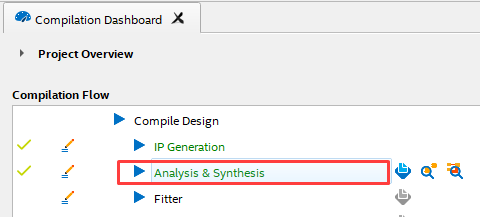

1. デザインを合成

Quartus Prime Pro Edition (以下、Quartus Prime) において、Processing メニュー あるいは Compilation Dashboard により、Analysis & Synthesis を実行します。

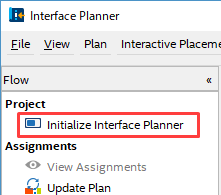

2. インターフェイス・プランナーを起動・初期化

Tools メニュー > Interface Planner を起動します。

Flow ペイン内の Initialize Interface Planner をクリックし、Fitter ベースの有効性および既存のロケーション・アサイメントをチェックします。

競合や違反があった場合は、Console ペインにエラーメッセージが表示されます。

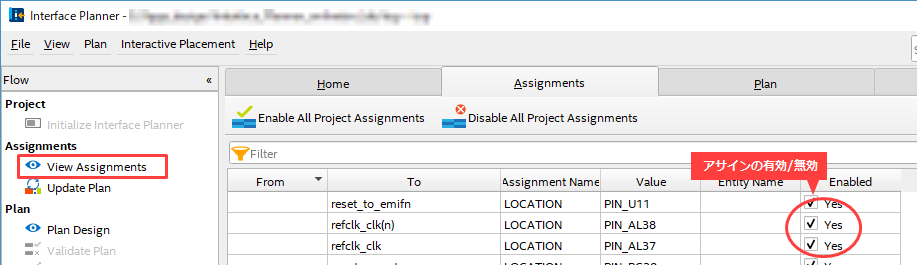

3. インポート済みのアサインメントをチェックしプランを更新

Flow ペイン内の View Assignments をクリックします。(Assignments タブがアクティブになります。)

Assignments タブがアクティブになり、プロジェクトに存在するすべてのアサインメントがリストアップされます。

Flow ペイン内の Update Plan をクリックします。

Enabled 設定されたアサイメントが、ルールチェックのためデザインに適用されます。

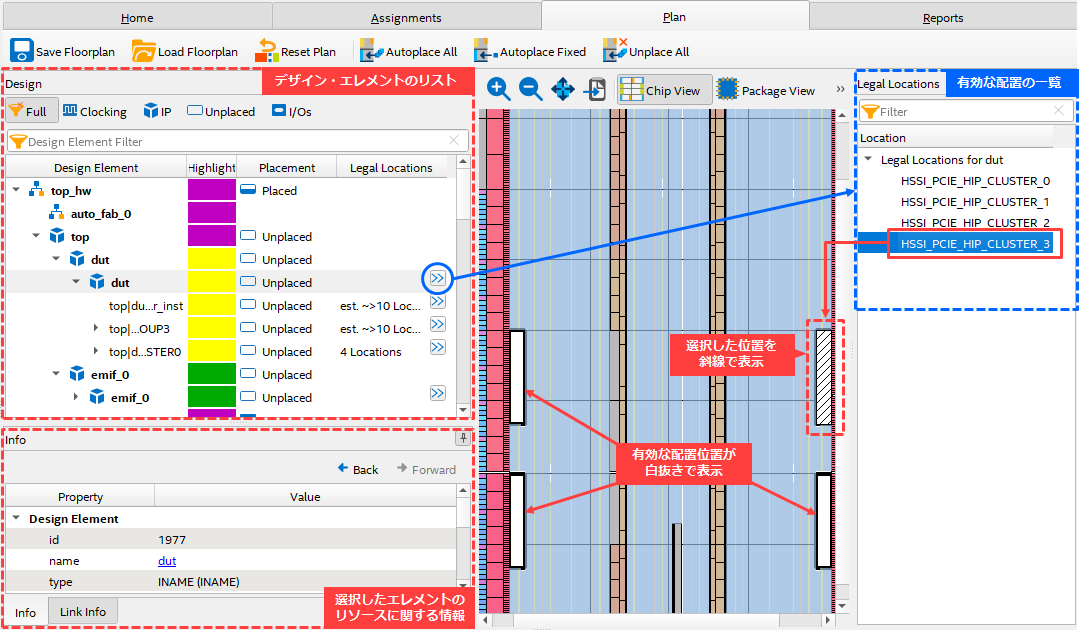

4. デザイン・エレメントを配置

Flow ペインの Plan Design をクリックします。(Plan タブがアクティブになります。)

Design ペインにおいて、アサインされていないデザイン・エレメント右横のボタンをクリックすると、Legal Locations ペインにアサイン可能な配置の一覧が表示され、Chip View に白抜きで位置が表示されます。

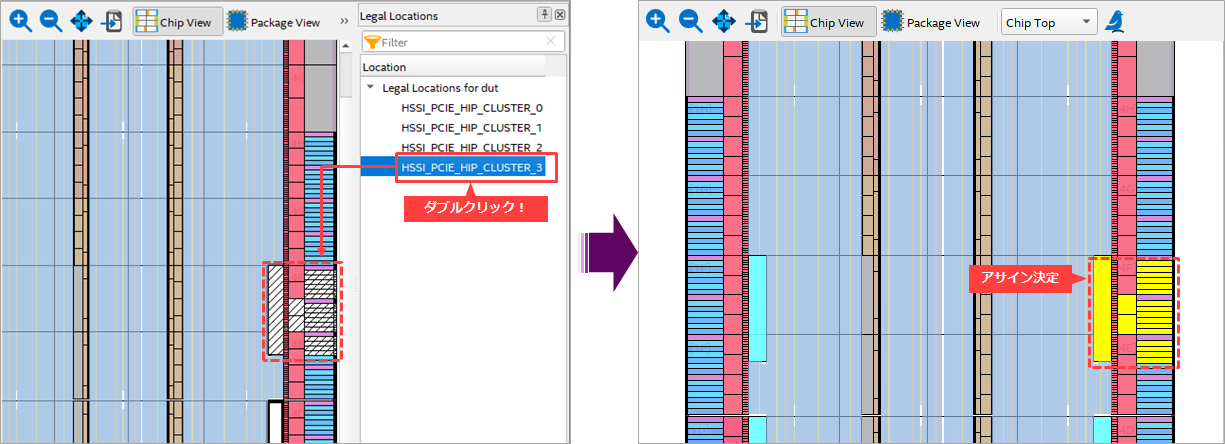

Legal Locations ペインから配置位置を指定すると、Chip View の表示が斜線になります。

アサイン位置を確定する場合は、Legal Locations ペインの位置情報をダブルクリックします。

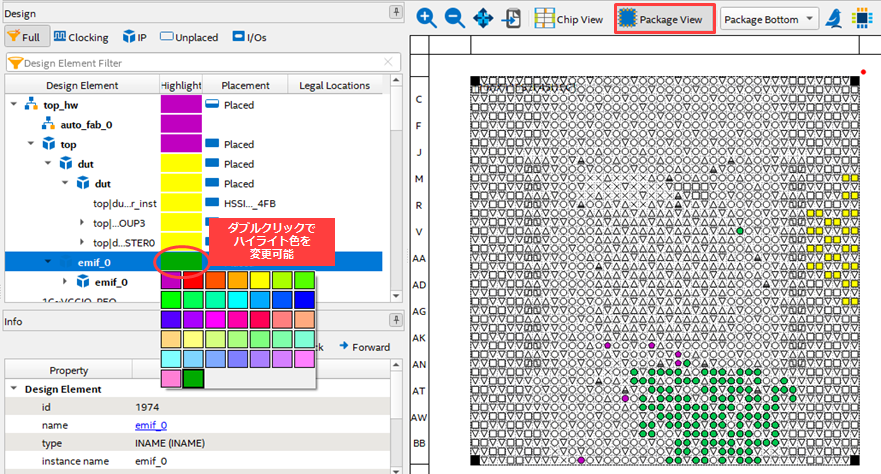

Package View に切り替えて、インターフェイスで使用される I / O ピンを確認することもできます。 また、後でコンパイルした設計と比較できるように、計画のスクリーンショットを撮ることもできます。

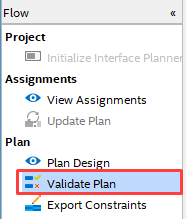

5. I/O プランを検証

配置指定が完了後、 Flow ペイン内の Validate Plan をクリックします。

これにより、作成した割り当てが検証され、エクスポートする準備が整います。

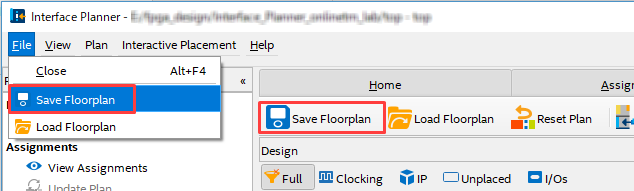

Save Floorplan を選択し、現時点の配置設定を保存することも可能です。

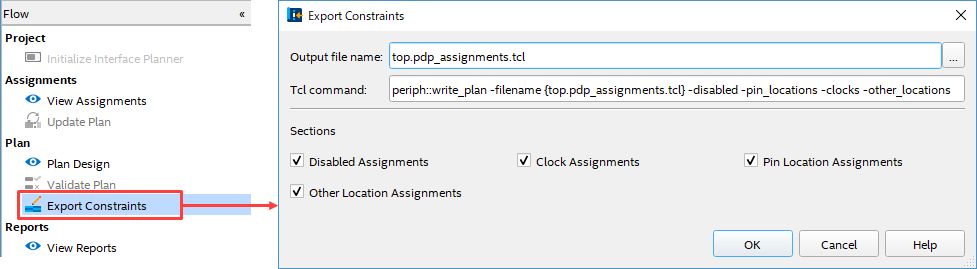

6. プランファイルの書き出し

Flow ペイン内の Export Constraints をクリックし、設定した配置情報を tcl スクリプトで保存します。

7. プロジェクトにインポートしコンパイル

インターフェイス・プランナーを閉じ、インポート先の Quartus Prime プロジェクトを開きます。

Tools メニュー > Tcl Script から、エクスポートした tcl ファイルを指定し、Run をクリックして反映させます。

アサイン情報は、Pin Planner や Assignment Editor に反映されるので、スクリプトの情報を見やすく最終確認することができます。

Run 実行前に、Edit ボタンによりスクリプトを編集することも可能です。

例えば、インターフェイス・プランナーがエクスポートしたすべてのタイプのアサインメントをデザインに反映せず。ピン配置のアサインメントのみを作成し、内部リソースのアサインメントを作成しない場合は、コメントアウトや削除することで、スクリプトのピン配置アサインメントのセクションだけを提供することが可能です。

その後、コンパイルを実行します。

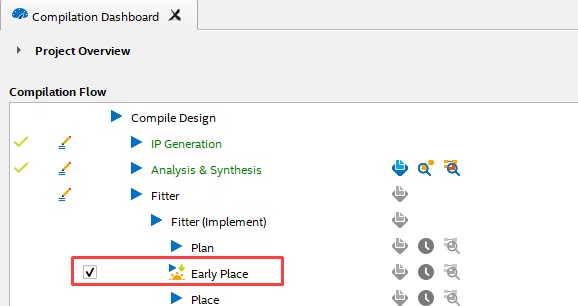

Analysis & Synthesis から Fitter (Finalize) ステージまでの実行に時間がかかるため、もしも配置を評価するだけであれば、Compile Dashboard の Early Place オプションを有効にし、Early Place コンパイルを実行することも可能です。

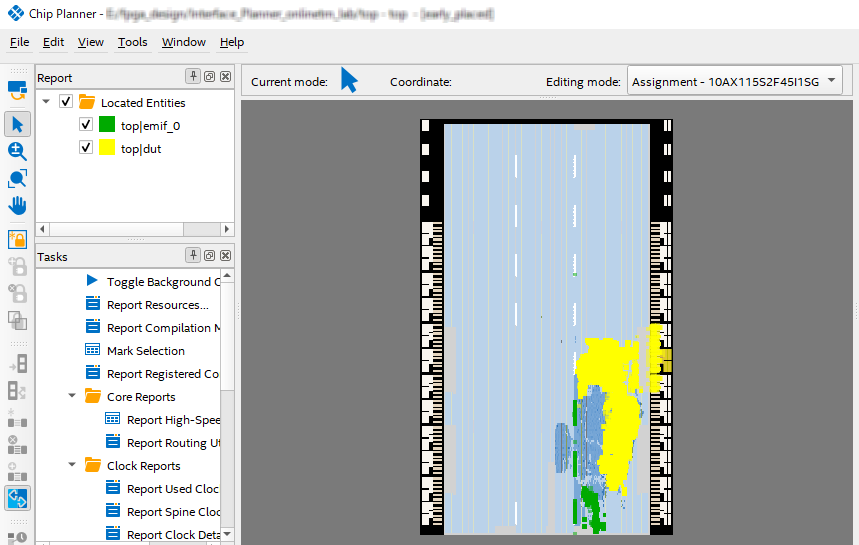

コンパイル終了後、Chip Planner (Tools メニュー) を起動し、配置を確認します。

まとめ

Quartus Prime Pro Edition のインターフェイス・プランナーは、I/O インターフェイスが多様化かつ複雑化する FPGA に対して、プロアプラン作成の手間や困難さを省き、有効なロケーション・アサインメントのみを作成することが可能です。

インターフェイス・プランナーを使用することによって、ロケーション・アサイメントに費やす時間を削減することができます。