こんにちは、マス男です。

前回コラム「マス男の FPGA 基板製作1」では、クロック信号のオーバーシュートが絶対最大定格の電圧値を超えていることが発覚しました。

先輩社員に相談したところ、ダンピング抵抗を取り付けたらオーバーシュートを抑制することが出来るとアドバイスをもらいました。

オーバーシュートとは

オーバーシュートとは、矩形波の立ち上がり部分で上方向に突出した波形の乱れです。

(下方向に突出した波形の乱れはアンダーシュートという。)

オーバーシュートは、信号の反射やノイズ信号の重なりが原因で起きます ( 図1 )。

図1. オーバーシュートの原因

ダンピング抵抗でオーバーシュート除去

オーバーシュートが非常に大きくなると、信号を受ける側のデバイスを破壊したり、ラッチアップ現象を起こしたり、デバイスの信頼性低下をまねくことがあるのできちんとケアする必要があります。

信号線上に抵抗( ダンピング抵抗という )を直列接続することでオーバーシュートを抑制することができます。

ダンピング抵抗は出力ピンの近端に置くのが適切であると先輩に教わりました ( 図2 )。

図2. ダンピング抵抗の位置

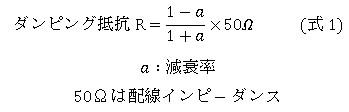

ダンピング抵抗値は以下の式で求めることができます。

オーバーシュート電圧 4.3 V を 3.3 V に減衰する(減衰率 a = 20 % )ダンピング抵抗値は ( 式1 ) より R = 33 Ω と求まりました。

実際は、30 Ω の抵抗を取り付けました。

ダンピング抵抗値を取り付ける前後のクロック信号波形の様子です ( 図3a, 3b )。

図3a. ダンピング抵抗無しのクロック波形 図3b. ダンピング抵抗有りのクロック波形

ダンピング抵抗 30 Ω を発振器の近くに置いたことで、クロック信号のオーバーシュート電圧を 3.9 V に抑えることが出来ました。

学んだこと

・オーバーシュートは、信号を受ける側のデバイスを破壊したり、ラッチアップ現象を起こしたり、デバイスの信頼性低下をまねくことがある

・信号線の近端にダンピング抵抗を直列接続することでオーバーシュートを抑制することができる