こんにちは、マス男です。

「マス男の FPGA 基板製作」と題して、新人研修の一環で時計機能を実装するため

FPGA ボードの設計を行ったときの赤面エピソードを連載していきます!

新人が "やらかした失敗" を温かく見守ってください (笑)。

絶対最大定格の電圧をオーバーした代償…

新人同期であるトットの FPGA がある日突然、動かなくなりました。

呆然と動かなくなった FPGA を見つめる同期3人…

原因は、絶対最大定格の電圧値 (4.2 V) をオーバーした電圧値 (5.5 V) を FPGA に印加したからでした。

トット 「さっきまで正常に動いていたのは何故ですか!?」

先輩社員 「例えば、最高速度120 km/h の車が200 km/h で走行し続けたらエンジン壊れるよね。

FPGA も同じで、絶対最大定格の電圧を超えて動作し続けたら壊れるよ。」

絶対最大定格 (Absolute Maximum Ratings) について

FPGA に対して、電源電圧・入力信号電圧の最大値などが規定されています (Table1-1)。

絶対最大定格は、デバイスが破壊に耐えうる限界の規定値です。

そのため、絶対最大定格を超えるとデバイスに致命的な損傷を与える可能性があります。

この値はデバイス・ファミリごとに異なります。

なお、マス男が使用しているデバイスは Cyclone® IV E です。

発振器の出力信号電圧は 5.5 V 仕様であり、 5.5 V のクロック信号を FPGA に入力していたのです。

実は、マス男もトットと同じ発振器を使用しており、マス男の FPGA も破損する危険にさらされていたのです!!

推奨動作条件 (Recommended Operating Conditions) について

FPGA に対して、電源電圧・入力信号電圧の推奨値などが規定されています (Table 1-3)。

電源設計をする時、マス男は Table 1-3 を確認しました。

FPGA への供給電源電圧が推奨値 (Typ) になるように設計しました。

しかし、FPGA への入力信号電圧の確認を怠り、5.5 V 仕様の発振器を購入してしまいました…

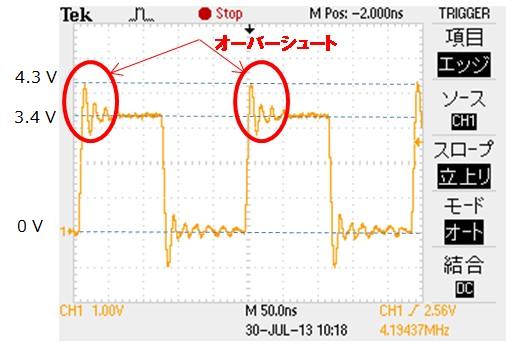

オーバーシュート

FPGA 破損後、出力信号電圧が 3.3 V 仕様の発振器に変更しました。

今度は、入力信号電圧の推奨値 (3.6 V) をちゃんと満たしているのか、オシロスコープでクロック信号を観測しました。

下の画像は、FPGA 入力端子にプローブを当てて観測したクロック信号です(図1)。

観測した結果、オーバーシュートが発生していました。

オーバーシュート部分(ノイズや信号反射の重なり)が絶対最大定格の 3.6 V を超えていました。

マス男は発振器を変更する以外の対策を思いつくことができませんでした。

この事実を先輩社員に相談しました。

マス男 「オーバーシュートが絶対最大定格を超えていました。どうしたらいいですか?」

先輩社員 「ダンピング抵抗を取り付けたらいいじゃない。」

(続く…)

学んだこと

・ 絶対最大定格を超えると FPGA に重大なダメージを与えるので、絶対に超えてはいけない

・ 推奨動作条件の電圧値を満たすように FPGA 基板設計をすること

実はもうすでに手遅れで、マス男の FPGA デバイスには重大なダメージが生じていたことをこの後、思い知るのであった。