こんにちは、マス男です。

今週から “タイミング解析” について連載していきます。

新人研修で最も難しかったのが、タイミング解析の講義でした。

本コラムでは、タイミング解析の講義資料やノートをまとめ、つまずいた点をご紹介したいと思います。

本日は SDC ファイルについてです。

タイミング解析とは

タイミング解析とは、ある動作周波数において、 FPGA が正確に動作するかを検証することです。

詳しくは 『 タイミング解析の概念 』 をご覧ください。

タイミング解析をするには SDC ファイルが必要

タイミング解析の研修で、難しいと思ったのが、 SDC ( Synopsys Design Constraints )記述でした。

シノプシス・デザイン制約ファイルってなんだろう?

SDC ファイルとは ASIC 業界におけるタイミング制約の標準フォーマットで、 FPGA 業界でも取り入れられた背景があります。

タイミング解析するには SDC ファイルが必要となります。まずは SDC ファイルの新規作成方法をご紹介します。

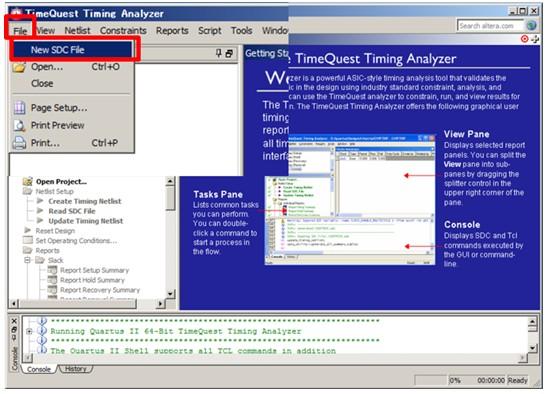

1. デザインをコンパイル後、TimeQuest Timing Analyzer を起動

Quartus® II 画面

2. Netlist の生成

Netlist > Create Timing Netlist … をクリック。

TimeQuest Timing Analyzer 画面

Create Timing Netlist にて OK をクリックし、 Netlist 生成完了。

Create Timing Netlist 画面

3. SDC ファイルの作成

File > New SDC File をクリック。

テキストベースで SDC 制約を記述します。

SDC ファイルの画面

SDC ファイルには何を記述するの?

下記 URL は SDC 記述の例です。

簡単にまとめると、

・動作周波数を記述

・入出力 I/O は基板の遅延情報など FPGA 外部のタイミングを記述

この2つの情報を SDC 記述することで、 FPGA が問題なく動作するか解析が可能です。

Quartus® II は FPGA 内部の 「配線による遅延時間」 「レジスタ出力遅延時間」 の情報を持っています。

しかし、FPGA 外部の 「動作周波数」 「入出力 I/O の遅延情報」 はユーザが Quartus II に与える必要があり、それが SDC ファイルなのですね!

SDC は TimeQuest Timing Analyzer で簡単に記述

SDC 記述言語を覚える必要はありません。(←安心!)

TimeQuest Timing Analyzer の GUI で簡単に記述できるのでご紹介します。

4. SDC コマンドの GUI を起動

先ほど新規作成した SDC ファイルより、 Edit > Insert Constraint をクリック。

SDC ファイルの画面

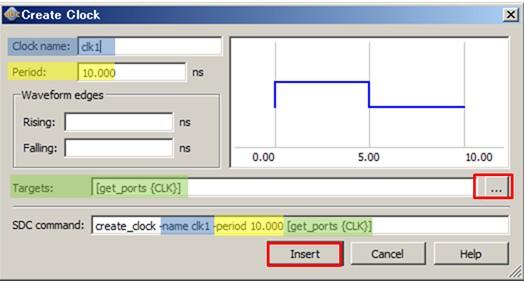

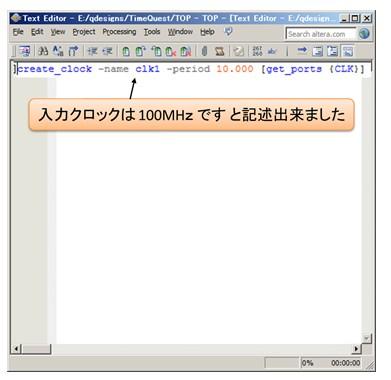

5.動作周波数の SDC コマンド記述

ここでは、クロック制約記述を例にご紹介します。 Create Clock … を選択。

・ Clock name : 任意の名称を記入

・ Period : 動作周波数を記入

・ Targets : HDL で定義したクロック信号名を選択

まとめ

・タイミング解析をするには SDC が必要。

・SDC とは、デバイス外部の遅延情報を記述したテキストファイル。

・SDC コマンドは TimeQuest Timing Analyzer の GUI で簡単に記述できる。