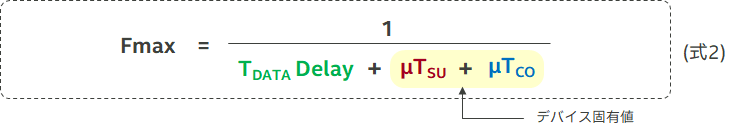

Fmax ( 最大動作周波数 )

タイミング解析では、あるクロック周波数において、FPGA が正確に動作するかを検証します。

タイミング解析の指標となるのが Fmax 値 です。Fmax とは、FPGA が動作する最大周波数であり、式1 で定義されています。データが 1 クロック・サイクルの間に送信レジスターから受信レジスターに到達可能かを計算しているんですね!

・TDATA Delay : データ遅延時間。 回路デザインに依存する。

・TCLK2 - TCLK1: クロックスキュー。 配線に依存する。

・μTSU : セットアップ・タイム。 レジスターの入力クロックエッジに対してデータがあらかじめ確定・保持している必要がある時間。 デバイス固有値。

・μTCO :クロック to アウトプット。 レジスターの入力クロックエッジに対してデータ出力されるまでの時間。 デバイス固有値。

式1 より、Fmax は "回路デザイン" と "クロックスキュー" に依存していることがわかります。

ここで、アルテラ FPGA デバイスには、クロックスキューが最小になるように調整された専用配線領域 (Global Clock , Regional Clock など) が内蔵されています。クロック信号を Global Clock に配線したとき クロックスキュー = 0 (つまり Tclk2 = Tclk1 ) となるので、式1 に値をあてはめると 式2 になります。

式2 より、Fmax は "回路デザイン" に依存することになります。

ユーザーは Fmax が期待値になるよう、設計することが求められます。

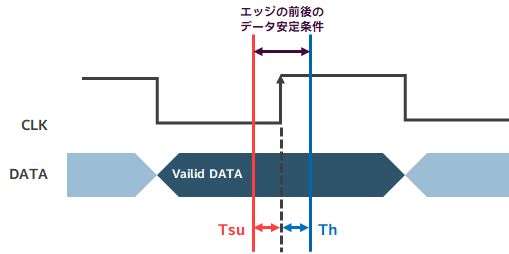

セットアップ・タイム と ホールド・タイム

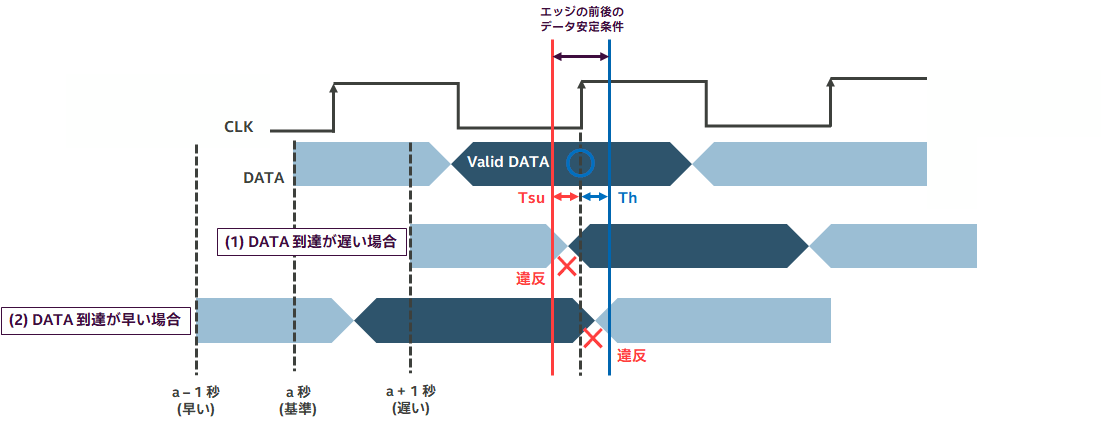

正しくデータを取得するためには、クロックエッジの前後でデータが安定している必要があります (図2)。

セットアップ・タイム (Tsu) :クロックエッジ前にデータ (DATA) を確定しなければならない時間。

ホールド・タイム (Th) : クロックエッジ後にデータ (DATA) を保持しなければならない時間。

タイミング解析では、セットアップ・タイムとホールド・タイムを満たしているか 全レジスター間のパスを解析しています。

データとクロックエッジのタイミングが合わないとき、セットアップ・タイム / ホールド・タイム違反となります。

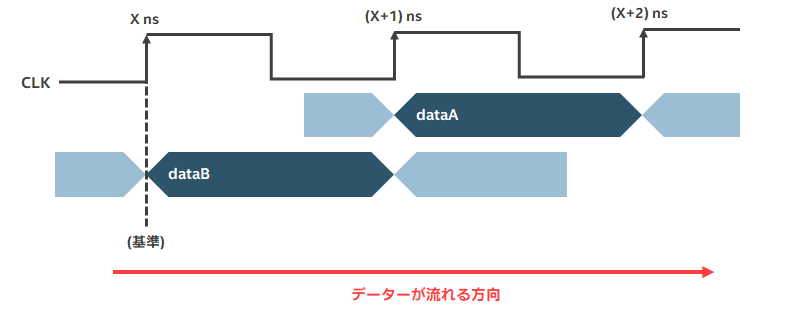

突然ですが、ここでクイズです!!

図3 の左端のクロックエッジを基準としたとき、 dataA と dataB はどちらが時間的に早い/遅いでしょうか??

答えは、dataA => 遅い dataB => 早い です。

マス男は「データが流れる方向に dataB よりも dataA の位置が前だから、時間的にも dataA の方が早く進んでいる」と錯覚しました (←つまずいた点)。

しかし 論理回路の動きを表現する場合、時間軸は左から右に表されます。つまり、クロックエッジに対して

左側が時間軸としては早く

右側が時間軸としては遅く

なっています。

クロックエッジに対してデータの有効範囲を見ることがタイミング解析を理解する上でとても重要なポイントだと気づきました!!

結論としては、データ到達がクロックエッジに対して遅いときセットアップ・タイム違反で、データ到達が早いときホールド・タイム違反となります。 (図4)

| まとめ |

|---|

|

・ Fmax のパラメーターは “回路デザイン” に大きく影響を受ける( 式2 )。 |

次回は タイミング解析では必ず必要な SDC ファイルついてご紹介します!