こんにちは、太郎です。今回は SER について書きます。

SER とは?

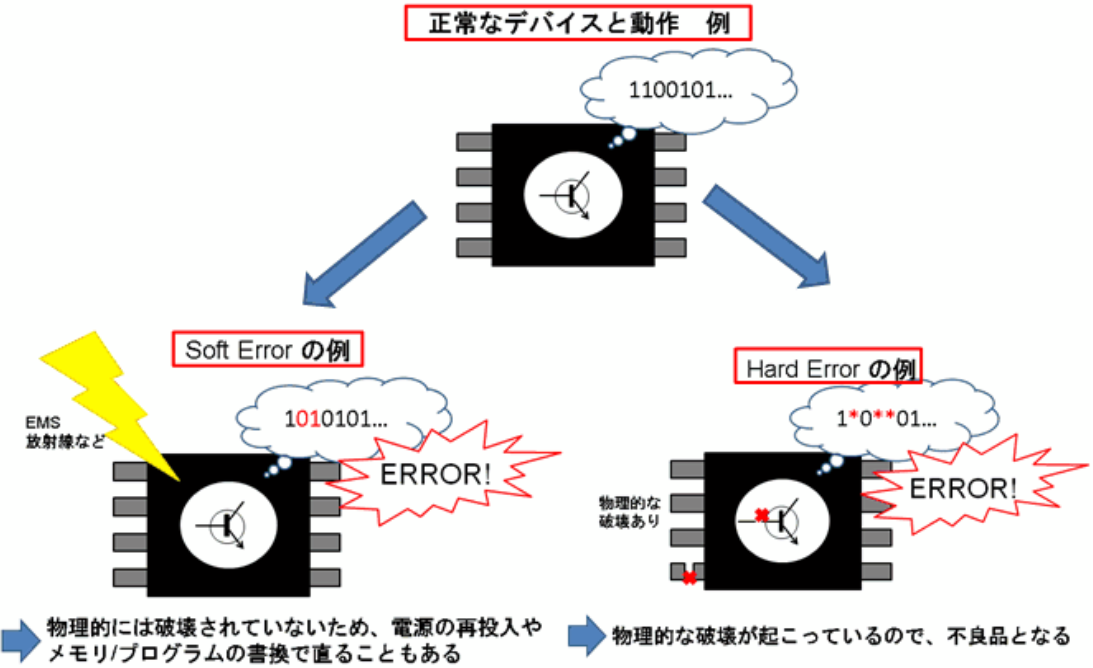

SER は Soft Error Rate の略で、放射線による LSI の動作不良の割合を言います。

SER は 物理的なトランジスタの破壊等による Hard Error の対義語として扱われることもあります。

Soft Error が起こった半導体チップは物理的に破壊されているわけではないことがポイントです。

つまり、物理的に破壊されているわけではないので、データの書き換えや電源を再投入することで正常動作に戻ります。

例えば SRAM では、メモリーセルに電荷を蓄えてデータを保持していますが、電荷を放電するイオン化放射線との衝突により、値が乱され、メモリーエラーになります。

SER の評価方法

デバイスの EMI (『PLL の応用 (スペクトラム拡散で EMI を減らそう!)』 参照) の影響度合を調査する方法として、中性子ビームの照射、放射性同位元素の近傍配置などがありますが、いずれも加速試験となります。

加速試験とは、実際の使用時間ではなく、測定時間を実使用時間よりもはるかに短縮した試験を言います。

私は加速試験を規定以上のクロック周波数でシステムを稼働させる試験と勘違いしていました。

規定以上のクロック周波数でデバイスを稼働させることはオーバークロックと呼ばれています。

技術サポートをする立場としては、このような使い方はお勧めできません。

規定以上、つまり推奨動作範囲外でご使用され問題が発生してもサポート対象範囲外になってしまうためです。

デバイスは必ず推奨動作範囲内でご使用ください。

半導体チップ、山に行く

上記の加速試験は、実際の使用環境を厳密に再現したものではなく、厳しい試験となる傾向があるようです。

ソフトエラーの影響を見積もる際、高山地帯に半導体チップを置いて試験を行うことがあるそうです。

欧州では、フランス・アルプスの一角に 「ASTEP (Altitude SEE Test European Platform)」 という、宇宙線由来の放射線を測定する施設があります。

ASTEP の高度は 2,552 m にあり、海面高度に比べると、約 6 倍の中性子線照射量があるそうです。

半導体デバイスは室内で実験するイメージが強かったので、とても意外に感じました。

アルテラ社の SER 対策について

アルテラ社 FPGA 内にはエラー検出回路(CRC: Cyclic Redundancy Check 回路)が内蔵されています。

(CRC のサポートについての詳細は、各デバイスファミリーのハンドブックをあわせてご参照ください)

アルテラ社 配置配線ツール Quartus® II のオプションを使用する事で容易に FPGA 内部の CRC 回路を有効にできます。

詳しくはこちらをご参照下さい。

さらに、最新の SoC FPGA においても Soft Error 対策を強化しています。

SoC FPGA についてはこちらをご参照下さい。

ものづくりでは本当に様々なことを考慮する必要があるのですね。

以上、太郎でした。