こんにちは。梅おにぎりです。

前回は、コンフィギュレーション・データのサイズを圧縮することで、AS モードでのコンフィギュレーション時間を短くすることに成功しました。

しかし欲張りな梅おにぎりは、"もっとコンフィギュレーション時間を短くできないか" と考えていました。

いろいろと探していると、何とも速そうな名前のコンフィギュレーション・モードを見つけました。

Fast Passive Parallel (FPP) モード!

今回は、FPP モードでコンフィギュレーション時間をどれくらい短縮できるかを見てみましょう。

FPP モード

FPP モードは、以下のような構成となっています。

※ 図内の注釈は、Cyclone IV のドキュメントをご覧ください。

前回の AS モードと異なる点は、2点あります。

1点目は、コンフィギュレーション・データの幅が 8bit であること。

AS モードの 1bit に比べて、1/8 のクロック数でコンフィギュレーションが完了します。

2点目は、Cyclone® IV E がコンフィギュレーション用のクロックを受信していること。

AS モードでは FPGA 内部のオシレータを使用していましたが、外部からクロックを入れることで、より速いクロックでデータ転送をすることができます。

ここで疑問が湧きました。

「データ転送クロックの速度に上限はないのだろうか?」

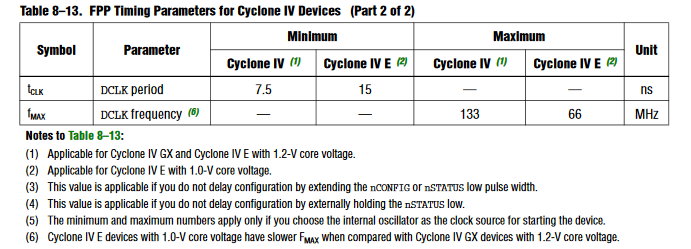

データシートで確認してみると、上限は 133MHz までいけるようです(Cyclone IV E のコア電圧が1.0V の場合は66MHz)。

AS モードのデータ転送クロックが 20~40MHz であるのと比べると、かなり速くできそうです。

では実際に計算してみましょう。

DCLK が 133MHz (7.5ns) として計算したのが次の式です。

データ・サイズ DCLK 周期 データ幅

(2,944,088 bits X 7.5 ns ) ÷ 8bit = 2.7 ms

AS モードでは、圧縮後でも 33.1~95.6ms であったのに対して

FPP モードでは、 2.7ms と大幅に短縮されました。

まとめ

FPP モードを使用することで、コンフィギュレーション時間を大幅に短縮することができました。

もう これ以上のコンフィギュレーション時間の短縮は無理かな、と考えていた梅おにぎり。

しかし、デバイスに電源を入れてからユーザモードになるまでの時間を考慮すると

まだまだ短縮する術があるのだった。 (次回に続く)