こんにちは、マス男です。

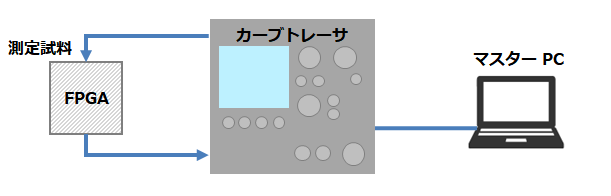

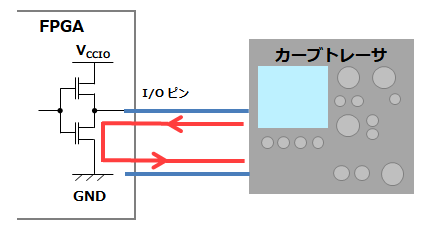

I/O ピンが 0V を示したとき、GND による 0V なのか、オープンによる 0V なのかをどうやって判断するのか先輩に聞いたところ、半導体の電流電圧特性はカーブトレーサで測定すると教わりました。

電源ピン(VCCINT、VCCIO)と GND 間の I-V カーブ測定

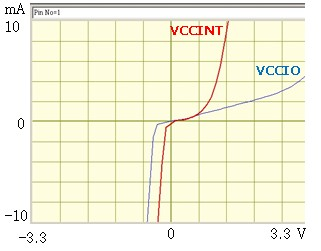

FPGA のコア電源(VCCINT)、I/O 電源(VCCIO)と GND 間の I-V カーブを測定しました (図2)。

最大電流値 10mA に設定し、電圧 -3.3~+3.3V まで走査させたときに流れる電流を測定しました。

良品の FPGA とマス男の FPGA を比較した測定結果です。

図3a、図3b は等しく、マス男の FPGA における電源・GND の I-V 特性は正常でした。

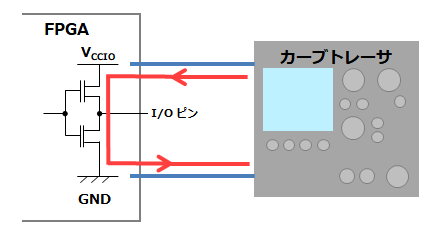

I/O ピンと GND 間の I-V カーブ測定

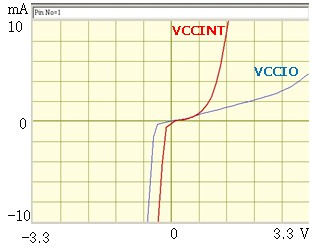

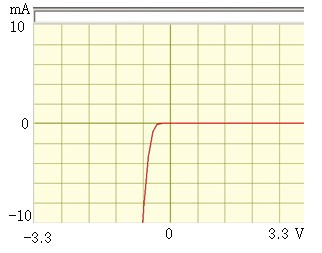

I/O ピン (ピン番号 72) と GND 間の I-V カーブを測定しました (図4)。

電流最大値 10mA に設定し、電圧 -3.3~+3.3V まで走査させたときに流れる電流を測定しました。

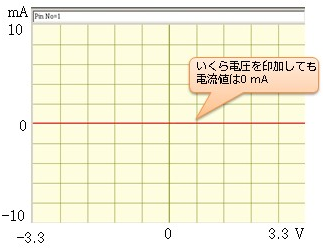

良品の FPGA とマス男の FPGA を比較した測定結果です。

マス男の FPGA の I/O ピン (ピン番号 72) はいくら電圧を印加しても電流が流れず、オープン特性でした。

FPGA パッケージの中身を見る!

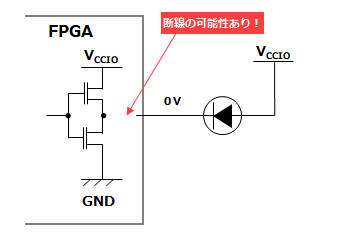

図6 は FPGA パッケージ中身のイメージ図です。

パッケージ中央にシリコン Die があり、シリコン Die と I/O ピン (Lead Frame) はボンディング・ワイヤー (Gold Wires) で結線されています。

図3b. よりシリコン Die は損傷無いことが分かり、図5b. より、おそらく I/O ピン (ピン番号 72) のボンディング・ワイヤーが断線している可能性があります。

よって、Low 出力ではなく、オープンによる 0 V なので LED が点灯しなかったのではないかと、予測できます。

マス男には、このようになってしまったことに心当たりがあります。→ マス男の FPGA 基板製作 1 『絶対最大定格の電圧について』参照

FPGA に最大定格以上の電圧を印加したので、ボンディング・ワイヤーが溶断し、断線させてしまったのではないかと予測されます。

LED に結線する I/O ピン番号を変更した結果、LED を点灯させることができました!

学んだこと

・ FPGA に絶対最大定格以上の電圧を印加したので、ボンディング・ワイヤーが溶断し、シリコン Die と IO ピン間を断線させてしまったのではないかと予測される

・ FPGA の電流電圧特性( オープンやショート )を調べたいときは、カーブトレーサで測定する

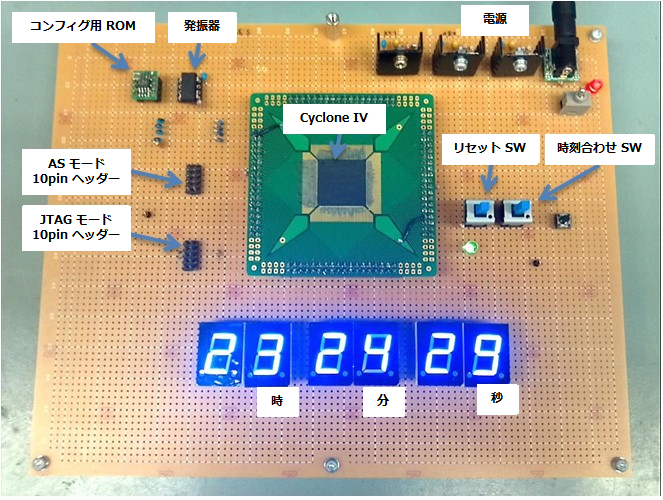

『 Masuo 赤面ボード』完成

様々なトラブルを乗り越え、時計機能付き FPGA ボードを完成することができました。

製作期間は約1ヶ月でした。

名前は『 Masuo 赤面ボード』です。

マス男の FPGA 基板設計シリーズ (全 6話) は、新入社員がはじめて FPGA 基板を設計したときに巻き起こした、様々なトラブルを解決するまでのフローを綴ったコラムです。

本シリーズは、ベテラン先輩社員が教えてくれたノウハウ・アドバイスをまとめたものですので、読者の皆様にもきっと役立つ情報満載です!

この場をかりて、ご指導して頂いた先輩に感謝申し上げます。

赤面ブログは、まだまだ続きます! 現在、新シリーズのコラム執筆進行中! お楽しみに!!