はじめまして、とぷぅと申します。

4 月に入社し、新人ブログを担当することになりました。

どうぞよろしくお願いいたします!!

今回は外部デバイスと FPGA の I/O タイミング関係を定義する方法について述べたいと思います。

研修でタイミング解析*について教わりました。

(※タイミング解析については タイミング解析1『タイミング解析の概念』を参照)

SDC ファイルの記述において入出力の遅延を定義する演習を行いました。

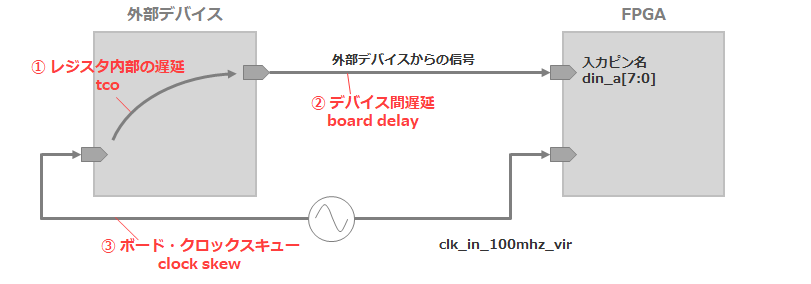

今回の演習では、外部デバイスから送られてくる信号に対する入力ピンのタイミングを定義しました。

clk_in_100 mhz_vir は以下の式で定義しています。

create_clock - name clk_in_100 mhz_vir - period 10.0008 ビットの din_a [7:0] というピンに外部から送られてくる信号の遅延を定義する場合、

入力セットアップ時間と入力ホールド時間の制約をおこないます。

外部デバイスから送られてくるデータの遅延には1,レジスタ内部の遅延、2,ボード上の遅延、3,ボード上のクロックスキューの 3 点があり、

これらを全て考慮した入力遅延を定義する必要があります。

今回の演習の例では、以下の表で定義された遅延時間で制約をおこないます。

|

最小 |

最大 |

|

| レジスタ内部の遅延 tco (ns) |

1 |

3 |

| ボード上の遅延(デバイス間) board delay (ns) |

0.5 |

1 |

| ボード・クロックスキュー clock skew (ns) |

-0.5 |

0.5 |

表 1 . 遅延時間

上記の表を使用して、全ての入力データピンについて、外部からのデータ入力に関する制約を付けます。

その記述方法はこちら

set_input_delay-clock {外部レジスタを駆動するクロック} - max 最大入力遅延[ get_ports {入力ピン名}]

set_input_delay-clock {外部レジスタを駆動するクロック} - min 最小入力遅延[ get_ports {入力ピン名}]この 2 つの値最大入力遅延、最小入力遅延は以下の式で求められます。

最大入力遅延= board delay ( max ) – clock skew ( min ) + tco ( max )

最小入力遅延= board delay ( min ) – clock skew ( max ) + tco ( min )(最大入力遅延がセットアップ、最小入力遅延がホールド時間に関する制約をおこなっております。)

つまり今回の演習の例において、din_a[0] に対しては以下 2 行の記述をします。

set_input_delay -clock {clk_in_100mhz_vir } -max 4.5 [get_ports {din_a[0]}]

set_input_delay -clock {clk_in_100mhz_vir } -min 1 [get_ports {din_a[0]}]これを din_a[0] ~ din_a[7] まですべて記述すると以下のようになります。

set_input_delay -clock {clk_in_100mhz_vir } -max 4.5 [get_ports {din_a[0]}]

set_input_delay -clock {clk_in_100mhz_vir } -min 1 [get_ports {din_a[0]}]

set_input_delay -clock {clk_in_100mhz_vir } -max 4.5 [get_ports {din_a[1]}]

set_input_delay -clock {clk_in_100mhz_vir } -min 1 [get_ports {din_a[1]}]

set_input_delay -clock {clk_in_100mhz_vir } -max 4.5 [get_ports {din_a[2]}]

set_input_delay -clock {clk_in_100mhz_vir } -min 1 [get_ports {din_a[2]}]

set_input_delay -clock {clk_in_100mhz_vir } -max 4.5 [get_ports {din_a[3]}]

set_input_delay -clock {clk_in_100mhz_vir } -min 1 [get_ports {din_a[3]}]

set_input_delay -clock {clk_in_100mhz_vir } -max 4.5 [get_ports {din_a[4]}]

set_input_delay -clock {clk_in_100mhz_vir } -min 1 [get_ports {din_a[4]}]

set_input_delay -clock {clk_in_100mhz_vir } -max 4.5 [get_ports {din_a[5]}]

set_input_delay -clock {clk_in_100mhz_vir } -min 1 [get_ports {din_a[5]}]

set_input_delay -clock {clk_in_100mhz_vir } -max 4.5 [get_ports {din_a[6]}]

set_input_delay -clock {clk_in_100mhz_vir } -min 1 [get_ports {din_a[6]}]

set_input_delay -clock {clk_in_100mhz_vir } -max 4.5 [get_ports {din_a[7]}]

set_input_delay -clock {clk_in_100mhz_vir } -min 1 [get_ports {din_a[7]}]これで外部信号からの入力ピンの制約はバッチリです!!

しかし、上記を din_a ピンのみならず、他の全ピンに制約を与えるとしたら、少しめんどくさい&スマートな記述ではない。

(ほとんど同じ内容を 16 行も書いているので・・・・)

もっときれいにちゃちゃっと記述する方法はないかと思っていたところ、

講師を担当してくれた先輩は 2 行で済む方法があるよ!と教えてくれました。

それがこちら。

set_input_delay -clock {clk_in_100mhz_vir } -max 4.5 [get_ports {din_a*}]

set_input_delay -clock {clk_in_100mhz_vir } -min 1 [get_ports {din_a*}]a の後に * (アスタリスク) をつけることで、 din_a 以下の記述が何であっても、同じ記述をすることができます。

つまり、先ほどの 16 行を 2 行で書けてしまいます。

この「*」のことをワイルドカードと呼び、手間をかけず、 SDC ファイルを記述することができます。

ワイルドカードは情報処理( Linux、C言語など)でよく用いられているものらしいです。

(私はワイルドカードを知らなかったので、研修で知った時感動しました 笑)

このワイルドカードは SDC ファイルでも使えるので、利用しない手はないですね!

まとめ

・入力ピンの設定には 3 つの遅延の要素があり、その全てを考慮した記述をしなければならない。

・ワイルドカードを用いると複数行に渡る記述を減らすことができる。→記述がすっきりする+時間短縮