みなさん、こんにちは、もつです。

今、研修で FPGA を用いた時計を製作しています。

デザインは Verilog HDL と VHDL の両方で作成しました。

まずはじめに、 Verilog HDL で完成させました。

VHDL は大変だろうなと思っていましたが、先輩から「Verilog でできているなら、ちょっと変えるだけだよ!」と言われ、

「すぐできるのか!」と安心しました。

しかし実際にやってみると、案の定エラーだらけ…

「そんな簡単にはいかないよな」と思い、一つずつ見直していくことに。

よく見てみると、勘違いしていたところが多々ありました。

そこで今回は、私が研修で勘違いしていた Verilog HDL と VHDL の文法的な違いのうち、これらをご紹介します。

クロックでの立ち上がり処理

Verilog では、クロックの立ち上がりで処理をおこなう場合、

always @ (posedge clk)

と書いていましたが、

VHDL では、

process ( clk )begin

if ( clk ‘event and clk = ’1’ ) then

と書かないといけない!

しばらく Verilog HDL ばかり書いていたのですっかり忘れており、センシビティーリストに書くだけで良いのかと思っていました。(笑)

複数行書いても、begin...end がいらない!?

例えば、Verilog HDL では、ステートメント記述が2行以上になる時は、begin...end が必要 でしたが、

VHDL では書き方が異なります。

process 文の後には begin...end をつけますが、if 文の後ろには then が必要で

その if ステートメントが終了する場合には、end if が必要 です!

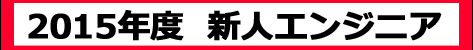

コメントアウトの仕方が違う!?

Verilog HDL では、コメントアウトは「//」(ダブルスラッシュ)、複数行の時は「/* ... */」でしたが、

VHDL 1993 のコメントアウトは「--」(ダブルハイフン) で、複数行をコメントアウトするときはすべての行の先頭にダブルハイフンを付けなければなりません。

ちょっと面倒だな~ と思ったのですが、簡単な方法がありました!!

Quartus II のテキスト・エディターのツール・バーにある Toggle Comment ボタン(下図赤丸)をクリックすると、選択された行すべてが一括でコメントアウトできるんです。

しかも、あとで先輩に教えてもらったのですが

VHDL-2008 では、Verilog HDL の /* … */ でコメントアウトができるようになったんだそうです。

論理演算子に記号が使えない!?

論理演算子を記述するとき、

Verilog HDL では "記号" で書きますが、VHDL では下表のとおり記号が使用できません。

|

論理演算子 |

Verilog HDL |

VHDL |

|

論理否定 |

! |

not |

|

論理積 |

&& |

and |

|

論理和 |

|| |

or |

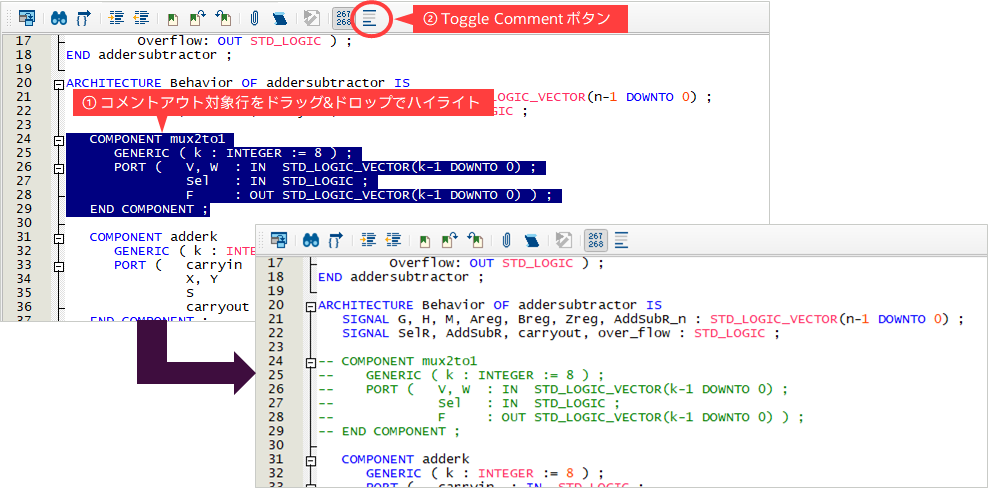

If 文中での数字の表現について

Verilog HDL では、例えば、4 ビットの 9 を 10 進数で表現するには、4’d9 のように表記していました。

しかし、

「VHDL では、このような表記の仕方はなかったような…」と思い込んでしまい、すべて 2 進数で書いていました。

ですが、良く調べると、10 進数で書く方法がありました!

VHDL で 2 進数で 4 ビットの 9 を表記する場合は、"1001" と書きますが、

これを 9 とそのまま書けば良いのです!ダブルクオート("")で囲む必要もないです!

ただしこれは、if 文の中の条件判定の場合のみです(下図)。

値の代入の際などに使ってしまうと、integer タイプと認識され、エラーとなるので注意が必要です。

以上が、私が研修で時計を作っている際につまずいた点です。

6 月の研修で、Verilog HDL も VHDL も少し学んだのですが、いざイチからやってみると、勘違いしているところ、忘れていたところが多々ありました。

皆様も、ぜひ参考にしてみてください。