このコラムでは「意外と知られていないけど、知っていると差がつく FPGA の技術情報」をご紹介します。

FPGA初心者の方からベテランの方まで、幅広くご活用いただける内容ですので、ぜひ最後までお付き合いください。

【第 3 回】 これってリークパワー? いいえ、DC パワーです。

リークパワーが大きいと言われる回路を確認すると、原因は DC パワーであるケースが多くあります。

DC パワーを考慮して回路設計すると待機時の省電力化に役立ちますので、今回は DC パワーについて説明します。

CMOS 回路は低消費電力プロセス

CMOS 回路は、動作時以外は pMOS か nMOS のどちらかが閉じて、Vdd から GND へ流れる DC 電流が無いので消費電力の低いプロセスと言われています。

ところが、CMOS 回路でもプルアップやプルダウンを行うと DC 電流が流れます。これが DC パワーです。

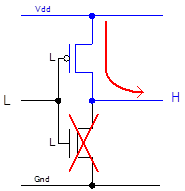

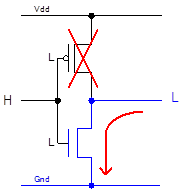

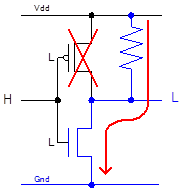

例えば、図3.のプルアップ付出力バッファは Vdd 側に Pull-up 抵抗が付いていますね。

“H” を入力すると、上のトランジスタが “OFF”、下のトランジスタが “ON” になり、出力ピンと GND が繋がります。

上のトランジスタは OFF になっていますが、並列した Pull-up 抵抗があるので、図3 の赤い矢印に沿って Vdd ⇒ Pull-up 抵抗 ⇒ Gnd へと DC 電流が流れます。

DC パワーは、Pull-up 抵抗1つだけで “V2/R” の電力を消費し、抵抗値を小さくすると消費電力は増加します。

同じように、プルダウンは出力ピンと GND の間に抵抗があるので、出力が “H” の時に DC パワーを消費します。

よって、“H” 状態が長い時はプルアップ、“L” 状態が長い時はプルダウンにしたり、 抵抗値を大きくすることで待機時の消費電力を削減できます。

リークパワーが大きいデザインを見ると、ピン処理に気を使わずに無駄にDCパワーを消費しているケースがありますのでご注意ください。

リークパワーを疑う前に、まずはDCパワーを確認してくださいね。