このコラムでは「意外と知られていないけど、知っていると差がつく FPGA の技術情報」をご紹介します。

FPGA初心者の方からベテランの方まで、幅広くご活用いただける内容ですので、ぜひ最後までお付き合いください。

【第 2 回】 クロック・ゲーティング(ゲーテッド・クロック)は効果ある?

クロック・ゲーティング(以降 CG と表記します)とは、データの変化がないレジスタのクロックを止めて、クロックネットワークの消費電力と、

それに繋がったレジスタとゲートの消費電力を削減する手法です。

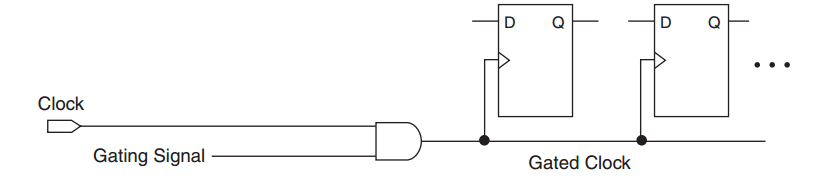

図1のように、クロック内に AND 等のゲートを入れてクロックを止めます。

設計者の方から「FPGA でも CG を使用できますか?」とよく聞かれます。

回答としては、FPGA でも CG を使えます。

しかし、図1.のようにクロックネットワークに AND などを入れてクロックを止める事はお勧めできません。

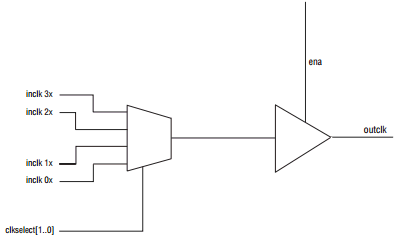

クロックを止める時は、インテルの CG 専用ブロック “ALTCLKCTRL” を使用してください。

実は、ASIC でも、ユーザ回路での CG は禁止です、クロックと同期する CG 専用セルを使っています。

CG 専用セルを使わないと、図1.の “Gating Signal” の信号とクロックのタイミングでグリッジが乗る可能性があるのと、

AND と後段のレジスタ間のスキューを保障できないためです。

それ以前に、クロックラインにゲートを入れた時点で非同期回路になるので、多くの EDA ツールが対応できません。

CG 専用セルを使うことで EDA ツールは CG 専用回路をデータイネーブル回路に置き換えて認識することで同期回路として処理できます。

CG を行う方法には大きく2つあります。

(1)ツールが自動で CG する方法

(2)設計者が意図的にクロックを止める方法

ツールが自動で CG する方法

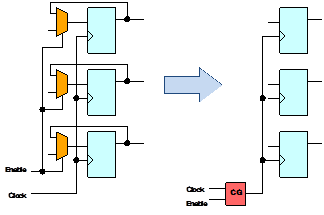

イネーブルとクロックを共有する複数の F/F がある場合に、F/F がディセーブルの時にクロックを止めます。

データ遷移が無い時に F/F が動作しないのと、MUX を含めたクロックの消費電力を削減できます。

CG 専用回路をできるだけクロックの根本近くに配置すると、クロックツリーの消費電力も削減されます。

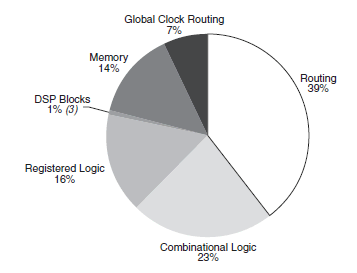

ASIC では、全消費電力の中でクロック電力が占める割合が高いので、自動で CG を行っても効果はありますが、

構造が異なる FPGA ではクロック電力が占める割合が数%と少ないので、あまり効果はありませ

設計者が意図的にクロックを止める方法

動作が不要な回路のクロックを止める方法です。

FPGA は全消費電力の中で I/O と配線部分の電力が大きいので、(1)よりも手間は掛かりますが効果は高い方法です。

ただし、どこでクロックを止めたら良いのかをツールが判断できませんので、設計者が意図的にブロックのクロックを止める必要があります。

クロックラインに入れる回路は、インテルが提供している CG 専用ブロック “ALTCLKCTRL” を使ってください。

以下URLをクリックすると “ALTCLKCTRL” 資料 (PDF) が自動ダウンロードできます。

Clock Control Block (ALTCLKCTRL) IP Core User Guide