回路規模が大きなFPGAを使用する際は、FPGAが電源に要求する電流量が増えます。

その結果、電源の入力ラインに流れるRMS電流が増加します。

入力のRMS電流が増加すると?

DC/DCコンバータの入力部に流れるRMS電流が増加すると、入力部のスイッチングノイズが大きくなります。

入力のRMS電流について、今まで気にしたことが無いかもしれません。しかし、今後FPGAで使用する電流値が増えた場合には、確認・検討することが必要になります。

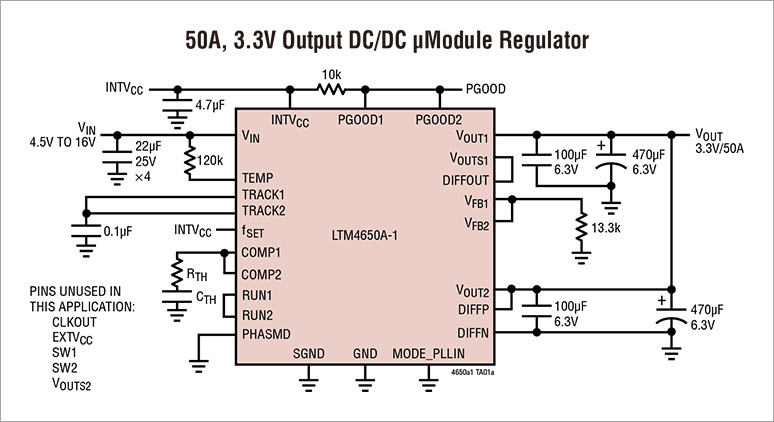

ここでは、図1のLTM4650A-1というDC/DCコンバータを用いて考えてみたいと思います。

LTM4650A-1は、25A出力のDC/DCコンバータが2つ入っている製品です。

2チャンネルのDC/DCの出力をまとめてシングル接続とすることで50A出力することが可能です。

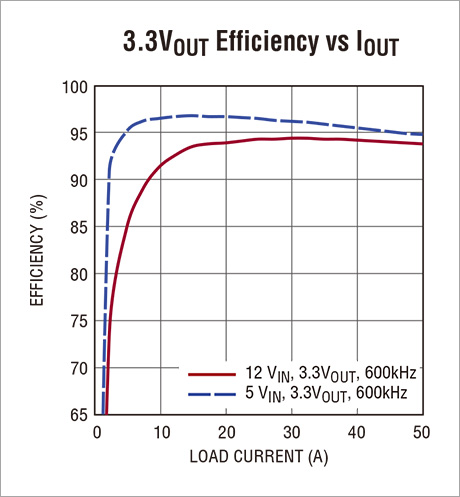

50(A)でも約95%の高効率を実現しています(図2)。

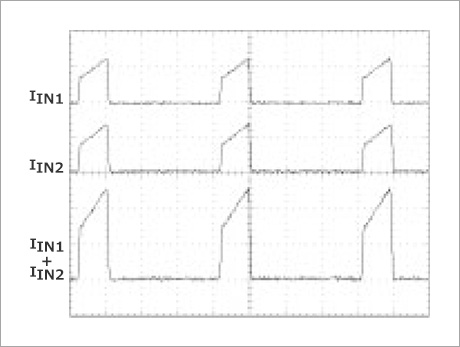

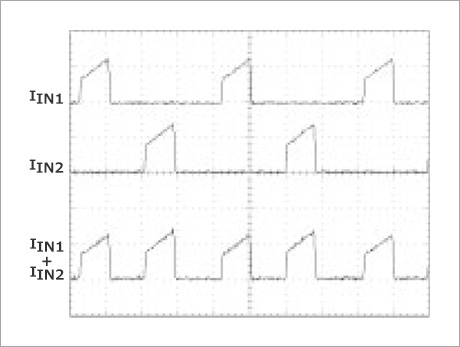

一般的に、シングル出力の場合の入力のRMS電流は 図5 のような形になります。

デュアルの入力電流IIN 1とIIN 2が加算された大きなRMS電流となります。

大きなRMS電流は、スイッチングノイズとしてあらわれます。

このRMS電流によるノイズが原因で、システムの誤動作を引き起こすこともあります。

下記式よりRMS電流を計算してみます。

条件は、入力12V、出力1.0V、最大電流50Aとすると、効率は図1から約87%とします。

計算すると、RMS電流値は約16Aとなります。

η%:電源モジュールの推定効率

D:降圧コンバータのデューティ・サイクル

D = VOUT / VIN

ノイズ源となるRMS電流を抑えるツー・フェーズ動作

ツー・フェーズとは、LTM4650-1に内蔵されているスイッチング・レギュレータ1と2のスイッチングのタイミングを180°位相(フェーズ)を変える動作になります。

図4のような形で、レギュレータ1の入力電流IIN 1とレギュレータ2の入力電流IIN 2の位相が180°ずれることにより、周波数は2倍になりますが、入力電流の最大値がシングル・フェーズ動作の時の半分になります。

これにより、入力ラインに発生するスイッチングノイズが低減され、シングル・フェーズと比較しEMI対策が安易になったりノイズによるシステムトラブル発生の影響が軽減されます。

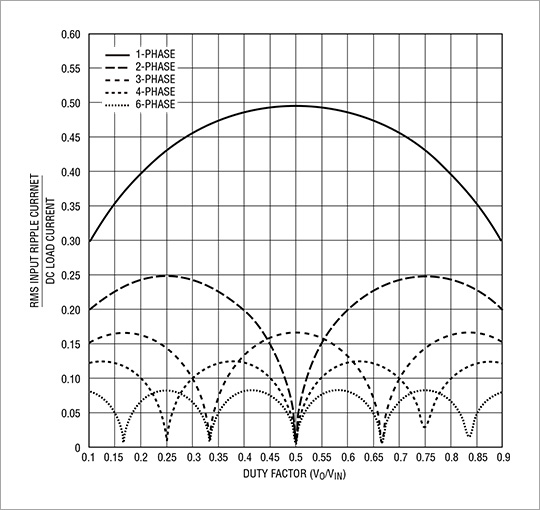

図5の正規化された入力RMS電流のグラフからツー・フェーズ時のRMS電流を見積もります。Dutyを約0.1とするとRMS/Maximum Currentの割合は0.2となります。

結果、ツー・フェーズ時のRMS電流は約10Aとなり、シングルフェーズ時の16Aより大きく減少します。

これにより、入力ラインに現れるスイッチング・ノイズが大幅に低減されます。

入力セラミック・コンデンサの削減

RMS電流が減ることで、入力ラインのスイッチング・ノイズを減らすことができる以外に、もう1つメリットがあります。

セラミック・コンデンサを削減できることです。

一般的に、セラミック・コンデンサの自己発熱量は20℃以下に抑える必要があります。

そのため、RMS電流値が大きくなると自己発熱が大きくなるため、コンデンサの数を増やして自己発熱を分散させる必要が出てきます。

自己発熱20℃になるRMS電流値が4.2Aのセラミック・コンデンサを使用していたと仮定します。

その場合、シングルとデュアル・フェーズ動作時のセラミック・コンデンサの必要数は次の通りです。

- シングル・フェーズ:4個(16A ÷ 4.2A = 3.81)

- ツー・フェーズ:3個 (10A ÷ 4.2A = 2.38)

FPGAボード上には、非常に多くのセラミック・コンデンサが搭載されているため、1個でも減らせることは実装コストや管理費コストを削減する上でも製造上のメリットになります。