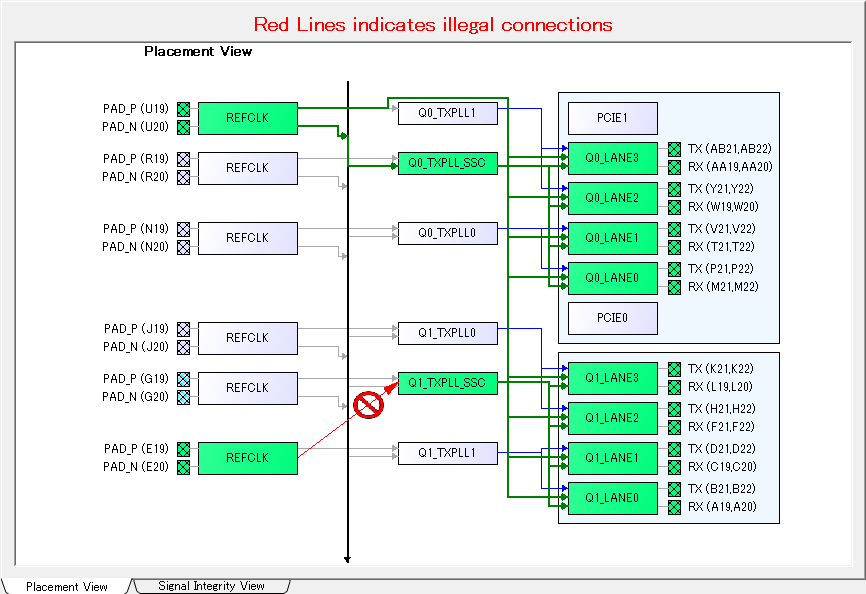

Microchip FPGA: REFCLK の配置制約規則について。Libero SoC のI/O Editor => XCVR ViewタブのGUIを使用した場合、最上段にあるREFCLKを使用すると全てのTXPLL及びLane_Quadにクロックが供給できる。 REFCLKの配置に依存して接続できないlane quadがあります。この制約条件について正確な情報を教えてください。

Libero SoC

PolarFire

クロック/CCC

トランシーバー

特定のREFCLKより下にのみ(Cascade to Lower)接続可能で、上側には接続できません。

詳細は、UG0677 : PolarFire FPGA Transceiver User Guide

https://www.microsemi.com/document-portal/doc_download/136531-ug0677-polarfire-fpga-transceiver-user-guide

3.5.4.1 Transceiver Reference Clock Interface の図に記載されたCascade to Lower の制限をご確認ください。