Intel: What is the purpose and range of values for the boot_scratch_cold0 to boot_scratch_cold8 registers in the System Manager group in the Intel® Stratix® 10 Hard Processor System Address Map and Register Definitions?

Category: SoC FPGA

tool:-

Device: Stratix® 10, Agilex™

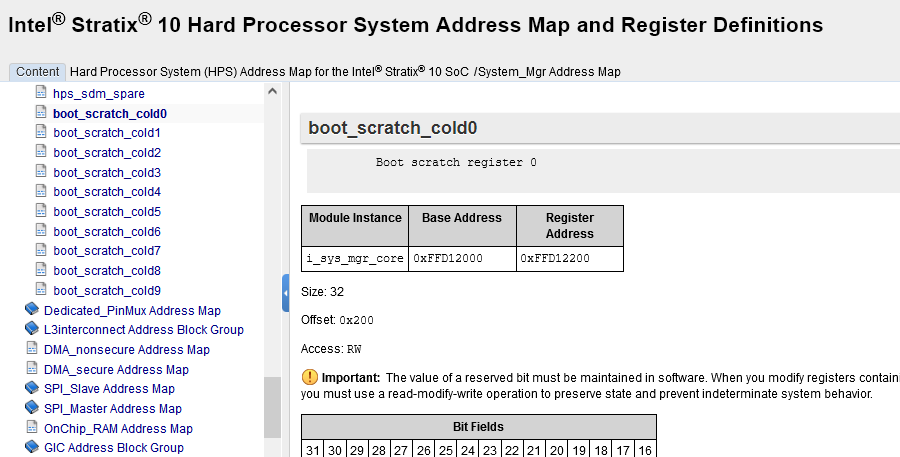

(From Intel® Stratix® 10 Hard Processor System Address Map and Register Definitions)

boot_scrach_cold0 to 8 are registers prepared for passing various setting values between software involved in the boot flow of the Hard Processor System (HPS).

Since both writing and reading depend on the software implementation, there are no restrictions on the range of values as a register specification.

Examples of software involved in boot flow:

* FSBL (SPL)

* SSBL (U-Boot)

* Arm-Trusted-Firmware

* Linux Kernel

See the following information posted on rocketboards.org for practical applications.

Appendix: Boot Scratch Register Usage (from Building Bootloader for Stratix 10 and Agilex)

This content is a common specification with Intel® Agilex™ FPGA.

![]() Experienced FAE

Experienced FAE

Free consultation is available.

From specific product specifications to parts selection, the Company FAE will answer your technical concerns free of charge. Please feel free to contact us.