Sony's next-generation CMOS image sensor interface realized with FPGA

Overview

SLVS-EC Rx IP is an IP for realizing SLVS-EC reception in Intel® FPGA. SLVS-EC is a high-speed serial interface standard for high-resolution CMOS image sensors proposed by Sony.

This standard employs an Embedded Clock that embeds a clock in pixel data, enabling board design without being aware of the skew that occurs between lanes. Therefore, it is advantageous for high-speed and long-distance transmission.

Features

- Compatible with SLVS-EC Specification Version 1.2/2.0

- Implements various functions defined by SLVS-EC Link layer (Physical layer is implemented by Intel® PCS/PMA)

- Supports Byte to Pixel conversion in various lane configurations

- Includes header parsing and payload error detection

specification

| function | Specifications |

| Number of Lanes | 1、2、4、6、8 |

| Baud Grade | 1、2、3※ |

| Bit per pixel | 8、10、12、14、16 |

| CRC | Limited* |

| ECC | Option 1 |

| Embedded data | Supported |

| Dynamic Mode Change | Supported |

| Multiple streams | If needed |

* Baud Grade 3 is supported only for 10 series or later

* CRC may not satisfy the operating frequency depending on the speed grade and number of lanes of the FPGA used.

* Please contact our sales department for unsupported IP functions and restrictions.

corresponding device

- Cyclone® V-GX

- Cyclone® 10GX

- Arria® 10 GX

- Stratix® 10 (L-Tile/H-Tile)

(*Please contact our sales department for the compatibility status of other devices.)

Offerings

- Cryptographic RTL (Verilog HDL)

- Reference design

- Simulation environment (for Modelsim)

- User's Manual, Reference Manual, Simulation Manual

logic resource

It becomes a circuit configuration including Transceiver with 8 lane configuration.

| Items | Cyclone® V-GX | Arria® 10 GX | ||

| w/o ECC | w/ECC | w/o ECC | w/ECC | |

| ALMs | 4711 | 8242 | 3930 | 7555 |

| Total Registers | 4328 | 6664 | 3778 | 6079 |

| Total block memory bits | 4096 | 13312 | 2560 | 11776 |

* The above value is an approximate value of the circuit scale with the total of 8Lane Full Configurable and IP + Transceiver. It may vary depending on the customer's system configuration.

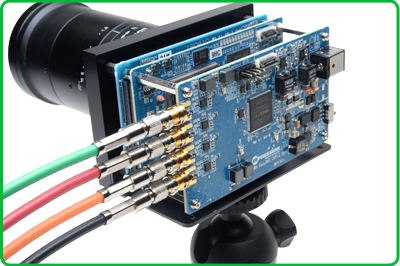

Evaluation/demo environment

This IP can be evaluated and demonstrated using our EasyMVC Machine Vision Camera Development Kit.